基于IMX214+ZYNQ XC7Z100的1080P双目视觉智能平台

描述

一、双目视觉智能平台概述

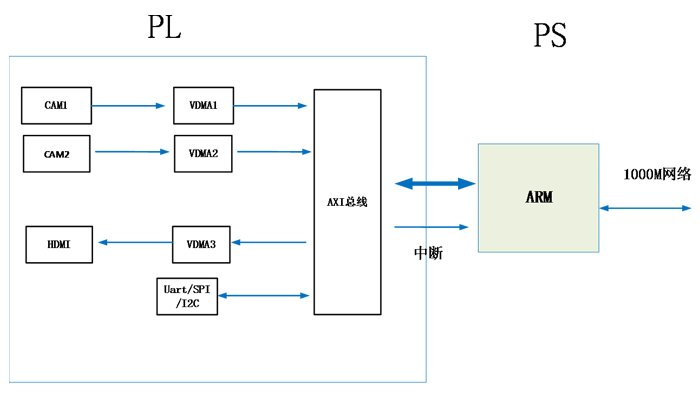

双目视觉智能平台以双路CMOS传感器IMX214+ XC7Z100 FPGA为基础,支持双路1080P 60fs视频输入, ZYNQ FPGA 支持FPGA预处理和双ARM计算。软件支持双目摄像头采集及QT图像显示,ARM接口管理及丰富的图像处理软件。

二、硬件资源1 FMC 双目MIPI模块FL0214

FMC 双目MIPI模块FL0214为MIPI接口的2路1300万像素的CMOS摄像头模块。 FL0214模块带有2个MIPI接口的摄像头模组,摄像头模组采用的是索尼(SONY)公司的CMOS感光芯片IMX214,摄像头 高分别率为4224(水平)x3120(垂直)。摄像头的MIPI信号通过MC20901芯片转换为LVDS信号到FMC接口供FPGA采样。

高分别率为4224(水平)x3120(垂直)。摄像头的MIPI信号通过MC20901芯片转换为LVDS信号到FMC接口供FPGA采样。

模块有一个标准的LPC的FMC接口,用于连接FPGA开发板, FMC的连接器型号为:ASP_134604_01

2.1 FL0214模块的参数说明

以下为FL0214 双目MIPI摄像头模块的详细参数:

CMOS感光芯片:SONY IMX214

输出分别率:13Mega-Pixel (4208 × 3120)@30fps,4K2K@30fps, 1080p@60帧;

图像输出格式:RAW10/8, COMP8/6;

调焦距离:10CM ~ 无穷大

调焦方式: 电机马达自动调焦;

可视角度:80.7° ± 3° (Diag)

摄像头输出:CSI-2串行数据输出(MIPI 4 Lane, 兼容D-PHY标准V1.1)

摄像头配置接口:I2C;

MC20901驱动芯片:电平转换(MIPI D-PHY->LVDS):

工作温度:-20°~65°;

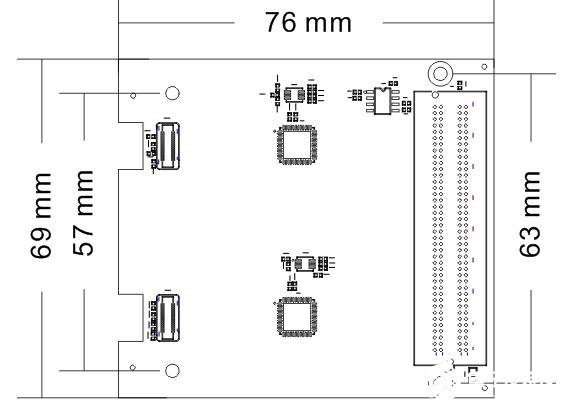

2.2 FL0214模块的结构图

FL0214 双目MIPI摄像头尺寸结构图

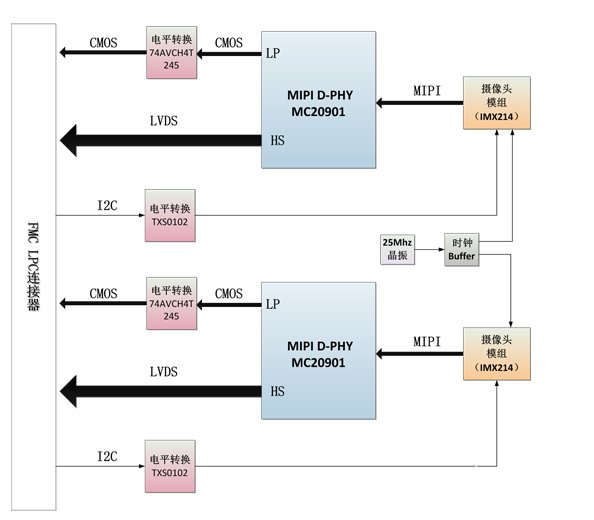

2.3 FL0214模块原理框图

FL0214模块的原理设计框图如下:

关于IMX214摄像头和MIPI D-PHY芯片的电路具体参考设计请参考摄像头的资料和芯片手册。

2.4模块FMC LPC的引脚分配:

下面只列了电源和接口的信号,GND的信号没有列出,具体用户可以参考原理图。

| Pin Number | Signal Name | Description |

| C35 | +12V | 12V电源输入 |

| C37 | +12V | 12V电源输入 |

| D32 | +3.3V | 3.3V电源输入 |

| C34 | GA0 | EEPROM地址位0位 |

| D35 | GA1 | EEPROM地址位1位 |

| D9 | CSI1_CMOS_LP_CLK_N | 第一路摄像头CMOS时钟负极输出 |

| D8 | CSI1_CMOS_LP_CLK_P | 第一路摄像头CMOS时钟正极输出 |

| G16 | CSI1_CMOS_LP0_N | 第一路摄像头CMOS LANE0数据负极输出 |

| G15 | CSI1_CMOS_LP0_P | 第一路摄像头CMOSLANE0数据正极输出 |

| G13 | CSI1_CMOS_LP1_N | 第一路摄像头CMOS LANE1数据负极输出 |

| G12 | CSI1_CMOS_LP1_P | 第一路摄像头CMOSLANE1数据正极输出 |

| G19 | CSI1_CMOS_LP2_N | 第一路摄像头CMOS LANE2数据负极输出 |

| G18 | CSI1_CMOS_LP2_P | 第一路摄像头CMOSLANE2数据正极输出 |

| G10 | CSI1_CMOS_LP3_N | 第一路摄像头CMOS LANE3数据负极输出 |

| G9 | CSI1_CMOS_LP3_P | 第一路摄像头CMOSLANE3数据正极输出 |

| G7 | CSI1_LVDS_CLK_N | 第一路摄像头LVDS时钟负极输出 |

| G6 | CSI1_LVDS_CLK_P | 第一路摄像头LVDS时钟正极输出 |

| H14 | CSI1_LVDS_HS0_N | 第一路摄像头LVDS LANE0数据负极输出 |

| H13 | CSI1_LVDS_HS0_P | 第一路摄像头LVDS LANE0数据正极输出 |

| H11 | CSI1_LVDS_HS1_N | 第一路摄像头LVDS LANE1数据负极输出 |

| H10 | CSI1_LVDS_HS1_P | 第一路摄像头LVDS LANE1数据正极输出 |

| H17 | CSI1_LVDS_HS2_N | 第一路摄像头LVDS LANE2数据负极输出 |

| H16 | CSI1_LVDS_HS2_P | 第一路摄像头LVDS LANE2数据正极输出 |

| H8 | CSI1_LVDS_HS3_N | 第一路摄像头LVDS LANE3数据负极输出 |

| H7 | CSI1_LVDS_HS3_P | 第一路摄像头LVDS LANE3数据正极输出 |

| G21 | CSI1_OTP_B | 第一路摄像头编程接口 |

| D26 | CSI1_RST_N | 第一路摄像头复位信号输入 |

| D21 | CSI2_CMOS_LP_CLK_N | 第二路摄像头CMOS时钟负极输出 |

| D20 | CSI2_CMOS_LP_CLK_P | 第二路摄像头CMOS时钟正极输出 |

| G34 | CSI2_CMOS_LP0_N | 第二路摄像头CMOS LANE0数据负极输出 |

| G33 | CSI2_CMOS_LP0_P | 第二路摄像头CMOSLANE0数据正极输出 |

| G28 | CSI2_CMOS_LP1_N | 第二路摄像头CMOS LANE1数据负极输出 |

| G27 | CSI2_CMOS_LP1_P | 第二路摄像头CMOSLANE1数据正极输出 |

| G37 | CSI2_CMOS_LP2_N | 第二路摄像头CMOS LANE2数据负极输出 |

| G36 | CSI2_CMOS_LP2_P | 第二路摄像头CMOSLANE2数据正极输出 |

| G25 | CSI2_CMOS_LP3_N | 第二路摄像头CMOS LANE3数据负极输出 |

| G24 | CSI2_CMOS_LP3_P | 第二路摄像头CMOSLANE3数据正极输出 |

| C23 | CSI2_LVDS_CLK_N | 第二路摄像头LVDS时钟负极输出 |

| C22 | CSI2_LVDS_CLK_P | 第二路摄像头LVDS时钟正极输出 |

| H29 | CSI2_LVDS_HS0_N | 第二路摄像头LVDS LANE0数据负极输出 |

| H28 | CSI2_LVDS_HS0_P | 第二路摄像头LVDS LANE0数据正极输出 |

| H26 | CSI2_LVDS_HS1_N | 第二路摄像头LVDS LANE1数据负极输出 |

| H25 | CSI2_LVDS_HS1_P | 第二路摄像头LVDS LANE1数据正极输出 |

| H32 | CSI2_LVDS_HS2_N | 第二路摄像头LVDS LANE2数据负极输出 |

| H31 | CSI2_LVDS_HS2_P | 第二路摄像头LVDS LANE2数据正极输出 |

| H23 | CSI2_LVDS_HS3_N | 第二路摄像头LVDS LANE3数据负极输出 |

| H22 | CSI2_LVDS_HS3_P | 第二路摄像头LVDS LANE3数据正极输出 |

| C27 | CSI2_OTP_B | 第二路摄像头编程接口 |

| D27 | CSI2_RST_N | 第一路摄像头复位信号输入 |

| D14 | FMC_CSI1_SCL | 第一路摄像头IIC总线时钟 |

| D15 | FMC_CSI1_SDA | 第二路摄像头IIC总线数据 |

| H37 | FMC_CSI2_SCL | 第二路摄像头IIC总线时钟 |

| H38 | FMC_CSI2_SDA | 第二路摄像头IIC总线数据 |

| C34 | GA0 | EEPROM的I2C地址0 |

| D35 | GA1 | EEPROM的I2C地址1 |

| C30 | SCL | EEPROM的I2C时钟 |

| C31 | SDA | EEPROM的I2C数据 |

| G39 | VADJ | VADJ电源输入 |

| H40 | VADJ | VADJ电源输入 |

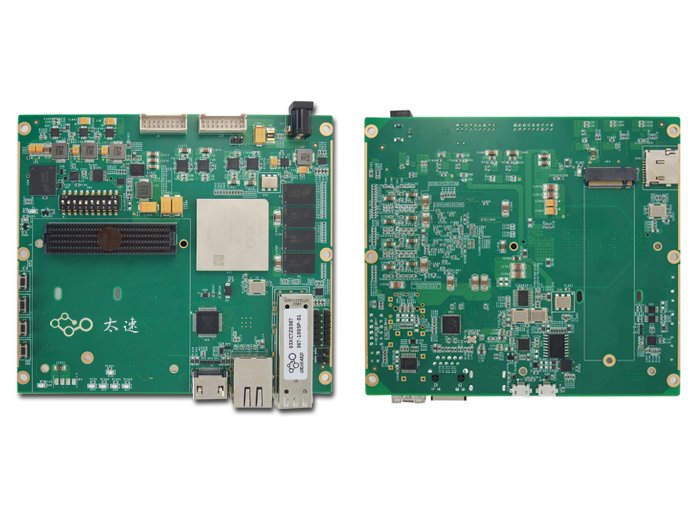

三、 硬件资源2-基于XC7Z100 的图像处理底板

1.1主要性能和优势

使用 Zynq-7000 SoC 对嵌入式应用进行快速原型设计以实现优化

硬件、设计工具、 IP、以及预验证参考设计

演示嵌入式设计,面向视频通道

存储接口

1GB DDR3 组件存储

1GB DDR3 SODIM 存储器

支持包含 Dual ARM Cortex-A9 核处理器的嵌入式处理

使用 10-100-1000 Mbps Ethernet (RGMII) 开发网络应用

使用 HDMI 输出实现视频显示应用

扩展 I/O, 包含 FPGA Mezzanine Card (FMC) 接口

四、 软件资源

软件支持:

支持从microSD 卡加载ubuntu系统

支持利用QSPI模式配置程序

支持RS232连接计算机串口通信

支持外接HDMI连接显示器,并支持键盘,鼠标等外接设备进行演示

支持Msata存储设备,支持高速数据存储功能 (SATA存储单独定制开发)

平台引入了Xilinx公司的SDSoC™ 开发工具,提供了嵌入式C/C++ 应用开发体验,包括了Eclipse IDE和完整的设计环境,支持Zynq® All Programmable SoC开发,同时集成了Vivado设计环境。

FMC上接高速ADC,DAC子卡,CameraLink子卡等,进行功能扩展以及客户的定制需求,并可提供演示程序

五、 双目视觉案例

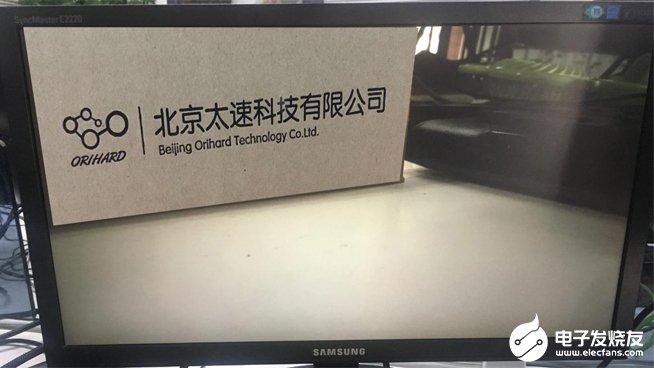

在VIVADO软件开发环境里下载双目测试例程到开发板,我们可以通过开发板的HDMI输出接口显示双目的视频图像到HDMI显示器上,

单个视频显示效果如下:

双目视觉显示效果:

审核编辑:黄飞

-

双目视觉在智能驾驶领域的应用2025-07-09 1462

-

基于Xilinx Zynq-7000系列XC7Z045/XC7Z100 SoC处理器设计2022-10-19 5661

-

Xilinx Zynq-7000SOC的相关资料推荐2022-01-03 2371

-

Xilinx Zynq-7000特性参数2021-12-30 1627

-

基于IMX214+ZYNQ XC7Z100的1080P双目视觉智能平台2021-01-01 1627

-

基于ZYNQ的机器视觉应用2020-09-16 2266

-

【MPS电源评估板试用申请】XC7Z100的PMBus供电系统设计2020-06-18 1214

-

zynq XC7Z100板卡学习资料:基于zynq XC7Z100 FMC接口通用计算平台2020-03-24 4673

-

LabVIEW双目视觉 【转载】2020-03-02 9217

-

367-基于ZYNQ XC7Z100 FFG 900的高性能计算模块解决方案2018-12-19 5193

-

钜芯发布业内首颗智能双目视觉芯片2017-10-26 11337

-

米家智能摄像机1080P多少钱?米家智能摄像机1080P评测2017-04-27 3303

-

基于SoC的双目视觉ADAS解决方案2016-11-05 3717

-

【WRTnode2R申请】双目视觉随动平台2015-09-10 2526

全部0条评论

快来发表一下你的评论吧 !