FPGA中时钟的用法

描述

生成时钟包括自动生成时钟(又称为自动衍生时钟)和用户生成时钟。自动生成时钟通常由PLL或MMCM生成,也可以由具有分频功能的时钟缓冲器生成如7系列FPGA中的BUFR、UltraScale系列FPGA中的BUFGCE_DIV/BUFG_GT以及Versal中的MBUFG/BUFG_GT等。对于这类时钟,Vivado会自动创建时钟,并不需要用户手工通过create_generated_clock创建。

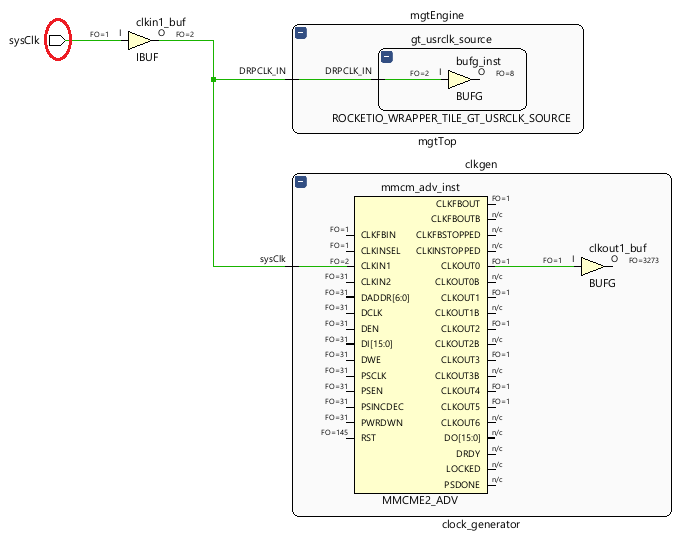

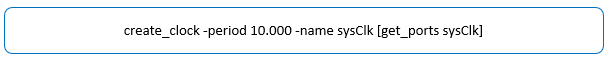

案例1:单端时钟

这是比较典型的场景,如下图所示:时钟由全局时钟管脚进入经IBUF驱动MMCM以及BUFG。此时只用在输入时钟管脚处(图中红色椭圆标记)创建时钟即可,MMCM生成时钟如图中端口CLKOUT0,Vivado会自动创建。注意主时钟的位置在sysClk对应的全局时钟管脚处,不是MMCM的输出端口,也不是BUFG的输出端口。

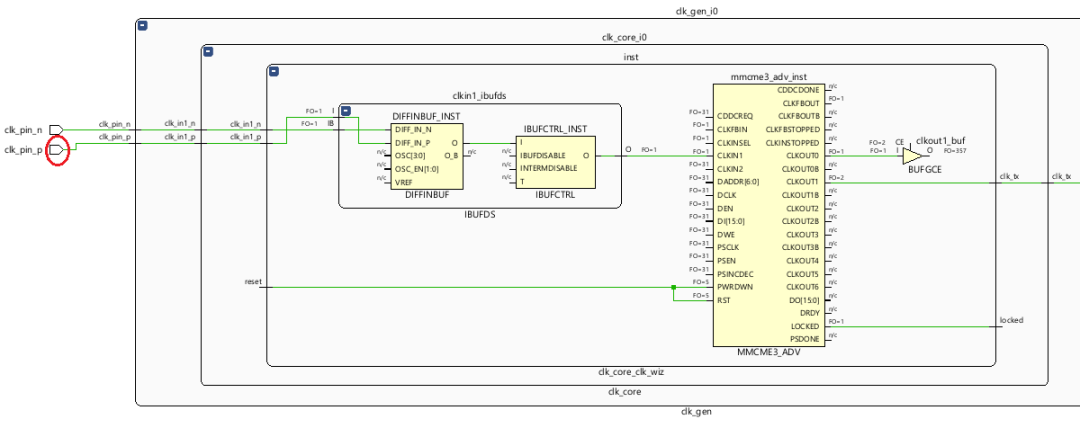

案例2:差分时钟

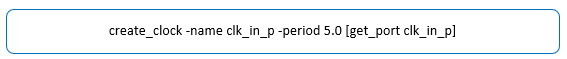

如下图所示,差分时钟转单端驱动MMCM,这里主时钟为clk_pin_p(图中红色方框所示),因此只用对该端口施加create_clock命令。

使用create_clock时,对于差分时钟,施加对象为差分的P端而不是N端,同时只用对P端使用该命令,如下图所示。

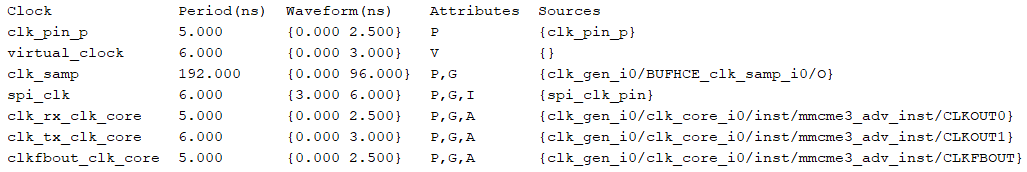

有了上述约束,工具就会自动推断出MMCM生成时钟,这可通过report_clocks命令查看并验证,如下图所示(需要打开综合后的网表)。

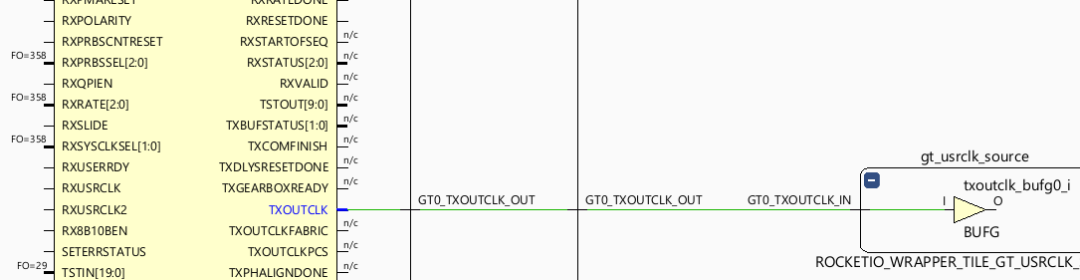

案例3:7系列FPGA中高速收发器的TXOUTCLK/RXOUTCLK

如下图所示,7系列FPGA中高速收发器的TXOUTCLK,输出端口接BUFG。这时要在TXOUTCLK处施加命令create_clock,因此,要用get_pins而不是get_ports。

审核编辑:汤梓红

-

FPGA的时钟电路结构原理2024-04-25 3566

-

怎么使用AD9946中DCO时钟?2023-12-20 589

-

FPGA架构中的全局时钟资源介绍2021-03-22 15371

-

FPGA中时钟速率和多时钟设计案例分析2020-11-23 4906

-

时钟在FPGA设计中能起到什么作用2019-09-20 6159

-

关于FPGA中跨时钟域的问题分析2019-08-19 4083

-

请问AD9946中DCO时钟的用法是?2018-10-10 3599

-

请问AD9684中DCO时钟的用法2018-08-15 5264

-

低功耗时钟门控算术逻辑单元在不同FPGA中的时钟能量分析2015-11-19 684

-

DLL在_FPGA时钟设计中的应用2015-10-28 960

-

FPGA异步时钟设计中的同步策略2011-12-20 1079

-

基于FPGA的时钟设计2011-09-21 4265

-

大型设计中FPGA的多时钟设计策略2009-12-27 869

-

影响FPGA设计中时钟因素的探讨2009-11-01 552

全部0条评论

快来发表一下你的评论吧 !