ChatGPT算力芯片如何做算力输出

人工智能

描述

我们谈到算力芯片和内存,这一期我们来聊聊算力芯片如何做算力输出,进而形成ChatGPT等生成式AI背后的算力基座。

现在的算力服务器中,里面并不是一颗颗芯片堆叠在一起,而是一张张算力卡并排插在卡槽里。目前大部分算力服务器单台放置8张或者16张算力卡。

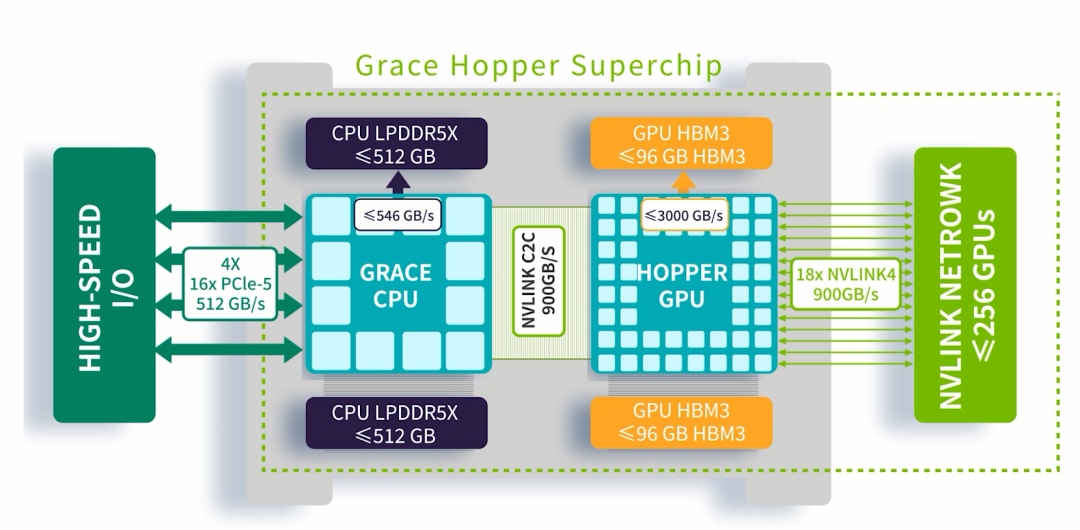

算力卡的核心当然还是计算芯片,会搭配大容量高带宽的内存、缓存,以及搭载CPU用于调度,为了帮助数据传输,便会使用高速通道,这便是PCIe(高速串行计算机扩展总线标准)在系统中的作用:提供总线通道。

图:算力卡示意图

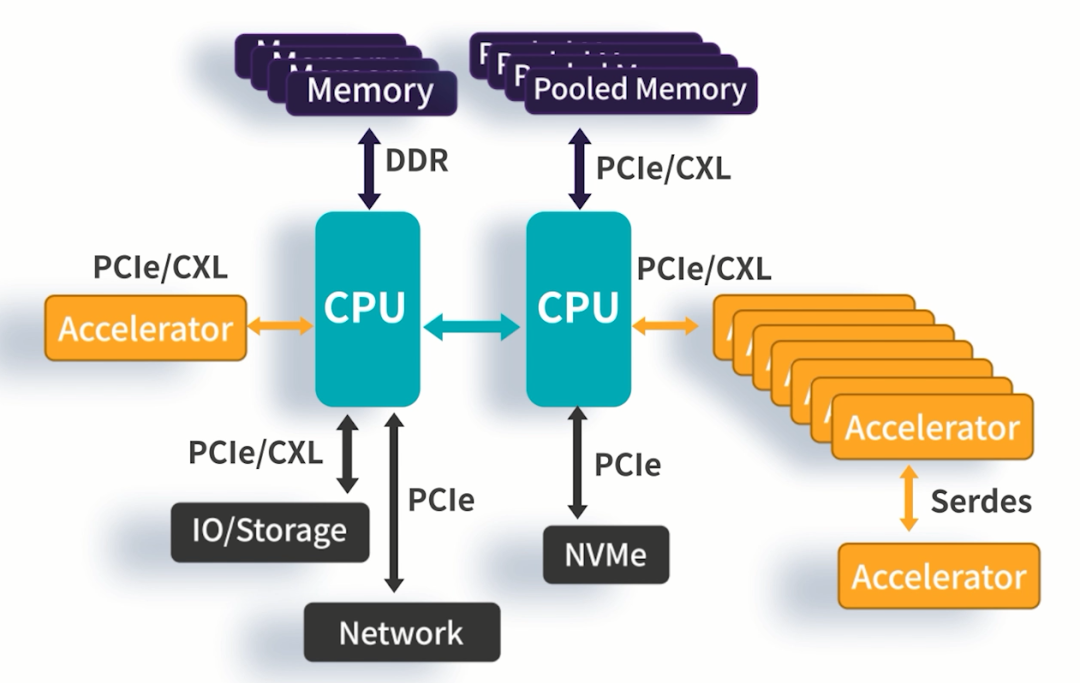

PCIe在数据运算中的应用非常广泛,比如CPU控制和调度芯片组进行工作会采用PCIe总线,算力卡和算力卡之间的互联也可能用到Serdes总线,计算好的数据存入到SSD硬盘中也是使用PCIe总线,算力中心里的交换机内部CPU与Switch芯片之间,采用PCIe总线。

图:PCIe总线在AI异构计算系统中的应用

因此,PCIe相当于是一种通用的总线标准,串联起整个AI背后的异构计算系统。通过采用PCIe接口,研发人员完全不必担心计算芯片、加速芯片、内存芯片、存储芯片、网关芯片和交换机等人工智能系统不同组件之间的互联问题。

PCIe从多个方面赋能当前人工智能系统的高速发展,包括以下几个特性:

1. 高效传输

2. 高可扩展性

3. 实时处理能力

4. 持续优化的低功耗性能

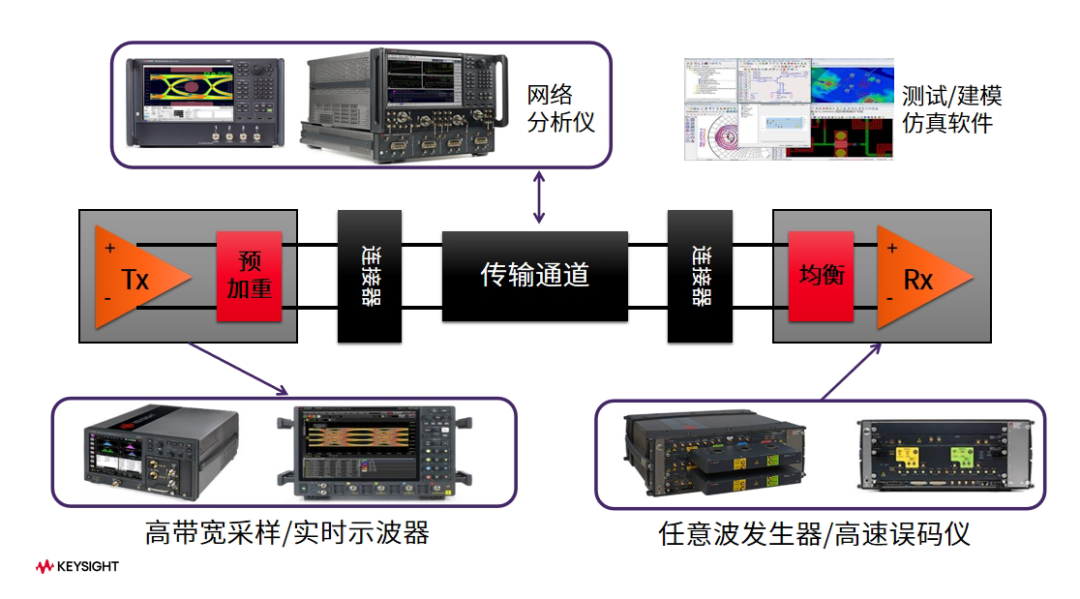

由于PCIe连接了系统中核心的芯片,又承担着数据传输的责任,因此其性能可靠性非常重要。在实际测试过程中,首先要测试PCIe接口的上传和下载峰值速度,以及稳定传输的速度,这是保证高效计算的关键。然后是测试PCIe接口的电气特性,包括传输功耗,以及高速逻辑唤醒等低功耗功能的具体表现,如下图:

图:是德科技PCIe测试拓扑图

此外,在PCIe接口稳定性方面,还要测试热插拔特性、隔离度和EMC性能等。当然,目前有一些厂商已经不满足于PCIe的传输速度,于是他们自己研发了一套连接标准。比如,英特尔提供Xe Link用于算力卡的互联,这是一种基于PCle 5.0扩展的新协议;英伟达则是开发了NVLink作为PCle的替代方案,带宽和能效能够达到PCle 5.0的数倍。这些自研方案会带来更高的测试挑战,对于是德科技而言,无论采取的是PCle协议,还是自研的高速互联协议,我们的方案都能够满足相关测试需求,如下图:

图:是德科技PCIe 6.0全链路测试方案

审核编辑:黄飞

-

ChatGPT背后的算力芯片2023-05-21 4538

-

【核芯观察】ChatGPT背后的算力芯片(二)2023-05-28 3832

-

【核芯观察】ChatGPT背后的算力芯片(三)2023-06-04 3547

-

大算力芯片的生态突围与算力革命2025-04-13 2770

-

ChatGPT技术:AIGC对算力有哪些需求?2023-02-15 1955

-

云端算力芯片为什么是科技石油?2023-07-12 1636

全部0条评论

快来发表一下你的评论吧 !