怎么通过HyperLynx DRC增强大规模PCB设计验证能力呢?

描述

“HyperLynx DRC已被证明是我们进行设计验证时不可或缺的工具,在确保我们的设计具有优异的性能方面发挥了关键作用。得益于西门子专门为我们量身定制的创新功能,我们的验证流程得到了变革性的改进。以前我们需要花一天多的时间才能完成的验证,现在只需要一个小时。这种效率的提升让我们能够在设计阶段进行多次检查,更大程度地减少了迭代循环,并显著缩短了我们的设计周期,成为我们打破行业格局的一大利器。”

——HerbertLee,MediaTek,Inc.模拟设计和电路技术资深部门经理

在快节奏和不断发展的电子领域,开发具备更强性能和功能的产品至关重要。但是,这种进步也会带来一系列挑战,这些挑战主要涉及产品的复杂性。大规模印刷电路板(PCB)的设计和验证尤其如此。

HyperLynx DRC 通过引入创新的区域裁剪功能,能够将运行速度提高136倍,因而成为大规模和多站点PCB 设计的可行解决方案,确保电子产品的技术进步真正成为可靠性、精度和效率的代名词。在复杂的电路板上应用区域裁剪功能,可使总检查时间显著缩短99.2%,从近34小时减少至区区15分钟,充分体现了其在优化PCB检查过程方面的变革性潜力。

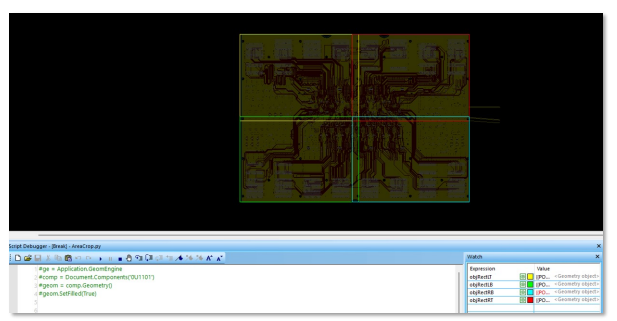

图:将设计划分为四个区域。

先进电子系统设计团队面临着以下几个行业挑战:

1. 产品的复杂性

2. 容易出错的过程

3. 检查频率不足

4. 后期错误检测

5. 仿真挑战

为应对行业中普遍存在的挑战,HyperLynx DRC 作为基于规则的检查器,已成为一种革命性的解决方案,能够使用几何计算快速识别潜在的PCB设计错误。HyperLynx DRC 是一个基于规则的多方位检查器,擅长快速识别潜在的设计错误。它提供了100多个预定义规则和高效的嵌入式引擎,大大缓解了业界普遍存在的挑战并优化了PCB验证过程。

1.开箱即用的规则

HyperLynx DRC 提供了100多个预定义规则,范围涵盖信号完整性、电源完整性、电磁干扰、静电放电、DC-DC转换器等模拟电路、爬电、间隙和IC封装特定检查。

2.高效的嵌入式引擎

多种嵌入式引擎,如几何形状引擎、图形引擎、场解析器和爬电引擎,有助于高效地检查各种技术挑战。

3.错误违规的管理

它通过一种独特的方法来管理错误违规,这种方法是允许用户创建对象列表、将规则应用于特定对象以消除不必要的检查,从而大幅缩短了检查时间。

4.增强的筛选功能

可以手动或自动生成对象列表,从而获得强大的筛选功能,以重点关注相关对象。

然而,HyperLynx DRC的全面功能也会带来一系列挑战。基于规则的几何运算虽然速度很快,但有时可能延长大型复杂设计的开发周期。此外,在设计阶段,用户可能希望关注特定的设计区域或特定走线。

区域裁剪功能

为改善这些问题,HyperLynx DRC引入了区域裁剪功能,允许用户隔离和仔细检查特定的设计区域,从而简化验证过程,具体优势如下:

•用户友好的界面:用户可以通过在向导中选择走线或元器件来轻松指定区域。

•自动裁剪:该向导会自动通过预定义的合并操作,根据考虑的对象裁剪设计,并创建一个新项目进行检查。

HyperLynx DRC的区域裁剪功能让用户能够专注于特定的设计区域,从而简化验证过程,降低复杂性并提高准确性。

审核编辑:刘清

-

HyperLynx 2409新增功能和改进功能2024-11-04 2238

-

高速PCB设计软件HyperLynx使用指南.zip2022-12-30 781

-

DRC pads HyperLynx为PCB设计提供电子规则检查2019-11-06 5585

-

PADS约束管理系统创建、审查和验证PCB设计约束2019-11-04 2744

-

HyperLynx DRC功能和优势2019-10-08 13290

-

HyperLynx DRC黄金版功能和优势2019-09-17 10349

-

HyperLynx置于整体PCB设计的过程图解2019-08-07 4539

-

大规模MIMO的性能2019-07-17 2539

-

PCB设计电气规则检查器解决DRC问题2019-05-21 7870

-

PCB设计后期处理之DRC检查2017-10-26 20590

-

如何使用 HyperLynx DRC 来查找 SERDES 设计2016-05-24 990

-

如何使用HyperLynx_DRC来查找SERDES设计2016-01-06 1447

-

Veloce平台在大规模SOC仿真验证中的应用2010-05-28 2354

-

高速PCB设计HyperLynx使用指南2010-04-03 1028

全部0条评论

快来发表一下你的评论吧 !