AMD Kria KR260 DPU配置教程

描述

本文作者:AMD 工程师 Shaoyi Chen

这篇文章我们将为 AMD Kria KR260 在 AMD Vitis 上创建硬件加速平台。 我们将从 KR260 预设文件开始,添加平台所需的外设并对其进行配置。 一切设置完毕后,我们将把硬件设计导出到 XSA。

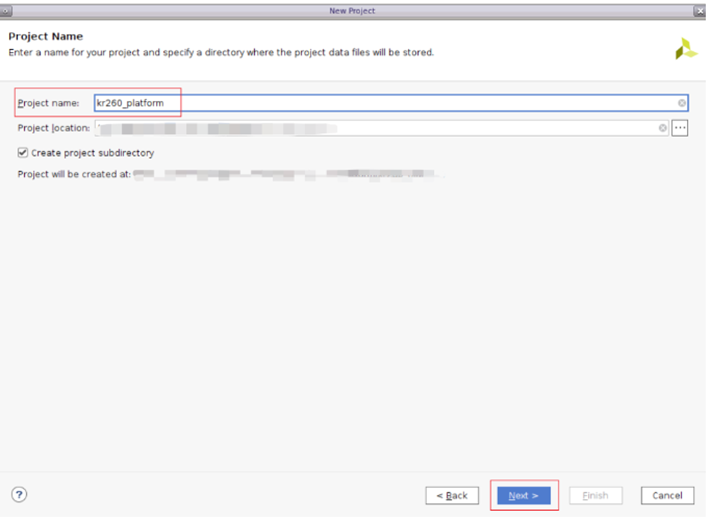

创建名为 kr260_platform 的 Platform

Create Project > Next

Project name: kr260_platform > Next

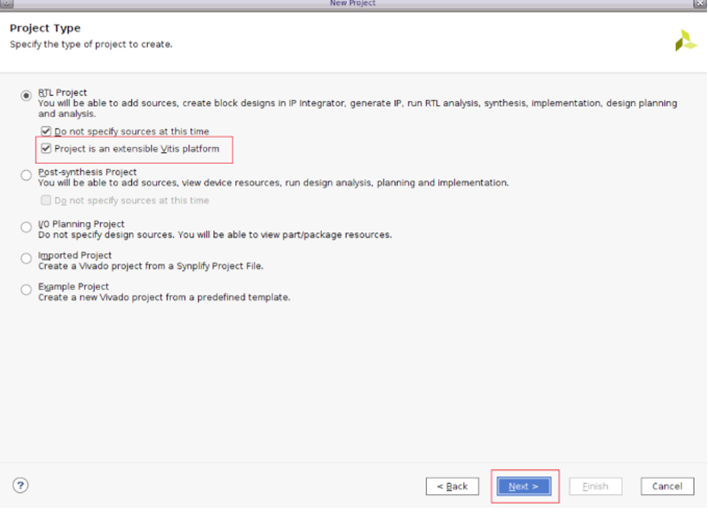

勾选 "Project is an extensible Vitis platform" > Next

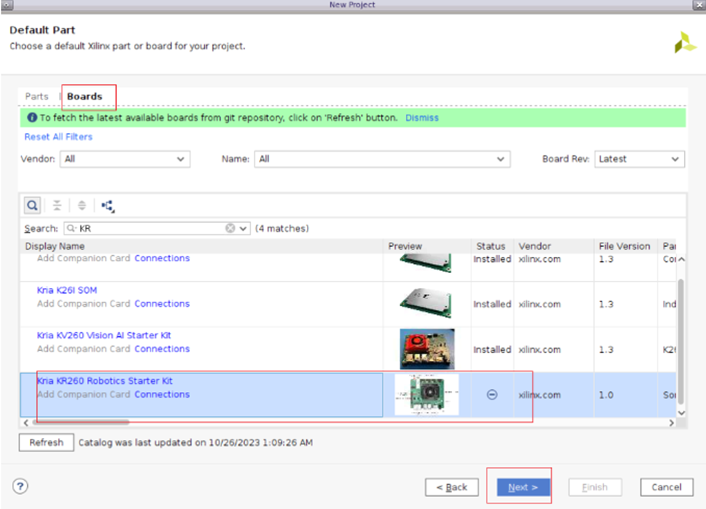

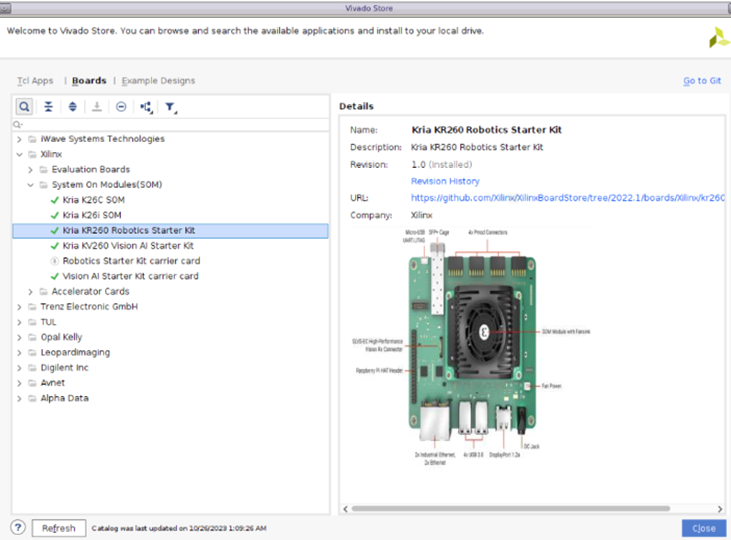

开发板选择 Boards > KR260 > Next > Finis

如果没有安装 KR260,需要先安装 KR260。

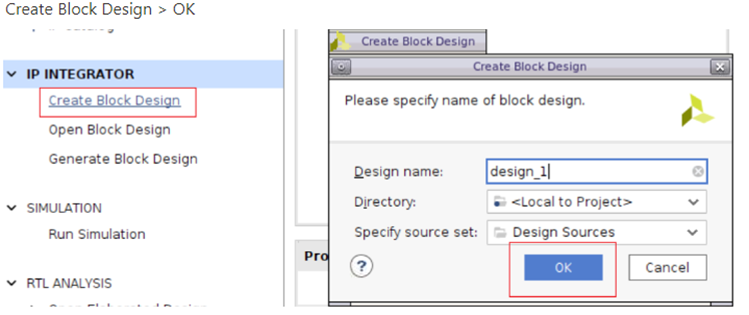

创建一个 Block Design

Create Block Design > OK

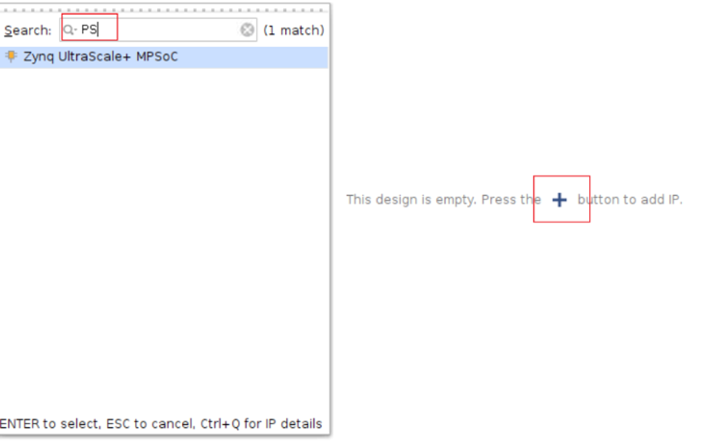

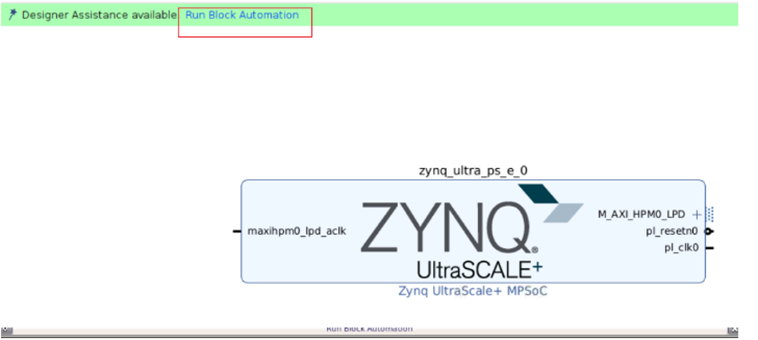

Add PS > Run Block Automation > Apply Board Preset > OK

在此阶段,AMD Vivado 自动添加了 AMD Zynq UltraScale+ MPSoC,并应用了 KR260 的所有板卡预设选项。 预设选项包括 MPSoC PS 模块配置和引脚分配。

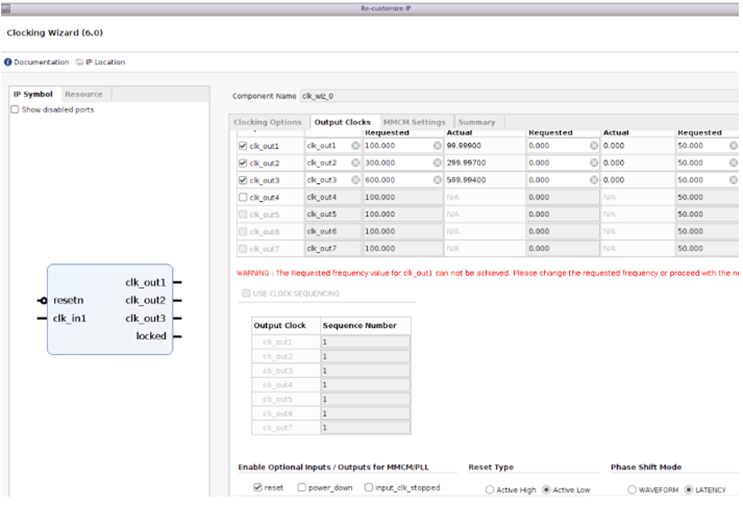

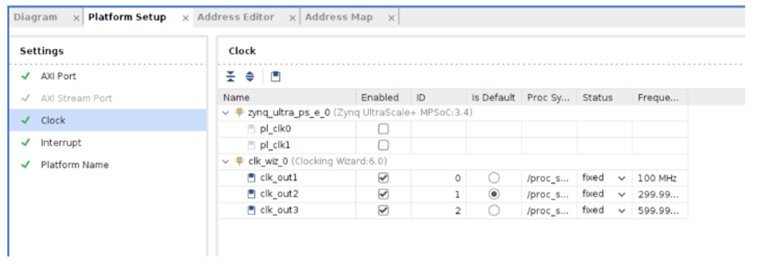

创建时钟和复位

Add a Clocking Wizard

clk_out1 to 100 MHz

clk_out2 to 300 MHz

clk_out3 to 600 MHz

Reset Type to Active Low > OK

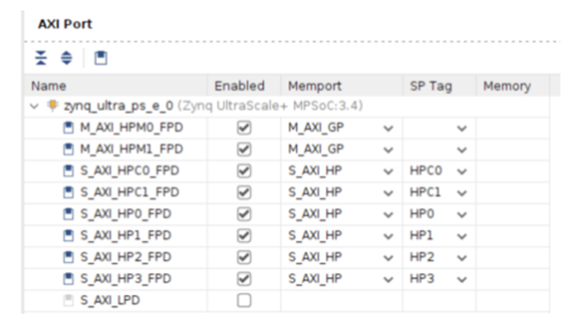

使能 Platform 的 AXI 接口

使能 PS 的 AXI Master 接口:

打开 Platform Setup 界面。

打开 AXI Port 子页面。

在 zynq_ultra_ps_e_0 选项下,使能

M_AXI_HPM0_FPD 和 **M_AXI_HPM1_FPD。**

保持 Memport 为 M_AXI_GP, sptag 为空。

使能来自 AXI Interconnect 的 AXI Master interfaces:

在 ps8_0_axi_periph 选项下, 点击 M01_AXI, 按住 Shift 并点击 M07_AXI 以选中从 M01_AXI 到 M07_AXI 的多个接口。

右键选中的选项并点击使能。

保持 Memport 为 M_AXI_GP,sptag 为 empty。

使能来自 PS 的 AXI Slave interfaces 来允许 Kernels 连接 DDR 内存:

在 zynq_ultra_ps_e_0 选项下, 选中所有的 AXI slave 接口: 按住 Ctrl 并点击

S_AXI_HPC0_FPD, S_AXI_HPC1_FPD, S_AXI_HP0_FPD, S_AXI_HP1_FPD, S_AXI_HP2_FPD, S_AXI_HP3_FPD。

右击所有的选项并点击 enable。

修改 S_AXI_HPC0_FPD 和 S_AXI_HPC1_FPD 的Memport 为 S_AXI_HP。

将接口的 sptag 名字修改为 HPC0, HPC1, HP0, HP1, HP2, HP3。 v++ 可以在 linking 阶段使用这些接口。

导出 XSA

点击 Validate Design 按钮来确认 block design 设计有效。在这个过程中 Vivado 会报告一个 critical warning,这是因为 /axi_intc_0/intr 没有被连接。因为 v++ 链接器会将中断连接到这个端口上,所以这个警告可以被忽略。

为 block design 创建一个 module wrapper:

在 Source 界面, Design Sources group 上右键 design_1.bd。

选择 Create HDL Wrapper...

选择 Let Vivado manage wrapper and auto-update。

点击 OK 来为 block design 生成 wrapper。

生成设计:

在 Flow Navigator 窗口下选择 Generate Block Design。

点击 Generate。

在 Flow Navigator 窗口下选择 Generate Bitstream。

点击 Yes.

导出 Platform:

点击菜单 File -> Export -> Export Platform 来运行 Export Hardware Platform wizard。

点击 Next 。

选择 Platform Type 为: Hardware, 点击 Next。

选择 Platform State: Pre-synthesis, 使能 Include Bitstream,点击 Next。

输入 Platform 属性并点击 Next。比如:

Name: kv260_hardware_platform

Vendor: xilinx

Board: kv260

Version: 0.0

Description: This platform provides high PS DDR bandwidth and three clocks

输入 XSA 文件名:

kv260_hardware_platform 并保持默认导出地址。

点击 Finish。

kv260_hardware_platform.xsa 将会被生成。

审核编辑:汤梓红

-

AMD 机器人入门套件开启未来智慧工厂2022-05-18 3752

-

AMD Kria KR260 DPU配置教程22024-01-19 3426

-

AMD Kria™ KR 260套件+ROS 2快速开发机器人解决方案2024-06-21 10817

-

PROPHESEE 携手 AMD,推出业界首款兼容 Kria™ KV260 视觉 AI 入门套件的事件视觉解决方案2024-05-30 1469

-

【AMD KV260视觉入门开发套件试用】1、开箱&烧录镜像系统体验2023-07-15 897

-

【KV260视觉入门套件试用体验】KV260开发板初使用2023-09-18 2379

-

【KV260视觉入门套件试用体验】四、学习过程梳理&DPU镜像&Resnet502023-09-26 1052

-

为Kria KV260添加USB WiFi2022-12-23 1081

-

Rpi SenseHAT与AMD-Xilinx Kria KR260和Petalinux的接口2023-07-13 1305

-

Kria KR260机器人入门套件:通过硬件加速释放机器人2023-09-14 1120

-

AMD Kria KR260 DPU配置教程32024-01-26 2808

-

机器人开发套件 Kria KR2602025-04-11 1458

-

AMD Kria KV260视觉AI入门套件更新升级2025-07-18 748

-

探索Xilinx Kria KR260机器人入门套件:开启机器人应用开发新旅程2025-12-15 121

全部0条评论

快来发表一下你的评论吧 !