势垒电容概念介绍

描述

势垒电容(Barrier Capacitance)的大小直接影响了半导体器件的电学性能和可靠性。

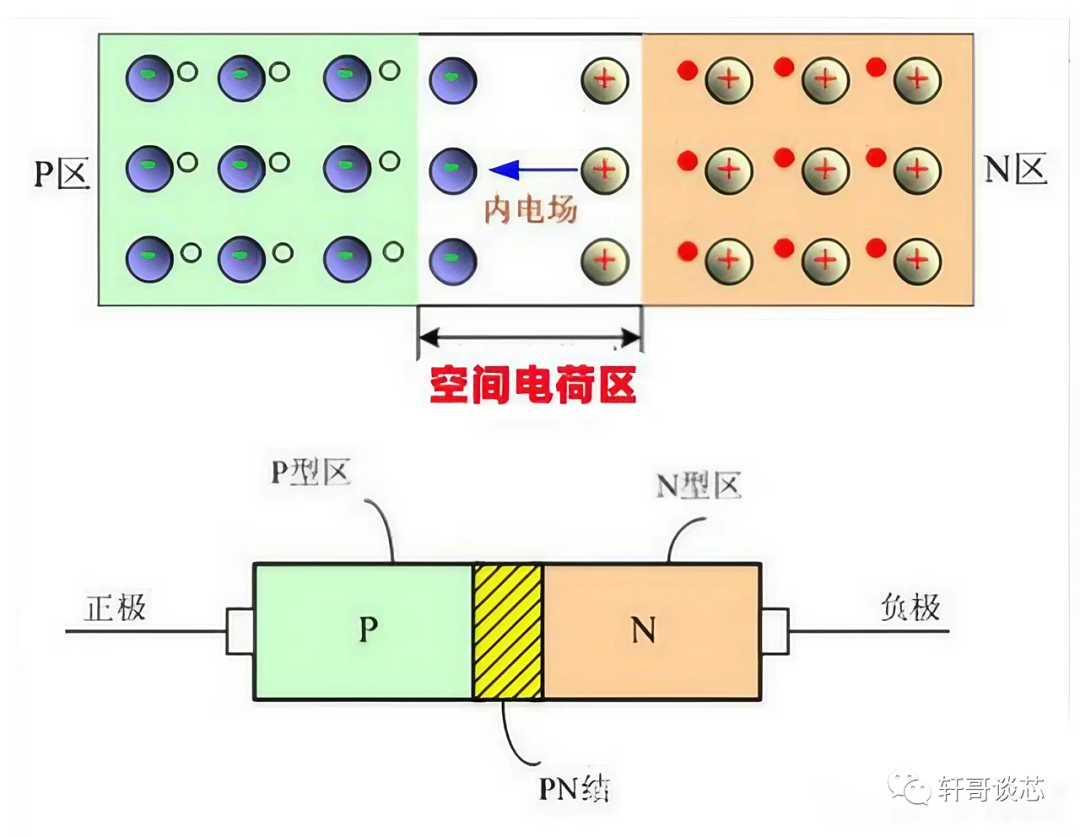

势垒电容CB是由势垒区中的电荷量QB和势垒区的宽度W决定的。势垒区是指PN结或金属-半导体接触处,由于内建电场的作用,电子和空穴被限制在两个区域之间形成的一个耗尽层。势垒区的宽度W是指势垒区在垂直于电流方向上的长度。

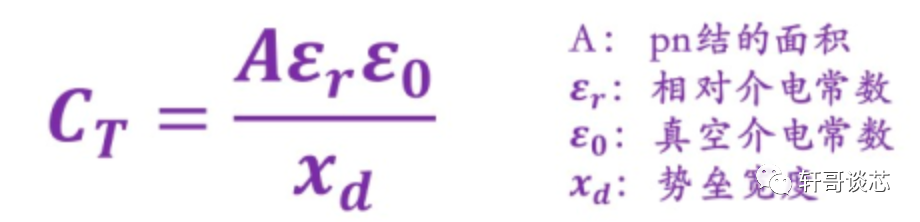

势垒电容的大小可以理论的计算一下:

当外加电压有△U 的变化时,电荷有△Q 的变化,假设两边的距离为 Xd 时。势垒电容为:

势垒电容CB的大小还与势垒区的载流子浓度、内建电场强度以及温度等因素有关。当载流子浓度较高时,势垒区内的电荷量增加,势垒电容也会相应增大;当内建电场强度较大时,势垒区内的电荷量减少,势垒电容也会相应减小;当温度升高时,载流子浓度增加,势垒区内的电荷量增加,势垒电容也会相应增大。

此外,势垒电容还可以用于制备电容器、存储器等电子设备。例如,利用金属-半导体接触处的势垒电容可以实现非挥发性存储器的设计和制备。非挥发性存储器是一种可以在断电后保持存储信息的电子设备,具有广泛的应用前景。

总之,势垒电容是半导体器件中的一个重要参数,它描述了PN结或金属-半导体接触处的势垒对电荷的存储能力。势垒电容的大小与势垒区的宽度、载流子浓度、内建电场强度以及温度等因素有关。通过合理设计和控制势垒电容的大小,可以提高半导体器件的性能和可靠性,实现各种电子设备的功能和应用。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

二极管扩散电容和势垒电容(可下载)2025-04-24 1070

-

二极管的电容效应势垒电容CB介绍2023-11-01 2683

-

PN结反向偏置时,随着反向电压的增加,势垒电容是增加还是减少?2023-10-19 6916

-

肖特基势垒二极管的作用 肖特基势垒二极管的工作原理2023-09-02 4712

-

二极管势垒电容和扩散电容讲解2023-06-27 14003

-

SiC肖特基势垒二极管和Si肖特基势垒二极管的比较2023-02-08 1587

-

【原创推荐】二极管扩散电容和势垒电容2021-10-08 6184

-

肖特基势垒二极管电路设计2021-01-19 4163

-

肖特基势垒二极管的特点2019-04-30 3403

-

浅析肖特基势垒二极管2019-04-11 1868

-

肖特基势垒二极管的特征2018-12-03 2140

-

类比法学习势垒电容和扩散电容2014-06-22 3224

-

肖特基势垒二极管,肖特基势垒二极管原理/结构2010-02-26 4071

全部0条评论

快来发表一下你的评论吧 !