AMBA总线中APB interconnect的介绍

电子说

描述

之前的两篇文章给大家介绍了APB协议相关的知识点,并结合实际的代码给大家讲解了一下APB slave的设计。并说明了一下APB slave mux这个模块。

上一篇文章提到:通常而言,APB的interconnect模块只能连接一个master,多个Slave。因此继续管它叫interconnect感觉差了点意思。所以一般就叫它slave mux了。巧的是前几天有个同事碰到了需要多个APB master的情况。本人便帮忙调研APB是否真的只能是一主多从的结构。没想到还真搜到了一些公司的设计,是支持多主多从的APB Interconnect,这种情况下确实是名副其实的Interconnect了。

首先解释一下什么是Interconnect,顾名思义,互联。起作用是把不同的组件连接在一起,包括但不限于:

处理器和处理器

处理器和Memory

处理器和Cache

Cache和Cache

IO设备等

对于SoC工程师,把互联理解成一个开关即可。它用来管理并指挥所连接的设备之间的通信。

1、一主多从的APB Interconnect

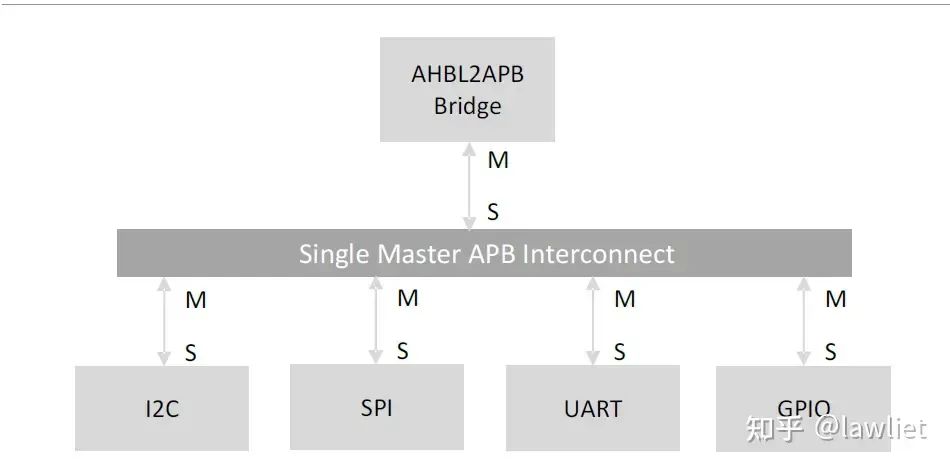

这种情况下Interconnect和mux没有本质区别,所以很多情况下直接叫它APB mux或者APB slave mux。具体到实际的SoC设计中大概长下面这样子,可以看到它只有一个Master,AHB2APB的转接桥。同时有多个Slave模块。这也是我们在SoC中最常遇到的情况。

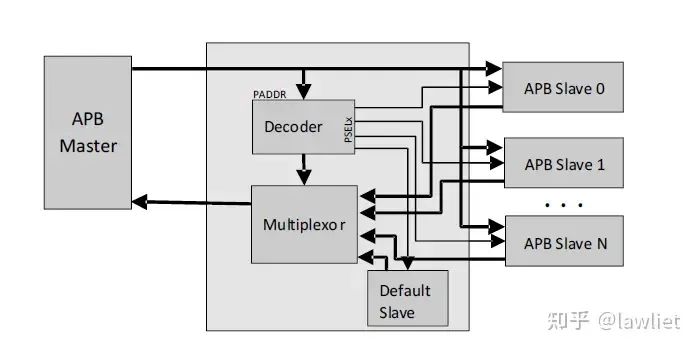

我们看一下这个Interconnect的内部具体长什么样子,如下图所示,可以看到主要逻辑就是译码器+MUX。 对于Master-->Slave的信号而言,PENABLE、PWRITE、PWDATA、PADDR信号直接由Master给所有的Slave。而PSELx信号有SLave数量这么多组,其逻辑应该是PSELx = PSEL & dec[ x] & en[ x]; 译码器根据PADDR选择拉高某个SLAVE的dec信号,也就是最多选中其中的某一个Slave。此外下面这个图中有一个默认slave,当没有任何slave被选择的话,则会选中默认的slave,用来应对地址越界的错误情况。该Slave默认的PRDATA默认为0,PSLVERR默认为1。 对于Slave-->Master的信号而言,PREADY、PRDATA、PSLVERR由MUX进行选择,从指定的Slave传给Master。

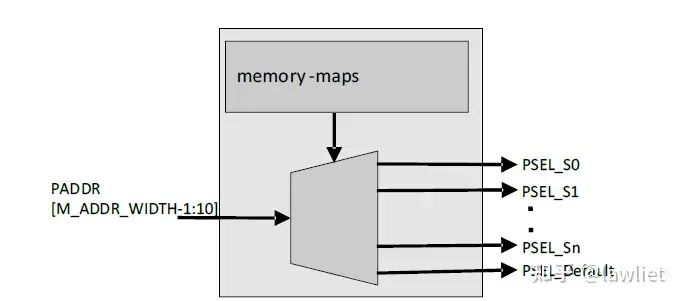

1.1、Decoder

译码器模块对每一笔传输进行地址译码,给每一个Slave相应的PSEL信号。Decode逻辑非常简单,就是根据当前的PADDR选中某一个Slave,如下图所示。这个模块功能更加丰富,地址映射可以静态的配置(工作的时候不能配置),实际上大部分的SoC设计中,地址映射应该是完全固定死的,无法更改的。这个是FPGA提供的IP,所以相对更灵活一点。

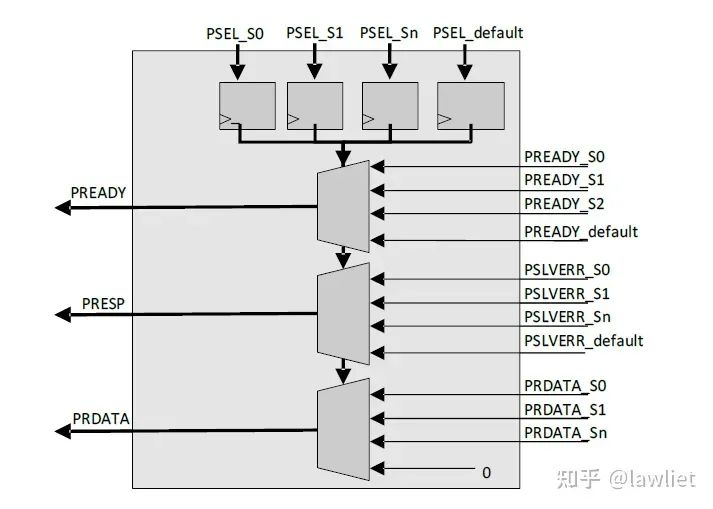

1.2、Multiplexor

该模块基于MUX提供的PSELX信号,从多个Slave中选择合适的PRDATA、PREADY、PSLVERR信号,设计很简单,就不多讲解了,直接看图:

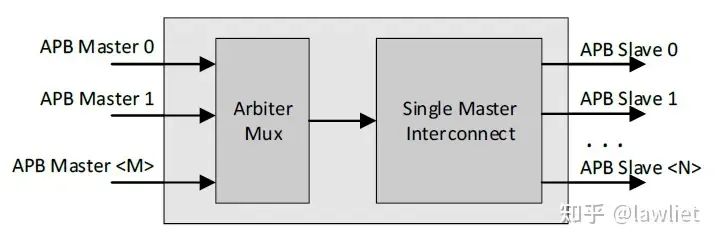

2、多主多从的APB Interconnect

上面这套东西和我上一篇文档的APB slave mux其实没有本质区别,也非常的好理解。但是如果实际的需求真的需要多个Master怎么办呢?虽然APB官方没有提供这种设计示例,但实际上当然是可以实现的。我们只需要在一主多从的Interconnect的基础上增加一个Arbiter mux即可:

当然这种情况下,只支持一对一的访问,所以实际上效率还是比较低的。仲裁方式可以使用固定优先级仲裁,也可以使用Round Robin仲裁。

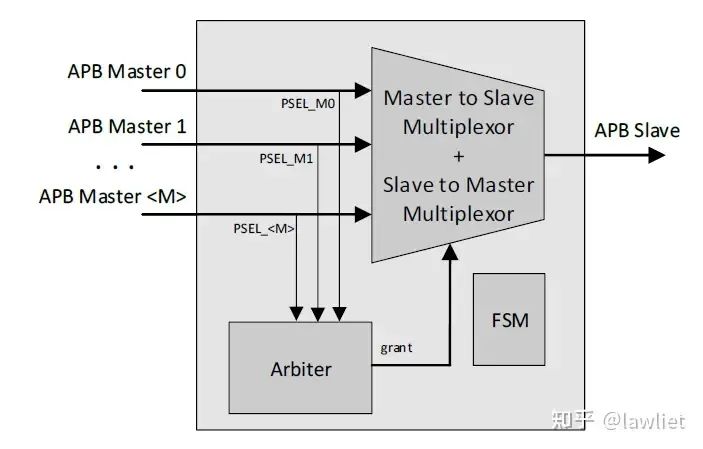

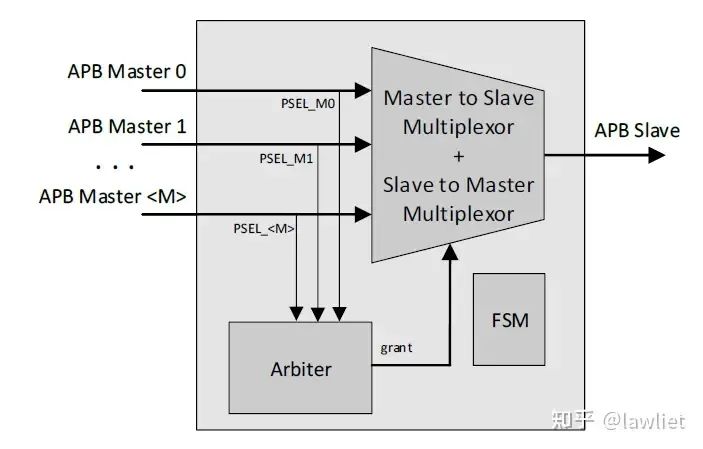

2.1、Arbiter Mux

顾名思义,Arbiter+MUX。Master to Slave Multiplexor对多个PSEL进行仲裁,然后选择其中的一个PSELX,基于这个PSELX,选择合适的PADDR、PWRITE、PSELX、PENABLE给Single Master Interconnect模块。 相应的,Slave to Master Multiplexor将PRDATA、PREADY、PSLVERR路由到相对应的Master。从而完成整个传输流程。下图这些向右的箭头实际上是双向的。Master和Slave互相交互,完成传输过程。

这篇文章给大家讲解了APB Interconnect这个模块。除了官方说的一主多从,实际上我们也可以实现多主多从的Interconnect。当然这个模块实际用的很少很少,大家可以根据实际需求决定是否要使用该模块。

-

AMBA总线中APB slave设计介绍2024-01-13 2382

-

什么是APB协议/总线?APB总线入门2024-01-02 8194

-

关于AMBA APB总线的知识点介绍2023-11-29 2604

-

AMBA总线—apb简介2023-06-05 3871

-

AMBA总线那些事之APB2023-05-04 3439

-

AMBA中的APB总线协议详解2022-06-07 3921

-

AMBA AHB总线与APB总线资料合集2022-04-07 5222

-

ARM总线协议AMBA中AHB、APB的区别与联系2022-02-09 2479

-

数字IC验证:ARM总线协议AMBA中AHB、APB的简介、区别与联系2021-12-05 2299

-

介绍AMBA2.0总线2021-09-06 4087

-

浅述AMBA-APB总线2021-07-23 3446

-

基于AMBA总线介绍2021-05-19 2882

-

APB总线的应用框图及接口信号2020-11-17 14739

-

基于AMBA APB总线NandFlash控制器的设计2011-11-03 1089

全部0条评论

快来发表一下你的评论吧 !