RAM的应用-一种常见的解耦设计

电子说

1.4w人已加入

描述

在模块划分时,我们通常会考虑解耦合,即尽量减少模块间的交互,让模块间的接口尽量简单。

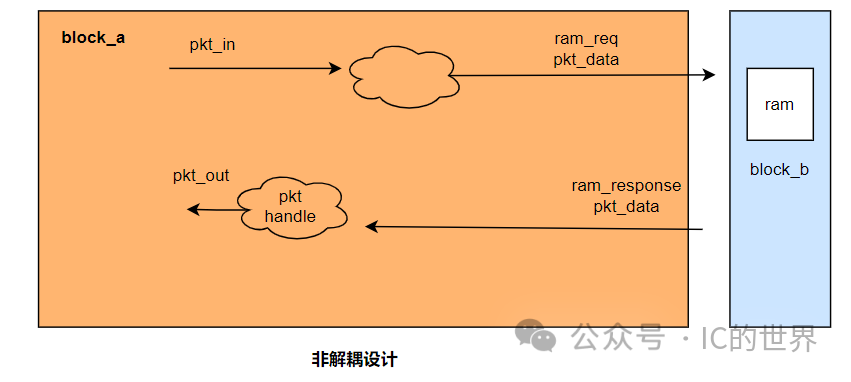

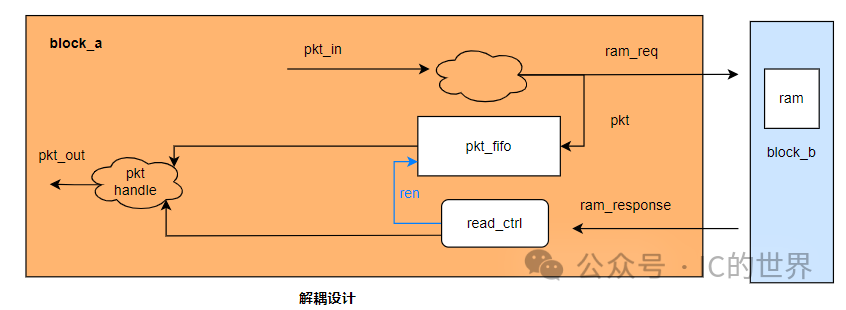

在包处理过程中,因为数据处理的需求,需要读取某些信息(配置信息,状态信息),如图中读取block_b中的ram,根据读返回的结果后对数据包进行处理。

为了解耦合,我们可以采用一个fifo(pkt_fifo)存储与ram请求(ram_req)无关的信息(数据包以及数据包的相关描述信息),等待response返回后,再从pkt_fifo读取相应的数据包信息对,从而对数据包进行处理。

如果不采用pkt_fifo存储包信息,那么会怎么设计呢?如非解耦设计图所示,不需要额外的fifo,将包信息(pkt_data)与访问请求(ram_req)一同传递给block_b模块,再由block_b将包信息(pkt_data)和访问响应(ram_response)一同送到block_a模块。

案例中的解耦合设计还有一个优点:节约资源和功耗。如果从发起ram_req到返回ram_reponse的流水比较长,例如需要几十甚至上百个时钟周期,在非解耦设计中,就需要使用寄存器对pkt_data进行打拍,而解耦设计中采用fifo存储pkt_data,虽然从存储bit角度计算两种设计需要的bit位几乎相同,但是fifo(用ram实现)面积更小,功耗更低。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

怎样去搭建一种永磁同步电机的数学模型2021-08-06 2168

-

一种基于滑模观测器的电流偏差解耦控制方法2021-08-27 1696

-

分享一种基于大RAM的系统设计IoT RAM2022-02-14 973

-

一种基于PID神经网络的解耦控制方法的研究2009-06-15 764

-

一种新的PI调节器在交流解耦控制系统中的应用2009-11-01 719

-

光耦隔离的4种常见方法对比2012-05-31 133255

-

一种脉冲多普勒雷达解距离模糊的新算法2016-12-23 1129

-

一种带功率解耦的Flyback微型逆变器研究2017-01-04 1105

-

一种新型的高光谱图像解混算法2021-06-27 912

-

一种常见的解耦设计2024-01-17 1432

全部0条评论

快来发表一下你的评论吧 !