射频电路板上的地孔以及仿真说明介绍

描述

我们在初中物理就学过,电压又称电势差,即任意两个电势/电位的差值,一般认为无穷远处的电势为0,通常说的“电压”隐含条件就是相对于0电势的差值,但这个“无穷远处的0电势”太含糊了,实际电路分析的时候不可能去探测到它。好在电压跟绝对电势无关,它只是一个差值,因此我们可以任意选择电路中某一个电位作为参考基准点,人为规定它是0电势点,则这个基准点就称为“地”(Ground)。

人为定义好“地”以后,电路中任一点的电压就有了参考。说“电阻一端的电压是5V”,实际上是说“电阻某一端对地的电压是5V”,但如果说“电阻两端的电压是5V”,已经明确了是以电阻的某一端作为参考,并不以“地”为参考。

根据应用场合不同,又人为将“地”细分为“电源地”、“数字地”、“模拟地”、“射频地”,有很多文章和理论分析介绍应该如何处理电路中不同的“地”。本文仅浅谈一下自己对“射频地”的一些认识。

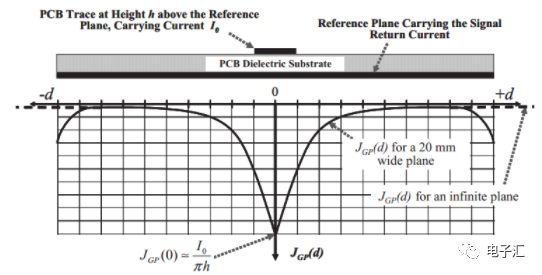

微带线回流的大小分布,如下图所示。电流分布在微带线的下方,且随着距离微带线正下方的距离越远,电流幅度越小。

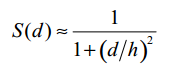

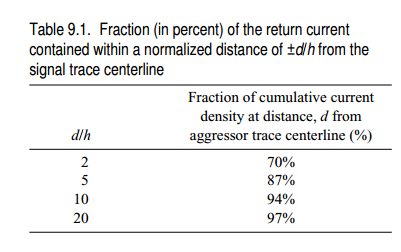

电流的分布,可以近似用以下公式表示:

其中,d是在回流平面上距迹线中心线的水平距离,h是介质厚度。

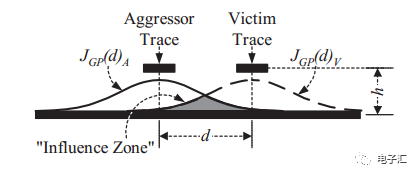

两根平衡走线,如果靠的比较近,就会有一部分回流重叠,随着d的距离的增大,在距离d范围内的电流越多,其数据关系如下表所示:

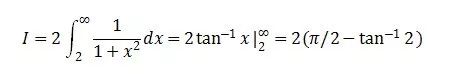

表中也可以通过对S(d)积分,然后进行计算得到。比如对于d/h=2时,则在d=2h以外的电流即为:

而总电流为:

所以包含在-d~d以内的电流的百分比为:

与上表中吻合。按同样的计算方法,可计算出当d=5h/10h/20h时,分别对应的值为87.4%/93.7%/96.8%。

地孔怎么加?

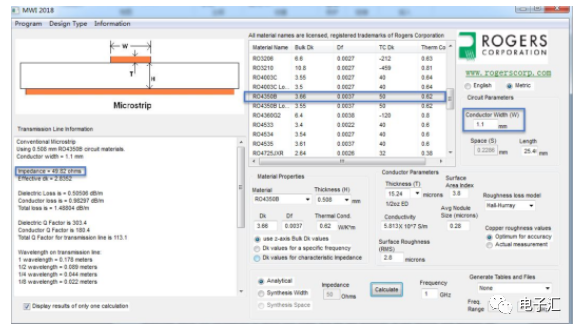

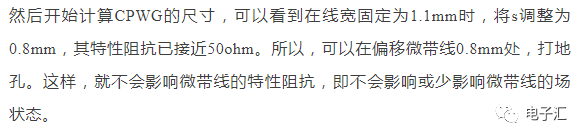

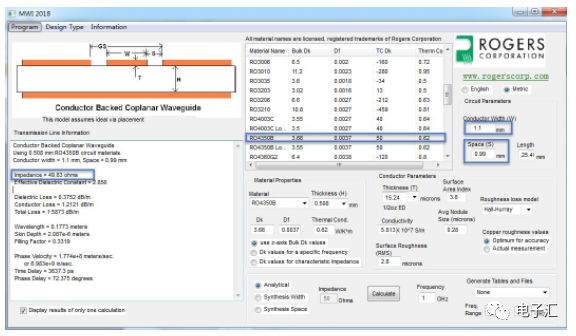

接下来,看看在这个尺寸下,满足3H原则么?

如果从这方面来看的话,整个射频板可能只需要打几个过孔就行了。不过,没有见过这样做的。一般射频板都是被打成筛子的。

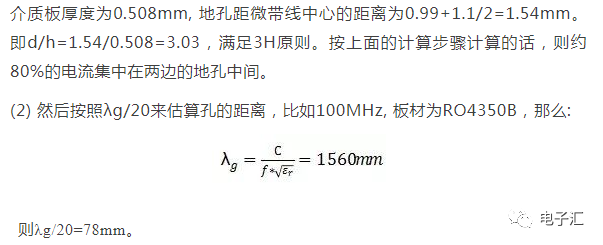

在算出来的λg/20比较大的时候,我一般是选择2mm~2.5mm的间隔打,如果λg/20比较小,就适当减小间隔,但是需要保证:

厂家能加工

不要把其他平面打断(这在数字板中经常需要注意,不要把电源平面打断)

怎么看待打孔可以增加隔离度呢?

在文献[3]中,用波导截止频率的观点来阐述了这个现象。

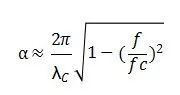

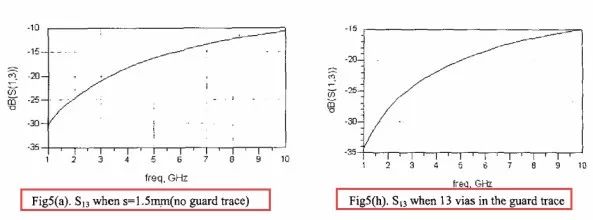

当信号进入小的缝隙或者非谐振盒子时,可以用波导的截止信号的衰减公式来估算。

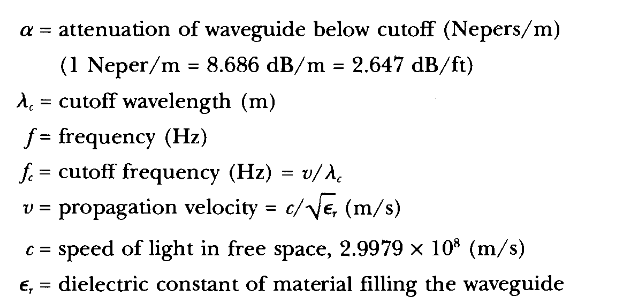

不过,我按照这个公式算下来的话,发现,如果是一排过孔,孔间距是2mm,孔的大小是0.3mm的话,算出来的经过过孔的衰减值才3.92dB,比我想象中的值小多了。这都有点让我不相信这公式的正确性。

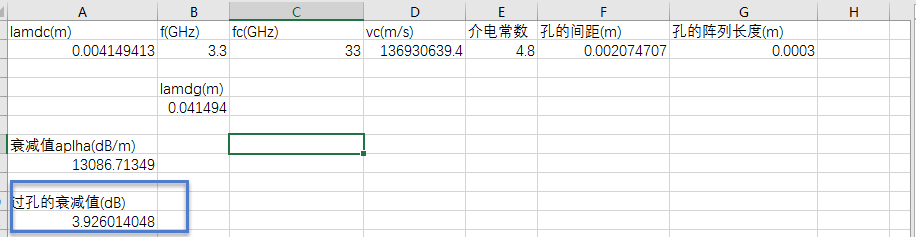

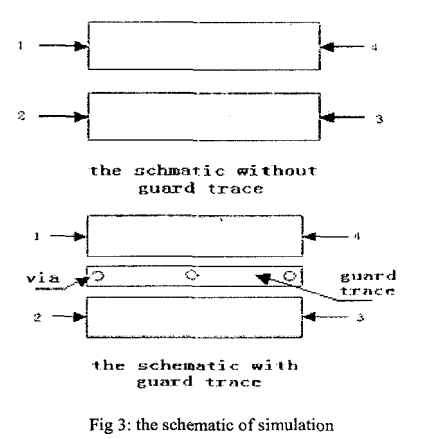

但是,当看到文献[4]时,我想,这公式可能是对的。文中,对下述原理图进行了仿真。

以下是仿真结果。发现量级也就在几个dB左右。隔离度还是主要取决于两个微带线的距离。

差分线的布地

下面,再简单说一下差分线周围的地线。

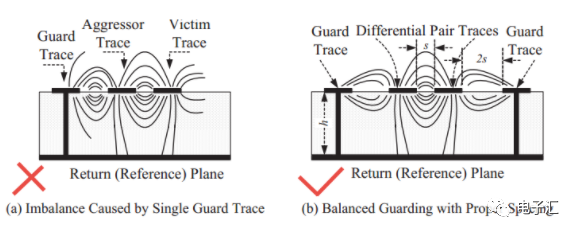

在给差分信号加保护地的时候,为了不破坏差分线之间的平衡关系,要求两边同时加地,而且要求地与差分线的距离至少要大于两倍的差分线的间距,这个还需要考虑信号到参考层的距离(H)。

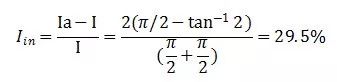

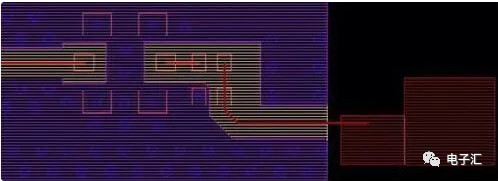

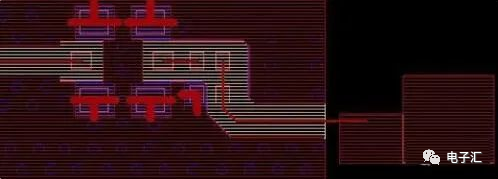

举个例子,我们将对多层电路板进行射频线仿真,为了更好的做出对比,将仿真的PCB分为表层铺地前的和铺地后的两块板分别进行仿真对比;表层未铺地的PCB文件如下图1所示(两种线宽):

图1a:现款0.1016mm的射频线(表层铺地前)

图1b:现款0.35mm的射频线(表层铺地前)

图1:表层为铺过地的PCB

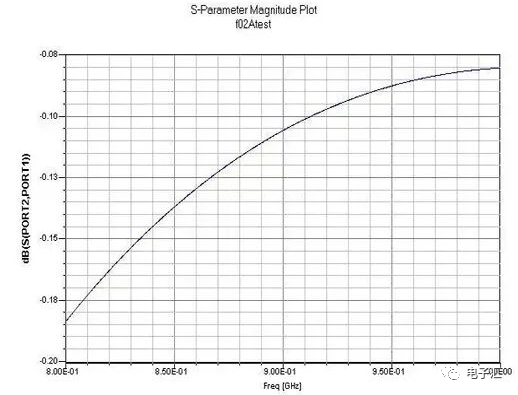

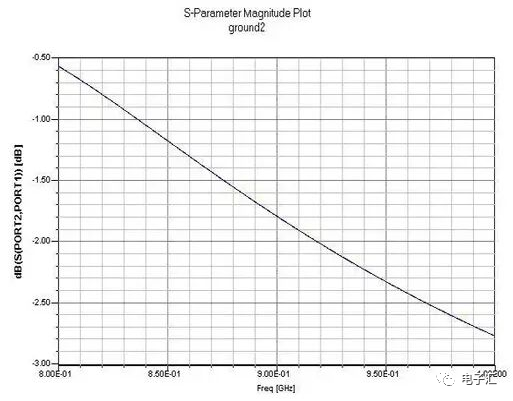

首先将线宽不同的两块板(表层铺地前)导入仿真软件中,在目标线上加入50Ω端口。针对不同线宽0.1016mm和0.35mm, 我们的仿真结果如图2所示,图中显示的曲线是S21,仿真频率范围为800MHz-1GHz。

图2a:表层为铺地的S21(线宽0.1016mm)

图2b:表层未铺地的S21(线宽0.35mm)

图2:表层未铺地的S21

由图中可以看到,在800MHz-1GHz的范围内,仿真的数据展示为小数点后一到两位的数量级,0.35mm的损耗要比0.1016mm的线小一个数量 级,这是因为0.35mm的线宽在该板的层叠条件下其特征阻抗接近50Ω。 因此间接验证了我们所做的阻抗计算(用线宽约束)是有一定作用的。

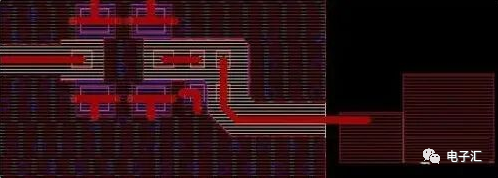

接下来,我们做了表层铺地后的同样的仿真(800MHz-1GHz),导入的PCB文件如下图:

图3a:0.1016mm的射频线(表层铺地)

图3b:0.35mm射频线(表层铺地)

图3:表层铺过地的PCB

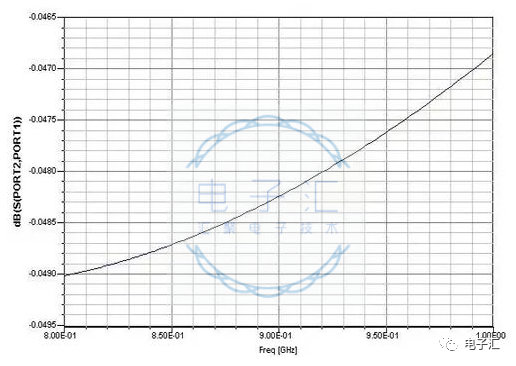

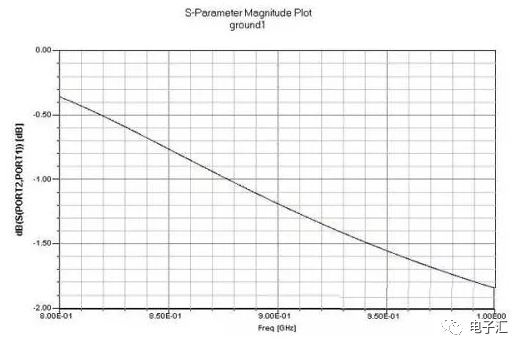

仿真结果如下图所示:

图4a:表层铺地后的S21(线宽0.1016mm)

图4b:表层铺地后的S21(线宽0.35mm)

图4:表层铺地后的S21

由图中看到,仿真的数据显示,该传输线的线损已经是1-2 dB的数量级了,当然0.35 mm的损耗要明显小于0.1016 mm的。另外一个明显的现象是相对于未铺地的仿真结果,随着频率由800MHz到1GHz的增加,损耗趋大。

我们可以从仿真的结果中得到这样一个结果:

射频走线按50欧姆走,可以减小线损;

表层的铺地事实上是将一部分RF信号能量耦合到了地上,造成了一定的损耗。因此PCB表层的铺地应该有所讲究。尽量远离RF线。工程经验是大于1.5倍的线宽。

-

激光焊锡应用:插件孔的大小对PCB电路板的影响2024-12-31 1967

-

一文详解半孔pcb电路板设计2024-04-25 2955

-

电路板布局设计的重点——pcb钻孔槽孔2023-10-13 3612

-

电路的原理图设计、电路仿真、印制电路板设计与信号完整性分析2023-01-04 1940

-

射频电路板设计技巧.zip2022-12-30 504

-

射频电路板设计法则2022-10-28 3040

-

浅谈射频电路板上的地孔以及仿真说明2021-04-20 10651

-

氩弧焊引弧电路板介绍2021-04-06 1909

-

PCB线路板中的盲孔和埋孔介绍2020-09-21 16864

-

射频电路板设计的要点2020-05-25 1934

-

电路板孔的可焊性对焊接质量有什么影响2019-11-29 3482

-

电路板为什么是绿色的_电路板上的元件介绍图2018-03-19 128256

-

盲孔与埋盲孔电路板之前的区别2017-10-24 5020

-

射频电路板设计技巧2017-01-28 1050

全部0条评论

快来发表一下你的评论吧 !