漫谈AMBA总线-AXI4协议的基本介绍

接口/总线/驱动

描述

带宽/BandWidth 和延迟/Latency 是衡量总线性能最重要的两个因素。

1.1 What is AMBA ?

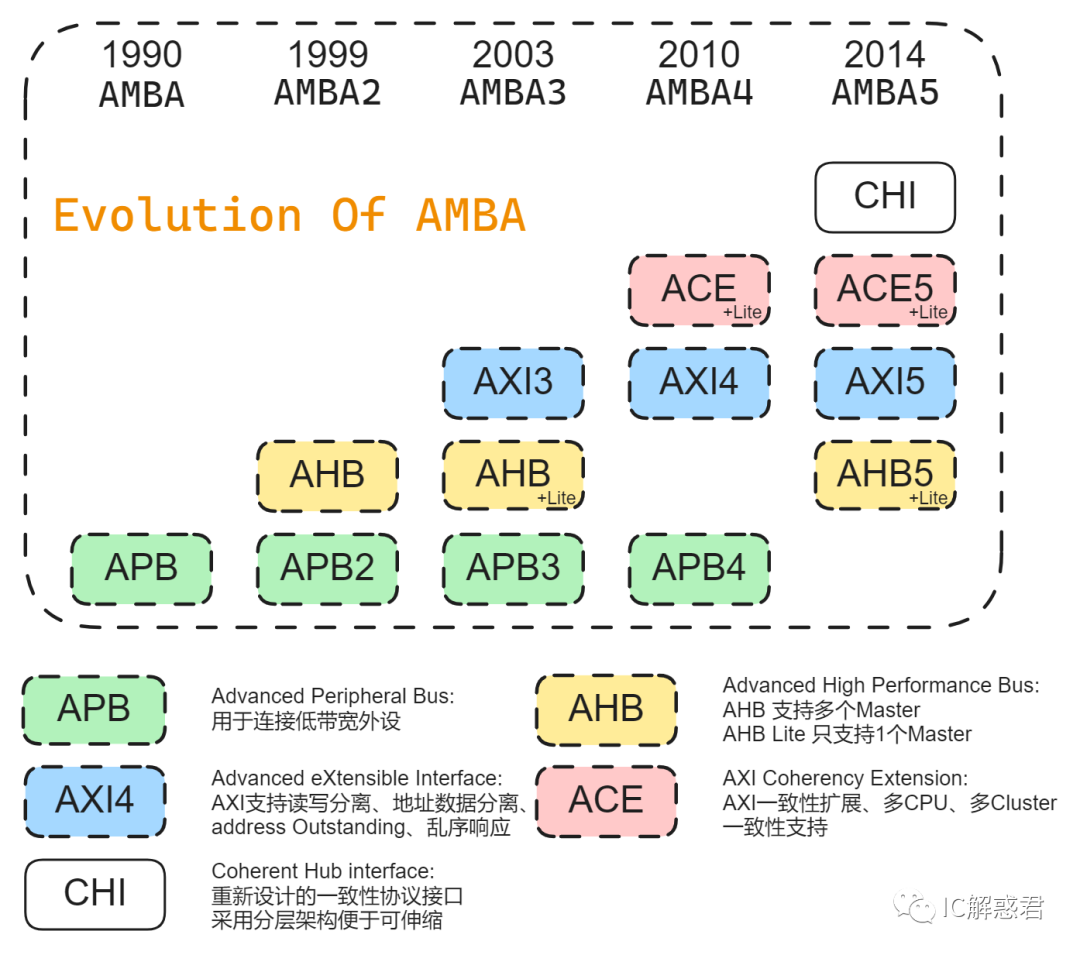

AMBA全称Advanced Microcontroller Bus Architecture(高级微控制总线架构),是一种开放的、标准的片上互联总线规范协议簇。从本质上来说,AMBA协议簇定义了片上功能模块是如何进行相互通信。同时随着时间演化,已经从AMBA到现在的AMBA5。协议簇的演化路径如下图所示:

1.2 Example for AMBA

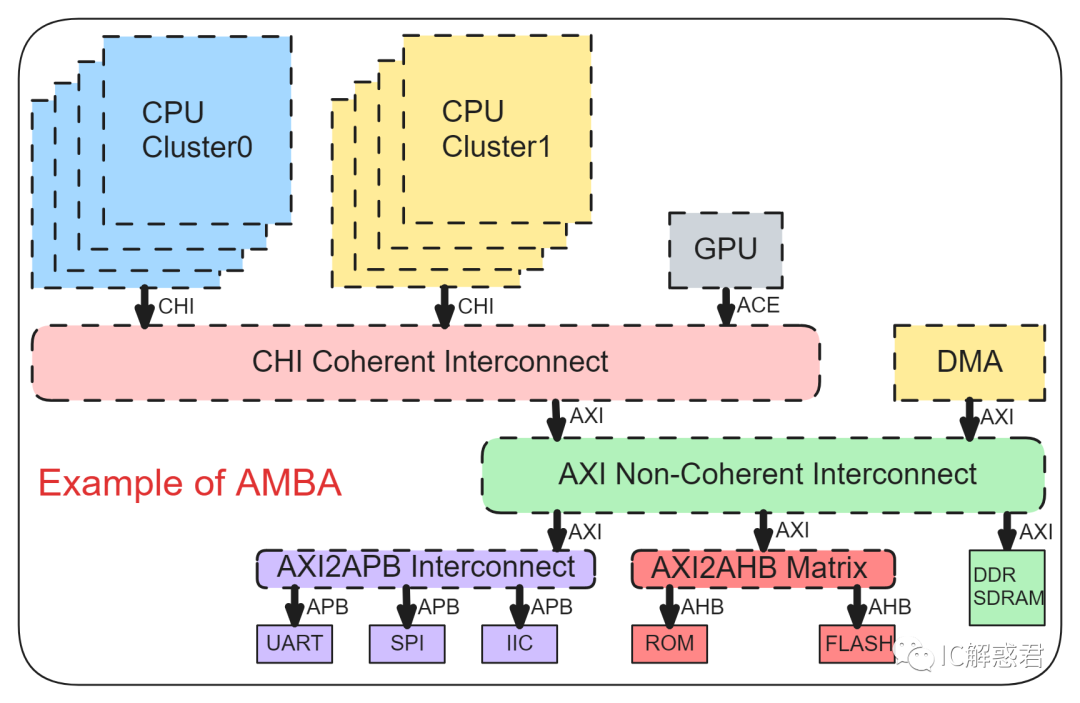

如上图所示的SoC设计实例。通过AMBA协议连接了各个功能模块,比如CPU、GPU、DMA、DDR等。AMBA协议通过简化和规范了模块接口信号,使得IP设计更加灵活兼容的同时也促进了IP的多次复用。

1.3 This text Focus on

本文主要集中在AMBA协议中的AXI4协议。之所以选择AXI4作为讲解,是因为这个协议在SoC、IC设计中应用比较广泛。

2.1 Brief Introduction of AXI4

AXI协议描述了单向数据传输的过程,在使用AXI协议构建的系统中,有两种AXI接口:Manager(Master)、Subordinate(Slave)。AXI Manager接口只能和AXI Subordinate接口连接。AXI Manager(AXI_M)接口发起AXI读写命令,AXI Subordinate接口接收到AXI读写命令之后给出响应。

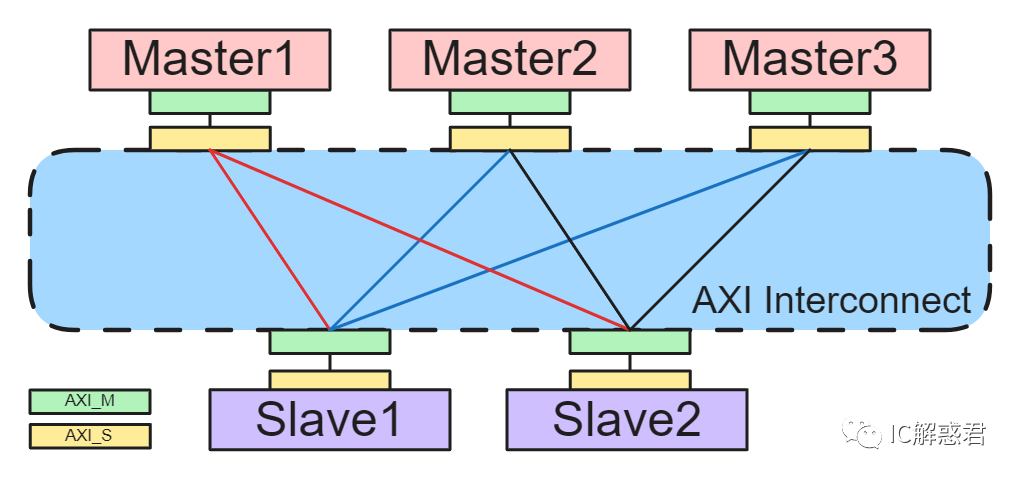

AXI协议是一个点对点接口规范,而不是SoC互联总线协议。所以如果想要连接多个AXI Master和多个AXI Slave时,就需要实现互联总线结构。如下图所示:

上文提到,AXI协议本身只规定了点对点接口之间的信号个数、时序特性。所以上图多个Master的AXI Interconnect模块只是在接口上遵守了AXI协议,互联总线内部的拓扑结构、仲裁机制、路由机制、流控机制等和AXI协议本身没有关系,取决于设计者的思路和应用场景。

PS : 可以用Synopsys DesignWare 、Arm Socrates等工具生成符合应用场景(PPA)的AXI接口的互联总线。

2.2 AXI Channel Overview

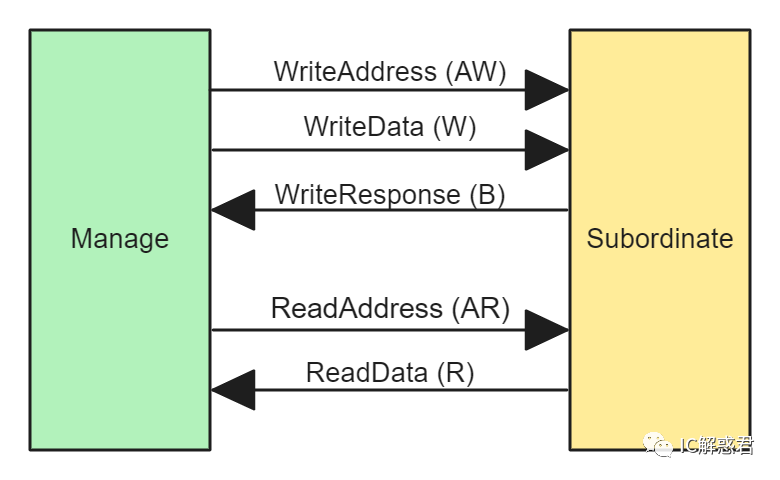

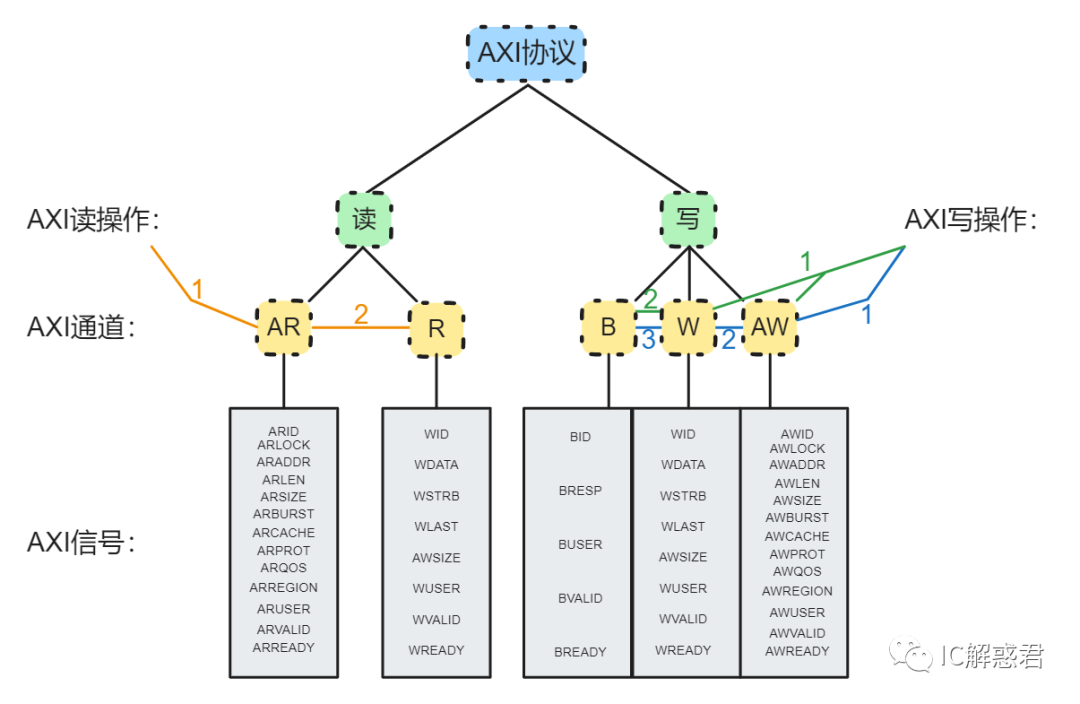

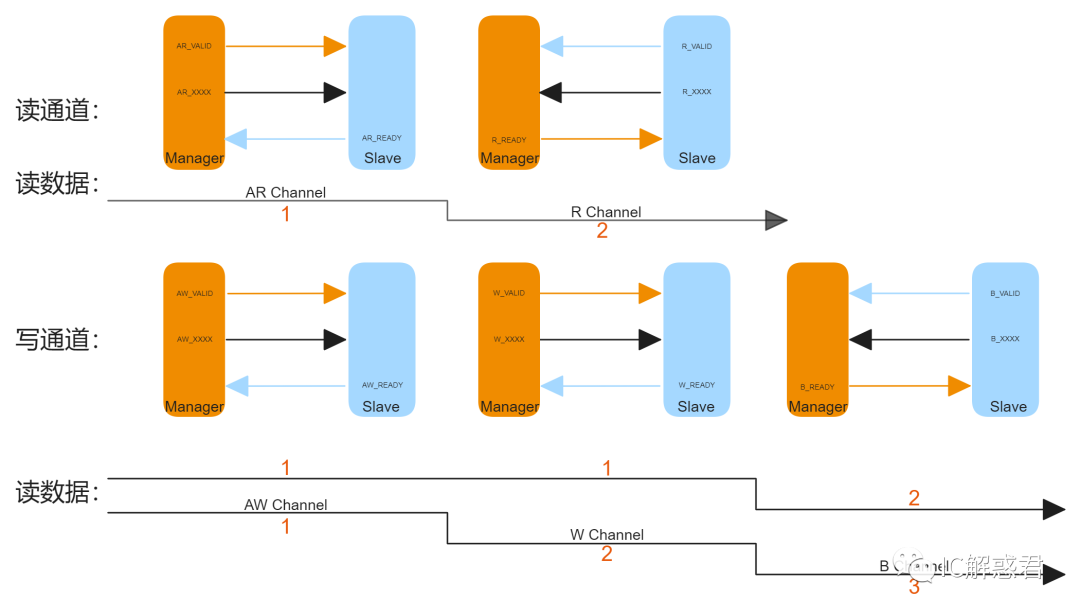

AXI协议规定了AXI Manager和AXI Subordinate之间点对点的信号个数、时序特性。AXI协议用于AXI Manager和AXI Subordinate接口之间数据的传输。AXI协议将所有的信号分成五个通道,分别是写地址通道(AW)、写数据通道(W)、写响应通道(B)、读地址通道(AR)、读数据通道(R)。如下图所示:

写数据: 1. Manager 通过Write Address(AW)通道向Subordinate发出想要写数据的地址 2. Manager 通过Write Data(W)通道向Subordinate发出写数据

3. Subordinate收到地址和数据后完成写入操作,并通过Write Response(B)通道告诉Manager当前的地址和数据写入是否成功(写响应) 读数据: 1. Manager 通过Read Address(AR)通道向Subordinate发出想要读数据的地址

2. Subordinate收到地址后,通过Read Data(R)通道向Manager返回需要的数据(读数据)。

PS : AXI Manager在发起写操作的时候,可以先发写地址,再发写数据,最后等待写响应。同时,AXI Manager也可以同时发出写地址和写数据,最后等待写响应,如上图所示。 PS : AXI协议所定义的读写通道并不对称,可以看到写数据包含三个通道(AW、W、B),读数据包含两个通道(AR、R)。因为Slave返回的读命令响应可以伴随着数据一起返回。 2.2 AXI Channel Transfer Overview 上文提到,AXI协议将信号分为五个通道。读写操作需要五个通道的配合完成;对于写操作,需要AW、W、B通道配合。对于读操作,需要AR、R通道配合。 而对于每个通道的数据传输,需要通道内信号在时间上组合来完成数据传输。如下图示,AXI协议中的五个通道,每个通道中都有相同的握手机制。

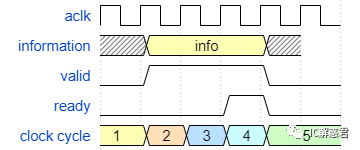

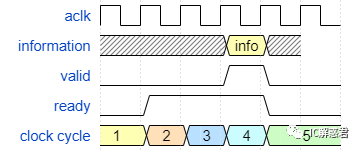

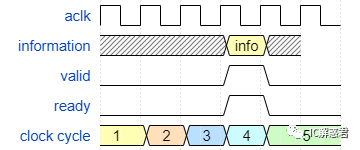

2.3 AXI Channel Transfer Timing Overview 上文提到,AXI协议中的通道的数据传输是依靠握手机制。source通过拉高Valid信号指示有数据发送。而destination拉高Ready信号表示可以接收数据。只有source和destination同时有效,数据才能完成传输。

如图1所示,source有数据发送,在T2周期拉高valid信号并保持发送的数据。在T4周期,destination拉高ready信号表示可以接收数据。数据在T5周期被完整传输。这里的valid和ready同时为1且时长1周期的握手,称为1次Transfer。

如图2所示,在T2周期,destination拉高ready信号表示可以接收数据,此时source并没有数据发送,直到T4周期source有数据发送便拉高valid信号,在T5周期完成一次数据传输(Transfer)。

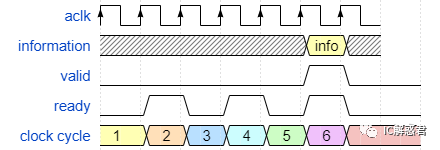

如图3所示,source和destination同时在T4周期作用,完成一次数据传输(Transfer)。

PS : source和destination之间没有任何关系。当source有数据发送,拉高valid信号;当destination可以接受数据,拉高ready信号。source和destination根据自己的情况拉高信号向对方表明意图。

PS : 为了避免死锁产生,需要遵从source不能根据destination的ready信号来操作valid信号,但是ready信号可以根据valid信号来设置。举例来说,source和destination可以认为是谈恋爱的双方:

1. source可以主动表达自己心意,destination也可以主动表示自己心意,两者没有依赖关系可以达到目的。

2. source可以向destination表达自己心意,destination根据source表达过来的心意可以回复source也能达到目的。

3. 当source等待destination主动表达心意,destination也等待source主动表达心意,没有人主动表达自己的心意,那么就会陷入互相等待形成死锁(事则不成)。

PS : source有数据发送时,拉高valid信号。此时source只有等待destination接受这笔数据才可以拉低valid信号(图1)(发数据要慎重,一旦发起必须等到对方接受才能恢复,即valid: 发数据,须慎重,一旦发,必须接,接完后,才能动)

PS : destination比较灵活,可以根据自身情况拉高拉低ready信号。但是当valid为1时,destination拉高ready信号时,必须接受这笔数据才可以拉低ready信号(ready: 接数据,随意动,源有效,必须接,接完后,才能动)。如下图,在T2、T4周期使用ready表示自己可以接收数据,但在下一周期又认为自己接受不了而拉低ready信号。在T6周期,valid和ready都拉高的时候,必须接收这笔数据才能进行下面操作。

2.4 AXI Channel Transcation Timing Overview

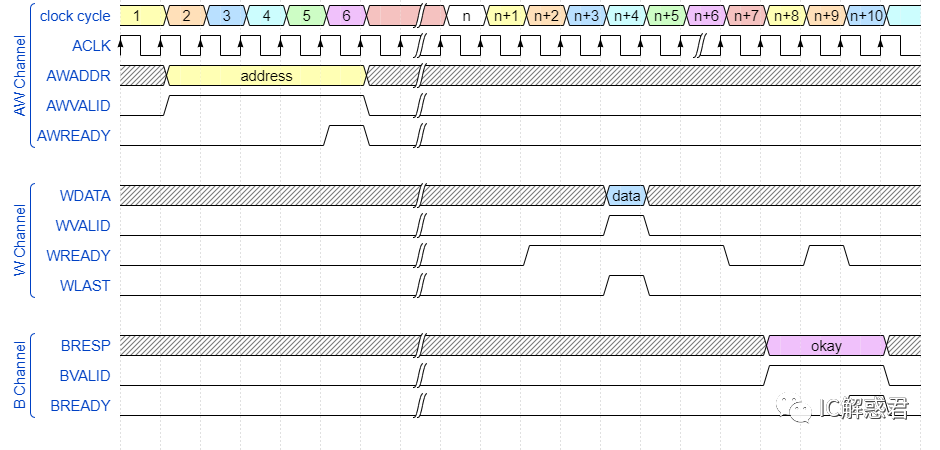

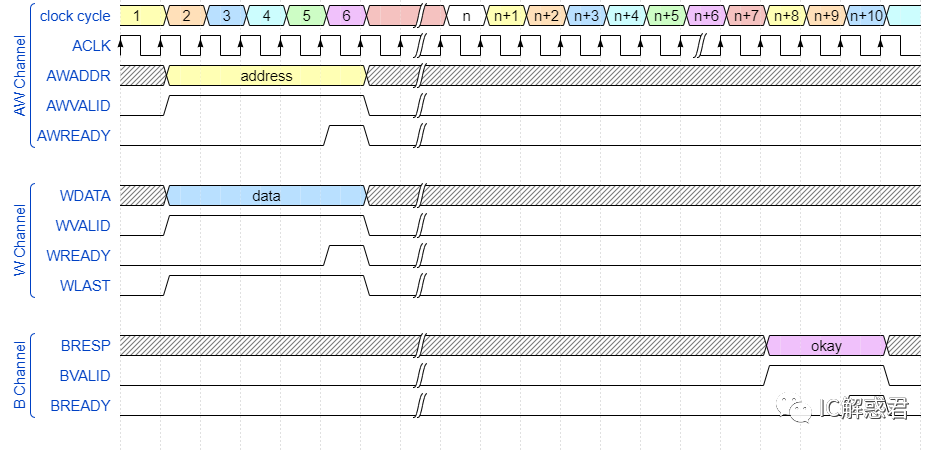

2.41 Write Transcation : single data

写操作时序图1:单数据

如上文所示,Manager向Subordinate写数据时,Manager先发送写地址,再发送写数据,最后等待Subordinate的响应。时序图如下:

如上图所示,每个通道传输的数据不一致,但是都通过相似的握手信号来完成数据的交互。从AW通道的地址信号开始,接着W通道的数据到最后的B通道的响应,这一完整的过程称为一次Transaction。

写操作时序图2:单数据

如上文所示,Manager向Subordinate写数据时,Manager同时发送写地址和写数据,最后等待Subordinate的响应。时序图如下:

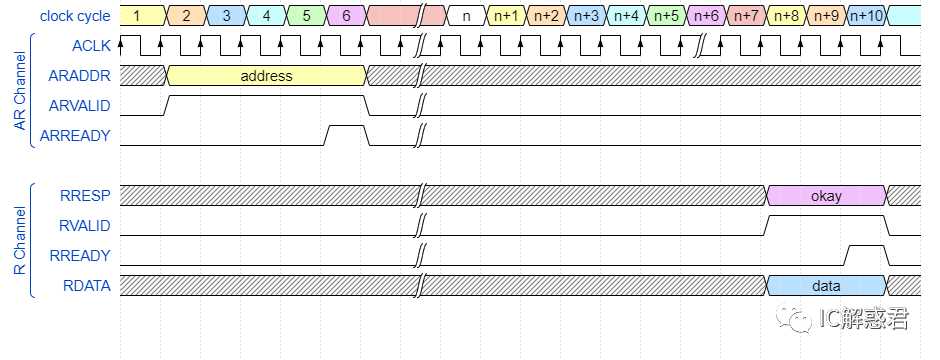

2.42 Read Transcation : single data

读操作时序图:单数据

如上文所示,Manager向Subordinate读数据时,Manager先发送读地址,然后等待Subordinate的响应。时序图如下:

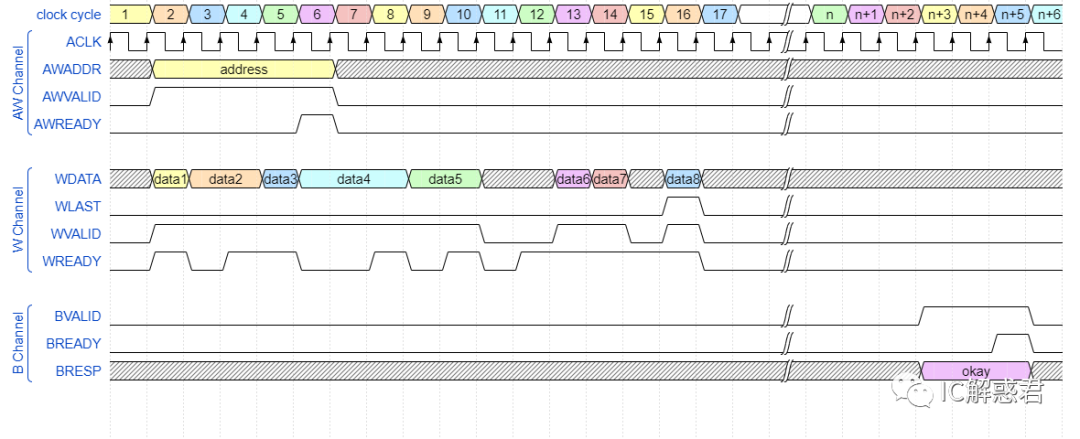

2.43 Write Transcation : multi data

写操作时序:多数据

如上文所示,Manager向Subordinate写多个数据,Manager发送写地址和写数据,等待Subordinate的响应。时序图如下:

在这里,从第一个写数据到最后一个写数据(data1~data8),在一个Transaction中,整个W通道的数据过程称为一次写Burst;写Burst内部每一拍的数据称为一个写Beat。

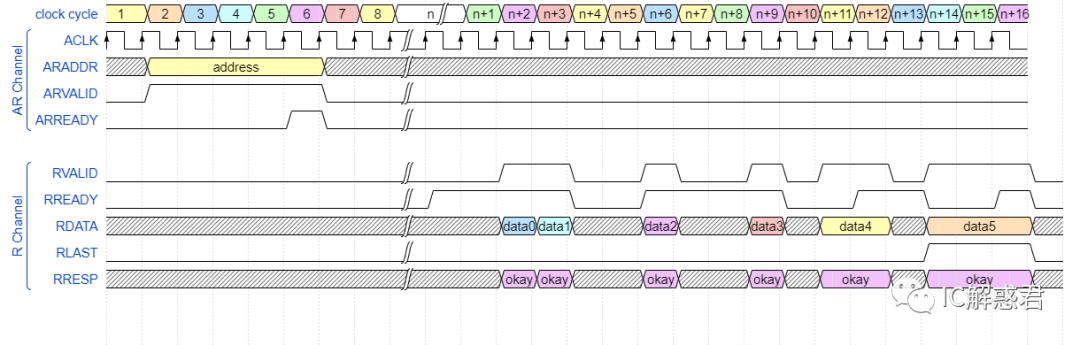

2.44 Read Transcation : multi data

读操作时序:多数据

如上文所示,Manager向Subordinate读数据时,Manager先发送读地址,然后等待Subordinate的响应。时序图如下:

对比读操作和写操作的波形可以明显看出读写通道的不对称。可以看到每一个读数据都有一个匹配的读响应伴随,读响应借助读数据通道返回。而写操作波形图中,有专门的通道(B通道)进行写操作的响应。

写响应在写数据操作完成之后返回一个写响应,而对读操作来说,伴随着每个数据都有一个读响应。这也能体现两者不对称。

在这里,从第一个读数据到最后一个读数据(data0~data5),在一个Transaction中,整个R通道的数据过程称为一次读Burst;读Burst内部每一拍的数据称为一个读Beat。

这也就是AMBA spec提到的AXI协议是基于Burst的传输(The AXI protocol is burst-based)。

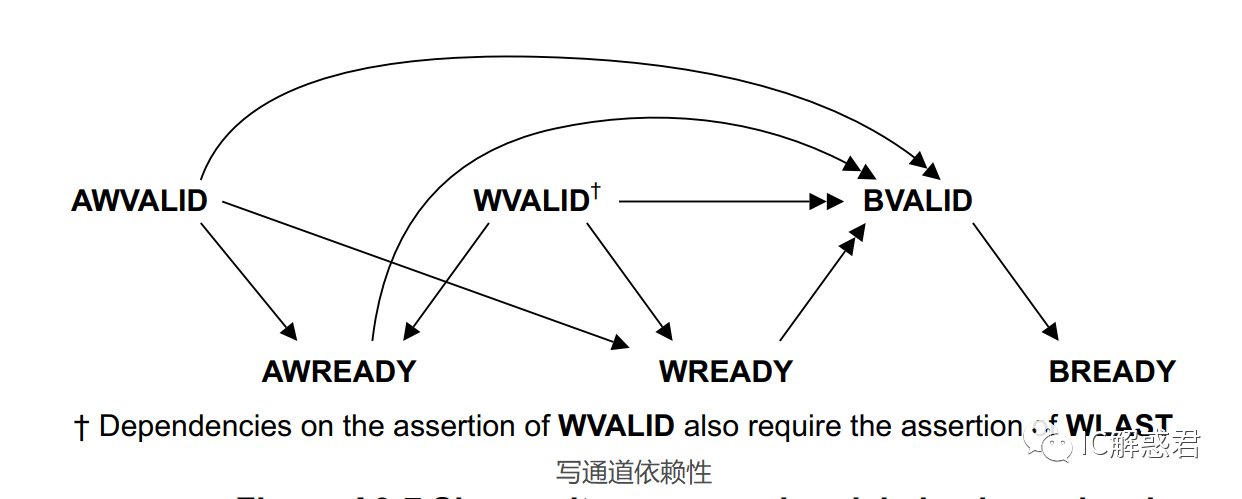

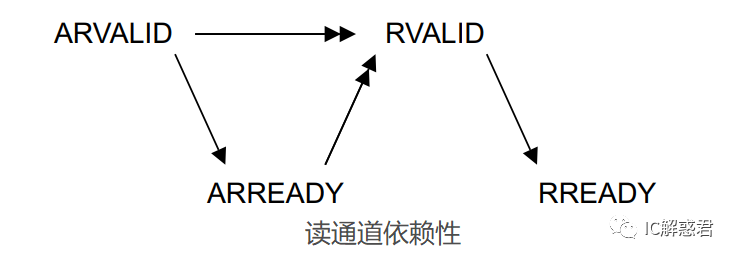

3. AXI Channel dependencies

虽然这一节会提及通道依赖性,但其实来说,通道依赖性已经在上文中完整体现,即:

1.写通道的依赖性:写操作由地址和数据开始,到写响应完成。这就定义了第一条依赖性:写响应要在地址和数据之后。

2.读通道的依赖性:读操作由读地址开始,到读数据和读响应完成。这就定义了第二条依赖性:读数据和读响应要在读地址之后。

上面通道依赖性很好理解,只有当slave收到命令之后才能给出响应:对于写通道的依赖性就是写地址和写数据都到达slave,这时候slave完成写操作并给出写响应。对于读通道的依赖性就是读地址到达slave后,slave返回读取的数据和读响应。如下AMBA spec原图所示:

除过上图所示的依赖特性,在AXI4协议里面没有规定其他任何的依赖关系。

审核编辑:黄飞

-

NVMe IP之AXI4总线分析2025-06-02 6191

-

AMBA AXI4接口协议概述2024-10-28 1736

-

SoC设计中总线协议AXI4与AXI3的主要区别详解2024-05-10 13940

-

AMBA3.0 AXI总线接口协议的研究与应用2023-09-20 921

-

SoC Designer AXI4协议包的用户指南2023-08-10 742

-

学习架构-AMBA AXI简介2023-08-09 1036

-

Xilinx FPGA AXI4总线(一)介绍【AXI4】【AXI4-Lite】【AXI-Stream】2023-06-21 3241

-

AXI4-Lite协议简明学习笔记2023-06-19 5947

-

FPGA AXI4协议学习笔记(二)2023-05-24 3028

-

看看在SpinalHDL中AXI4总线互联IP的设计2022-08-02 3292

-

AMBA 3.0 AXI总线接口协议的研究与应用2021-04-12 1202

-

深入AXI4总线一握手机制2021-03-17 1266

-

ZYNQ中DMA与AXI4总线2020-11-02 5276

-

AXI4接口协议的基础知识2020-09-23 7221

全部0条评论

快来发表一下你的评论吧 !