用于连接去耦电容器的过孔配置

PCB设计

描述

时钟数字IC通常需要大的瞬态电源电流。例如,大型微处理器可以在很短的时间内消耗高达 10 A 的电流。随着 IC 输出的上升/下降时间缩短,我们需要以更高的速率提供瞬态能量。PCB 的电源和接地导体确实存在一定的电感。如果数字 IC 的大瞬态电流流过电源和接地导体的电感,则会在电感上产生电压。由于电源和接地导体上存在较大的瞬态电压降,我们无法在 IC 的电源和接地焊盘上提供恒定电压。

解决上述问题的方法是提供能够提供瞬态电流的电荷源。这通常是通过将去耦电容器放置在非常靠近每个逻辑 IC 的位置来实现的。我们应该始终记住,电路电源布线仅补充去耦电容器中的电荷,并且应该由去耦电容器提供所有高频瞬态电流。去耦电容器在与 IC 输出的上升/下降时间相关的短时间间隔内提供瞬态电流,并且电源具有至少半个时钟周期来对去耦电容器进行再充电。将高频能量远离配电走线使我们能够更轻松地承受配电结构中不可避免的电感。

去耦环路的电感

如上所述,我们使用去耦电容器来避免通过配电走线提供高频电流,这会表现出高电感。这就是为什么连接去耦电容器和 IC 的路径电感也很重要。如果去耦环路的电感不够小,逻辑IC就会尝试通过功率分配结构来获取其部分高频能量。因此,我们需要仔细检查去耦环路的电感,并尽一切可能将其化。请参考这篇文章了解减少去耦环路电感的重要技术。在本文中,我们将重点介绍可用于将去耦电容器连接到 PCB 电源层和接地层的不同过孔配置。

过孔承载相反方向的电流

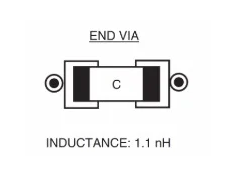

安装去耦电容器的传统方法是将过孔放置在电容器焊盘旁边,如图 1 所示。

图 1.图片由电磁兼容性工程公司提供。

对于这种情况,从电容器的安装焊盘到电源接地平面对的总电感的典型值约为 1.1 nH。为了减少这些过孔的总电感,我们可以将它们靠近在一起。将过孔靠近在一起会增加它们之间的互感。

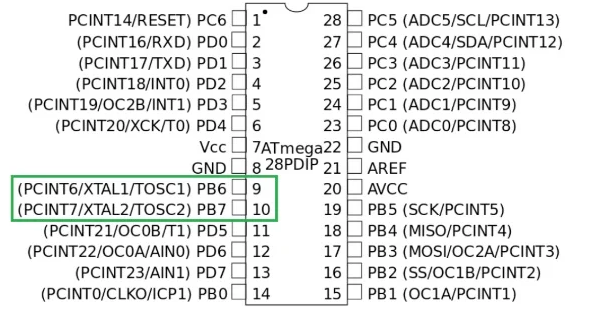

由于这两个过孔的电流流向相反,因此增加的互感将减小每个过孔的净电感。为了更好地理解这一点,请记住流经电感器的电流会产生环绕导体的磁力线。这些磁力线的方向可以通过图 2 所示的右手定则找到(在本例中,电流方向为向上)。

图 2.使用的图像由Signal and Power Integrity-Simplified提供。

当电流通过通孔时,会产生围绕通孔的磁力线。一个通孔的一些磁力线也将环绕另一通孔。

由于两个过孔产生相反方向的磁场(参见图 3),因此它们之间的磁耦合实际上会减少围绕每个过孔的磁力线总数。导体周围的净磁力线数量决定了其电感。因此,当我们的通孔承载相反方向的电流时,增加它们之间的磁耦合将减少每个通孔表现出的有效电感。

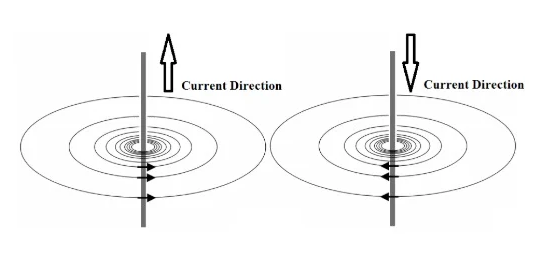

因此,降低去耦环路电感的一种技术是将过孔靠近在一起,如图 4 所示。在这种情况下,电容器的安装焊盘与电源-接地平面对之间的电感降低至 0.7 nH 。

图 4.图片由电磁兼容性工程提供。

过孔承载相同方向的电流

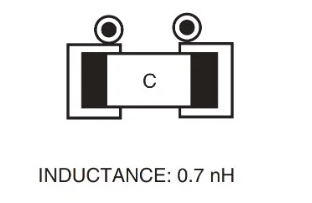

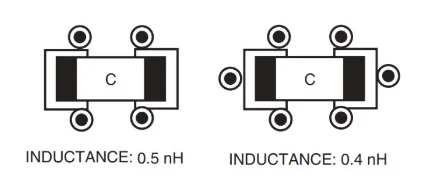

为了进一步降低去耦环路的电感,我们可以对每个电容器焊盘使用多个过孔,而不是仅使用一个过孔。图 5 显示了两种可能的布置。

图 5.图片由电磁兼容性工程提供。

如果连接到同一焊盘的过孔之间没有互感,我们可以很容易地得出结论,并联过孔的等效电感将与过孔的数量成反比。如果它们之间存在互感怎么办?

通过连接到同一焊盘的过孔的电流方向相同。与图 3 中的情况不同,图 5 的平行通孔之间的磁耦合将增加围绕每个通孔的磁力线总数。因此,当我们有承载相同方向电流的过孔时,增加它们之间的磁耦合将增加每个过孔表现出的有效电感。

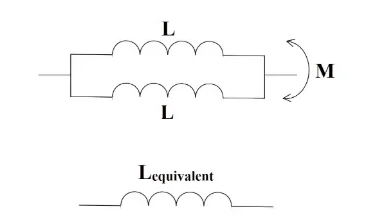

让我们考虑每个焊盘有两个过孔的布置(上左图)。假设每个过孔的自感为L,并联过孔之间的互感为M(下图6)。等效电感值是多少?

图6

考虑到两个过孔的磁力线方向相同,

互感 M 不能大于自感 L。因此,在坏的情况下,[L_{equivalent}] 接近于 L。但是,如果我们将连接到同一焊盘的过孔放置彼此之间足够远,我们可以显着减小互感M并获得接近[frac{L}{2}]的等效电感。

通常假设,如果过孔之间的中心间距大于过孔的长度,则互感变得远小于自感。在这种情况下,过孔的等效电感几乎与过孔的数量成反比。

使用多个过孔的另一个优点

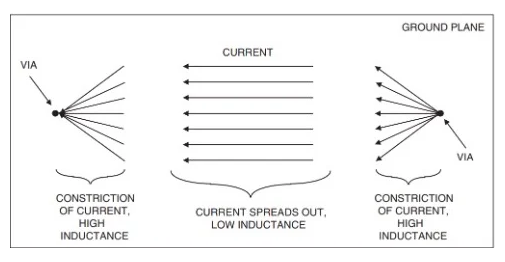

我们看到,通过多个过孔,我们可以获得与过孔数量成反比的等效电感。还有另一种机制可以使图 5 的布置具有较低的电感。为了理解第二种机制,我们需要考虑当电流通过通孔馈入或流出平面时平面中的电流分布。如图7所示,在过孔附近,电流被限制通过过孔流入或流出平面。当我们远离过孔时,电流会扩散。

图 7.图片由电磁兼容性工程提供。

检查平面的电感可能是一个复杂的问题,超出了本文的范围。您可以在《电磁兼容性工程》一书的第 10 章中找到一些详细信息。重要的一点是,远离过孔,电流可以扩散,并且平面呈现出低电感。然而,在过孔附近,电流无法扩散,并且路径的电感显着增加。

有趣的是,图 7 中所示的电流分布的总电感将主要由过孔附近的大电感决定。图 5 的布置使用多个过孔连接到平面。因此,与使用单通孔的配置相比,多通孔配置允许电流在平面的更广泛区域中扩散。因此,多个通孔可以减小通孔附近的平面的电感,并且因此减小去耦环路的电感。

结论

我们使用去耦电容器来避免通过配电走线提供高频电流,这会表现出高电感。如果去耦环路的电感不够小,逻辑IC就会尝试通过功率分配结构来获取其部分高频能量。因此,我们需要化去耦环路的电感。在本文中,我们讨论了可用于将去耦电容器有效连接到 PCB 电源层和接地层的不同过孔配置。我们看到,我们应该将具有相反方向电流的通孔靠近在一起,并且在适当的间距下,多通孔配置可以产生与通孔数量成反比的等效通孔电感。

-

超级电容器和普通电容器的区别2024-09-27 4267

-

并联电容器采用什么连接方式2024-08-16 4304

-

什么是电力电容器,电力电容器的基本知识介绍2024-01-06 4766

-

并联电容器和串联电容器的作用2023-09-04 13558

-

在去耦电容器和PCB上的高速数字IC之间建立高性能连接2023-04-14 1238

-

去耦电容器的作用及放置问题2020-12-23 4933

-

去耦电容器应该如何正确放置2020-11-14 5260

-

最有效的去耦电容器放置指南2020-09-29 4977

-

并联电容器如何连接2019-06-23 31665

-

去耦电容器是否真的有必要?2018-12-26 1585

-

输出电容器的配置2018-11-29 1778

-

去耦电容器它的作用到底是什么?2018-09-20 1944

-

去耦电容器的应用解决方案2014-09-16 2279

-

电容器的作用2013-07-22 4641

全部0条评论

快来发表一下你的评论吧 !