100kW碳化硅三相并网逆变器设计

描述

文章来源:电网技术

作者:邓宇杰1,杜燕1,曾磊磊2(1.合肥工业大学电气与自动化工程学院,2.国网江西省电力有限公司电力科学研究院)

摘要:随着人们环保意识的不断提高,传统的化石能源越来越无法满足人们的要求,以太阳能为代表的可再生新能源逐渐引起人们的关注。而并网逆变器作为新能源与电网连接的关键一环,其性能对于整个电网系统都起着至关重要的作用。传统的光伏并网逆变器通常采用IGBT器件,但由于该种器件的开关速度受到电导调制效应影响,使得逆变器的开关频率难以提高,这就限制了光伏逆变器效率和功率密度的提升。与传统的 Si 器件相比,基于SiC MOSFET器件的耐压更高、导通电阻更低,并且器件结电容、门极电荷量更小,所以可以达到更快的开关频率,利于提高效率。文中主要进行了碳化硅三相并网逆变器的硬件电路设计,包括主电路参数的设计以及驱动电路的设计,并在MATLAB上进行开环仿真验证。从损耗分析的角度说明了SiC器件相比于Si器件的优势,得出了SiC器件在相同损耗下的开关频率更高的特点。

0 引言

根据“十四五”现代能源体系规划可知,在“十三五”期间,我国的太阳能发电装机总量就达到了2.5 亿 kWp。而“十四五”时期是为力争在 2030 年前实现碳达峰、2060 年前实现碳中和打好基础的关键时期,加快能源系统调整以适应新能源大规模发展,推动形成绿色发展方式和生活方式。由此可见,太阳能光伏发电的潜力远不止于此,仍然大有可为。

并网逆变器在电网与光伏发电系统的连接中起着不可或缺的作用。为保证整个光伏并网系统的稳定,对光伏并网逆变器的性能也有了越来越严格的要求。因此,在光伏并网逆变器基础趋向成熟的同时,开始要求其拥有更高的效率、更高的功率密度。

人们对于光伏并网逆变器的早期应用选择的是绝缘栅双极型晶体管(Insulated-gate Bipolar Transistor,IGBT)或者是金属氧化物半导体场效应晶体管(Met‐al Oxide Semiconductor Feild Effect Transistor,MOSFET)。作为传统的晶体管,他们的使用场合随着技术的更新迭代以及自身的局限性变得越来越少。同时,电力电子装置在当今的发展潮流中有着更高的要求,带隙能量、热导率及电子漂移等物理特性成为制约电力电子器件的主要因素。倘若无法满足“轻小快”等各类要求,此类装置终将会被时代所淘汰。最常规的Si MOSFET器件,其开关速度快,但是这种非高耐压装置并不适用于高电压大电流的环境。而由于电导调制效应,另一种 IGBT 导通压降很小,因此能够胜任Si MOSFET不适用的场合。然而与之相反的是,IGBT开关频率最高仅为Si MOSFET的三分之一,开关速度更慢,实际应用开关频率仅为 10 kHz~20 kHz 左右。然而常见的电网往往是高压电,只能考虑开关频率较低的 IGBT器件,这就造成了逆变器功率低下的问题。正是由于这些器件材料的局限性,导致光伏逆变器的性能很难在不变换器件的前提下获得提升。因此,新型宽禁带半导体器件就成为了重要的突破口,例如目前主流的碳化硅(SiC)、氮化镓(GaN)等器件。而对于这种新型材料的半导体器件例如碳化硅器件,其主要优势就在于:

1)SiC 材料的临界击穿强度约为 Si 的 10 倍,这说明了 SiC 材料的耐压更高。

2)SiC MOSFET 的开关过程中不存在电导调制效应,所以这比 Si IGBT 的开关速度更快,更适用于高频场合。

3)SiC MOSFET 的导通电阻比更小,这也就意味着损耗更低,可以提高效率。

4)由于SiC材质具有较高的热传导性能,因此可以有效地减小其体积和质量,进而增加其功率密度。

1 主电路设计

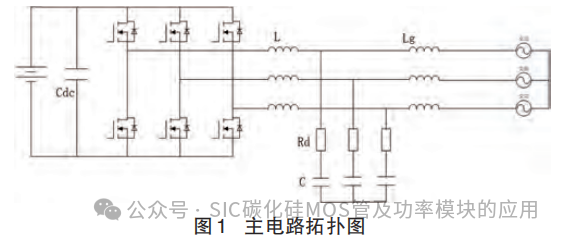

1.1 拓扑选型

在文中的设计中,逆变器主电路采用的是三相全桥拓扑结构,如图1所示。滤波器采用的是LCL 型滤波器。阻尼方式采用电容支路串联电阻的无源阻尼方案实现对 LCL 滤波器谐振的抑制,这对整个系统的稳定起到了很好的作用。

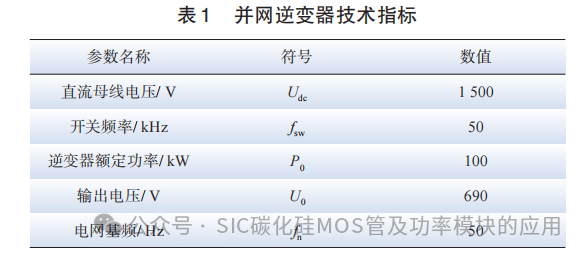

三相并网逆变器的工作条件如表 1 所示。由此展开对100 kW碳化硅三相光伏并网逆变器硬件电路的设计。

1.2 开关管设计

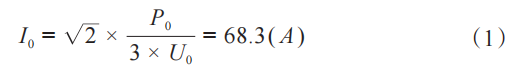

额定功率为 100 kW,根据电压有效值 U0=690 V算出电流峰值

逆变器开关管的最高耐压即为母线电压 Udc=1 500 V,由于选型中需要满足 1.5~2 倍的通态平均电流,故文中选择 GeneSiC Semiconductor 公司生产的 G2R50MT33K,该 型 号 的 最 高 耐 压 为 3 300 V,25 ℃条件下额定工作电流 101 A,100 ℃下额定工作电流67 A,满足要求。

1.3 滤波器设计

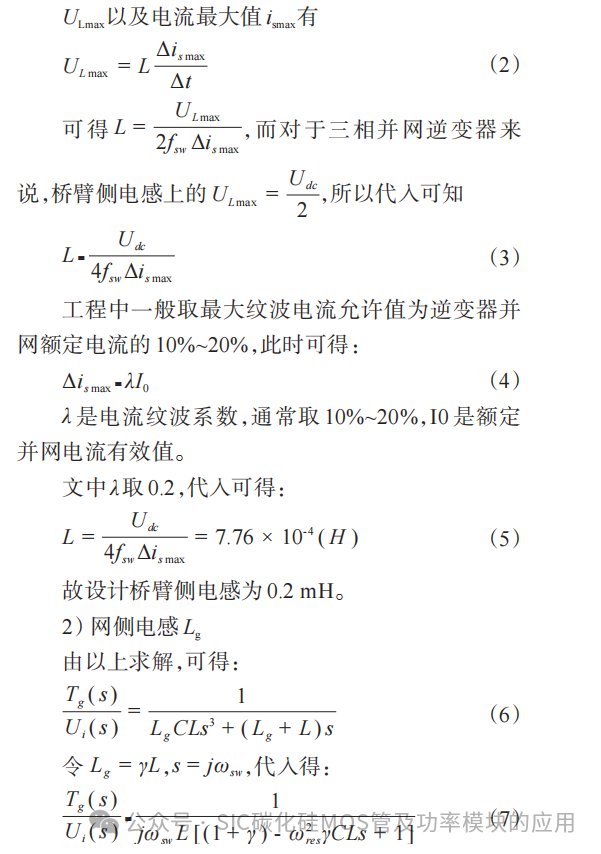

1)桥臂侧电感L对于桥臂侧电感上的电压最大值

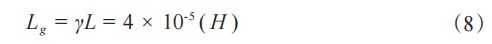

故γ 可调节 LCL 滤波器衰减比列,太小的 γ 会使衰减效果变差,太大的 γ 会使成本增加,工程上一般取γ ≤ 0.05,在设计时,可计算得到网侧电感值。然后再验证总电感值以及 LCL 谐振频率是否满足要求,如果不满足要求需要重新选择衰减比例或者滤波电容的值计算,直到满足要求为止。

在文中设计中,取γ = 0.2,可计算得:

故设计网侧电感为40 μH。

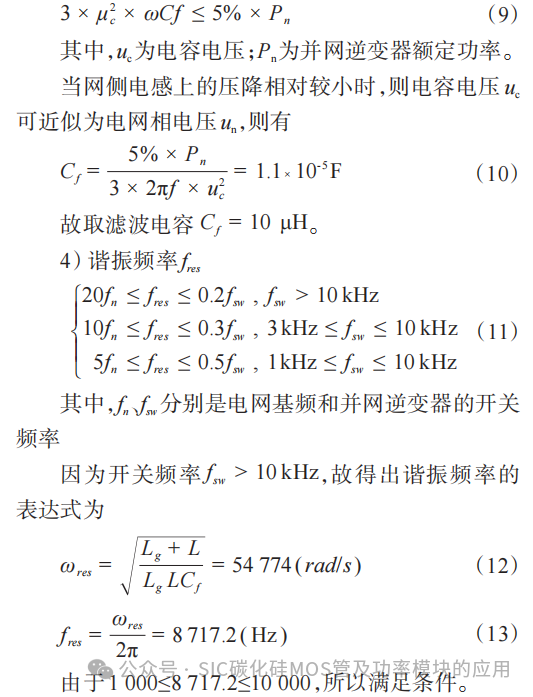

3)滤波电容Cf

工程上通常要求电容产生的无功功率不超过5%的系统额定功率,故有

5)无源阻尼电阻Rd

根据前文所述,文中采用的阻尼策略是电容支路串联电阻的无源阻尼法,所以要进行阻尼电阻的设计。而阻尼电阻 Rd的结构,则必须兼顾系统阻尼与损失。

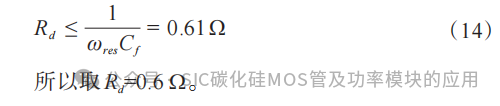

在 LCL 滤波器参数的设计中,阻尼电阻的取值一 般 不 超 过 谐 振 角 频 率 处 滤 波 电 容 Cf 容 抗 的1/3,即

2 驱动电路设计

2.1 驱动电源设计

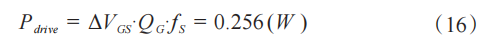

由 GeneSiC Semiconductor 器件手册得知,SiC MOSFET 栅极驱动电荷 QG为 256 nC,当驱动电路开关频率为 50 kHz,驱动正向电压为+15 V,驱动负向电压为 -5 V时,理论计算的驱动功率为:

其中,ΔVGS是驱动正向电压和负向电压差值,QG为栅极电荷,fs为开关频率。故选择6路 QA01C电源进行驱动,具有20 V/-4 V两路输出,可以很好地提高开通和关断能量。

2.2 驱动芯片设计

基于碳化硅逆变器的驱动电路设计一般有两种隔离方式:光耦隔离和磁隔离。光耦隔离的基本原理是利用光作为介质,将输入和输出信号分离开来。这种方法不仅节约了成本,提高了传输效率,还提高了对EMI的抗干扰能力。磁绝缘利用变压器将输入和输出信号分离,这种隔离方式虽然传输速率较高,但是抵抗电磁干扰能力弱,而且在高频环境下易出现变压器磁饱和现象。

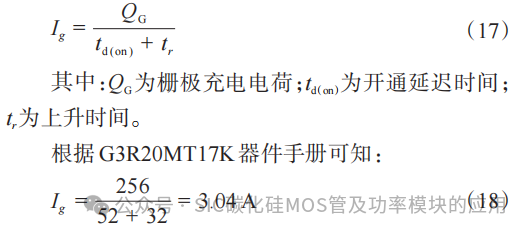

在驱动电路设计时,驱动芯片应该提供足够的驱动电流,当该电流不足时,会导致器件开关过程延时,从而使得开关过程的损耗增加。因此,根据式计算出开通过程需要的平均驱动电流Ig为:

故平均驱动电流为 3.04 A,因此从隔离方式、驱动电流两个方面考虑后选择 Infineon 公司生产的SiCMOSFET 栅极驱动器 1EDC60I12AHXUMA1,该驱动芯片采用 Infineon特有的无铁芯变压器技术,最高能够达到 3000 V 的隔离电压等级,同时该驱动芯片最高可以输出 10 A 的峰值驱动电流,能够驱动SiCMOSFET快速动作。

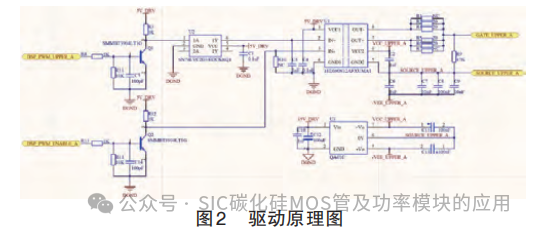

2.3 驱动电路原理

首先对驱动芯片 1EDC60I12AHXUMA1 做简单介绍,该驱动芯片采用 PG-DSO-8-59 封装形式,逻辑输入引脚支持 3~15 V 的宽电压范围,可以直接连接到 DSP或者其他微处理器的输出引脚。芯片的逻辑输入引脚,驱动输出引脚都具有欠压锁定(UVLO)功能,可以确保更可靠的开关动作。1EDC60I12AHX-UMA1的引脚定义如表2所示。

驱动芯片 1EDC60I12AHXUMA1 的逻辑信号侧电源 VCC1具有较宽的工作电压范围,在 3.3~15V 之间。2、3个脚均可用作PWM信号的输入端,当PWM信号采用 IN+管脚时,IN-应该与低电平相连,这时IN+是高电平,输出是高,IN+是低压,而输出是低压,而驱动是低压。如果将 IN-管脚用作 PWM信号的输入,则IN+应该被连接至高电平,在该情况下IN-是高电平,而驱动输出是低电平,IN-是低电平,而驱动是高电平,从而实现低通断逻辑。通过这两个引脚的特点,可以实现硬件过流保护。

如图 2 所示,左侧为 DSP 的 PWM 和硬件的过电流保护。在高频率切换时,系统的电磁干扰较大,会对驱动信号产生较大的影响,为了提高系统的可靠性,必须对驱动电路进行抗干扰。PWM 信号首先通过三极管,这不仅可以改善 PWM 信号的驱动性能,还可以降低 DSP直接输入的驱动电流。而三极管是一种电流驱动的装置,其电流信号的抗干性要高于电压信号。通过三极管驱动电路,将 PWM信号输入到施密特触发反向器中,施密特触发器具有正、负两种阈值电压,对信号进行整形滤波,从而进一步增强了系统的抗干扰性。最终,PWM 信号与驱动芯片 IN+管脚相连接。通过三极管驱动电路,硬件过流保护信号与驱动晶片 IN-插头相连接。通常,硬件的过流保护信号是高电平的,三极管是开通的,IN-是接地的。当出现过电流时,保护信号跳到低电平,三极管关闭,IN-引脚与高电平相连,这时,无论 IN+输入是高还是低,驱动芯片的输出均处于低电平状态,从而使该装置能够达到过电流保护的作用。

3 MATLAB开环仿真

为了验证是否可以输出满足并网要求的并网电流,以及之前设计的LCL型滤波器的参数是否可以满足滤波要求,故需要在MATLAB中进行开环仿真验证。

3.1 仿真模型

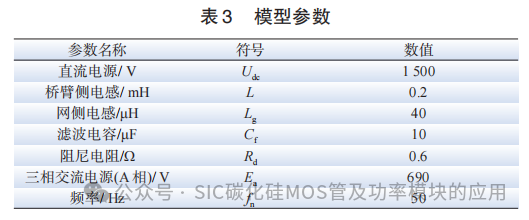

通过之前的设计分析,搭建模型。仿真模型主要有直流电源输入模块、并网逆变器模块、SPWM 发生器模块、具有滤波功能的 LCL滤波器模块,最后再接入三相交流电源形成模型,如图3所示。对应其中的参数如表3。

3.2 结果分析

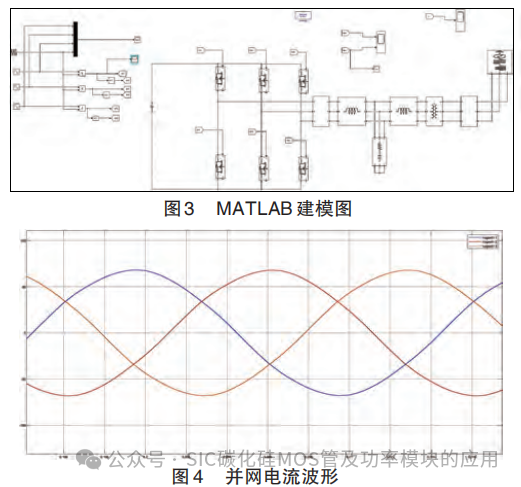

该次实验目的:观察 LCL 滤波器参数设计是否合理。

通过前文搭建的模型,输出功率为100 kW,输出电压为 690 V,计算可以得出输出电流峰值为 68 A,电流波形如图4所示。

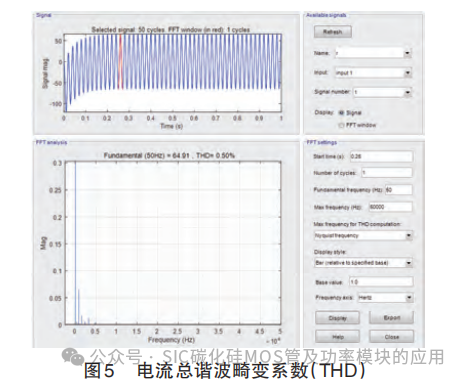

工程上一般来说THD≤5%,如图5可以看出THD=0.5%<5%,所以满足条件。

根据图4和图5,可以得到以下结论:

1)直流母线电压可以输出满足要求的并网电流;

2)设计的LCL滤波器参数可以达到很好的滤波效果。

4 损耗分析

功率半导体器件多数工作于不断开关过程,在导通过程以及开关过程都会产生损耗。过大的损耗不仅会降低系统的运行效率,还会造成大量的发热,造成温度过高,严重地影响到设备的运行。因此,开关器损耗问题成为目前国内外研究的一个重要课题。在系统设计、寿命判断、选择合适的散热系统、提高系统的可靠性方面,均具有十分重要的意义。MOSFET的功率损耗主要分为导通损耗与开关损耗。

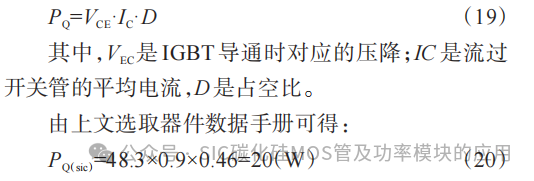

4.1 MOSFET导通损耗

电力电子器件在通态下,由于存在一定的通态电阻,经过电流流通时,在电阻两端会产生导通压降,从而产生了导通损耗。导通损耗的大小由流过器件的电 流 与 导 通 压 降 的 乘 积 大 小 所 决 定 ,其 计 算 公式为:

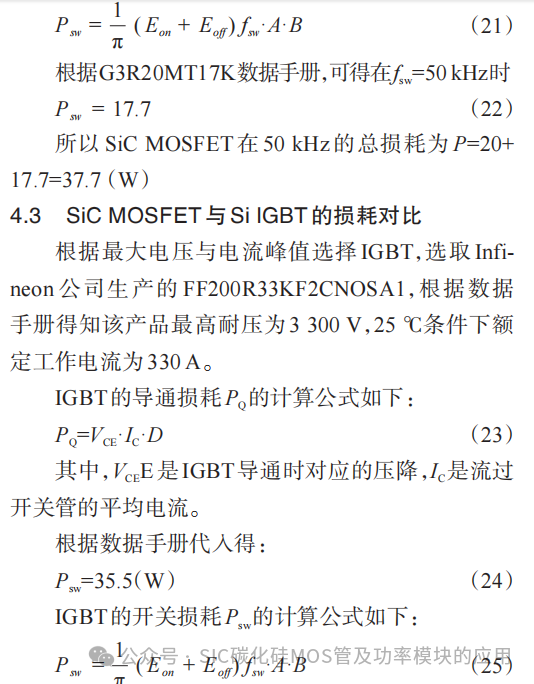

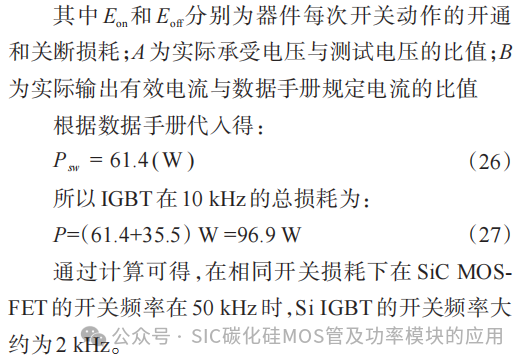

4.2 MOSFET开关损耗

在电力电子电路运行过程时,总是伴随着相应的电力电子器件的开启和关闭,从而导致了开关损耗的发生。随着新设备、新技术的发展,以及电力电子学逐渐走向高频率,开关损耗是决定设备整体效能的关键因素。

开关损耗是在MOSFET的开断过程中,因MOSFET的工作电压、电流都会对 MOSFET施加影响,从而导致 MOSFET 的开关重叠时间延长,进而引起器件的损耗。开关损耗Psw的计算如下:

在相同的损耗下可以明显看出 SiC MOSFET 的开关频率要远远高于 Si IGBT的开关频率,在高频特性一方面可以减小谐波对系统的影响,另一方面也可以使系统中的电感和电容等元器件的体积缩小,这使得系统的整体体积相比低频有了质的飞跃,带来了更高的功率密度,同时对于相同的开关频率下 SiC MOSFET器件损耗比 Si IGBT显著降低,可以大大缓解散热问题。

5 结语

文中设计了100 kW碳化硅三相光伏并网逆变器的硬件电路,主要包括以下几个方面的内容:

1)进行主电路拓扑的选取以及主要参数的设计,包括直流侧电容的设计、桥臂侧电感、网侧电感、开关管的设计、滤波电容的设计以及阻尼电阻的设计。

2)设计了 SiCMOSFET 的驱动电路并对采用的驱动芯片、驱动电路原理做了说明。

3)在MTLAB软件中进行开环仿真验证,验证了LCl滤波器参数设计的合理性。

4)对比Si IGBT进行了损耗分析,得出结论:

①在相同的开关频率下,SiC MOSFET器件损耗比Si IGBT显著降低,可以大大缓解散热问题。

②在相同开关频率下,SiC MOSFET的开关频率远远大于Si IGBT,不但可以减少谐波的影响,还可以减小电感和电容等元器件的体积,带来更高的功率密度。

审核编辑:汤梓红

-

高功率密度碳化硅MOSFET软开关三相逆变器损耗分析2025-10-11 1286

-

Wolfspeed 200kW三相逆变器概述2025-08-04 1353

-

三相并网逆变器的工作原理和特点2024-05-17 4412

-

三相并网逆变器系统(光伏发电系统)simulink仿真2023-02-28 1031

-

一个简易的三相并网逆变器2021-11-15 1795

-

碳化硅器件是如何组成逆变器的?2021-03-16 2813

-

关于三相并网光伏逆变器的同步pi控制资料下载2018-04-18 1149

-

LCL滤波的三相并网逆变器电流双环控制策略书.pdf2018-04-16 1461

-

基于虚拟电阻阻尼的三相并网逆变器控制设计_谢宇2017-01-08 1187

-

三相并网逆变器公共耦合点电压控制研究2017-01-05 1023

-

复杂电网工况下三相并网逆变器的锁频环技术_李建文2016-12-31 1147

-

三相并网逆变器微分平坦控制策略2016-12-28 1094

-

三相并网逆变器N线火线的传导整改都不过,问题大概出在哪儿2016-12-12 7328

-

SVPWM技术在三相并网逆变器中的应用及仿真2016-04-13 757

全部0条评论

快来发表一下你的评论吧 !