原子阵列实现容错通用量子计算的前景和挑战

描述

随着量子计算技术的不断发展,原子阵列量子计算作为一种新兴技术,展现出巨大的潜力和优势。近期,该领域取得了重大突破,为通用量子计算的实现迈出了坚实的一步。本文将介绍原子阵列量子计算的核心要素、发展历程、优势以及近期突破的重要意义。

原子阵列量子计算简介

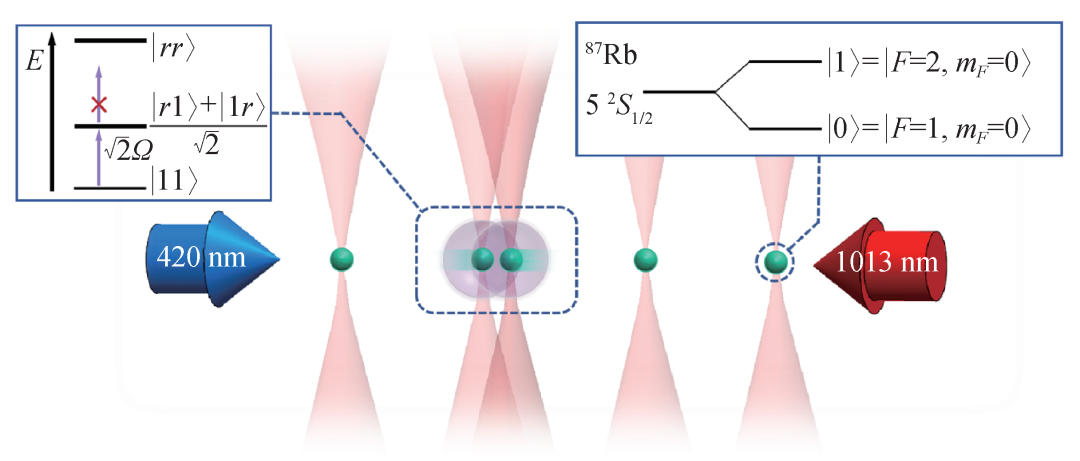

原子阵列量子计算由以下三个核心要素组成(图1):(1)利用原子内态编码量子比特。在使用碱金属原子的阵列实验中,量子比特编码在基态原子的两个磁量子数为零的内态能级上。这两个原子内态之间的相干时间很长,可以达到数秒,该相干性此前已经被广泛应用于原子钟的精密计时;(2)利用光镊束缚和操控原子。光镊可以将原子的空间运动固定,通过可编程的方式控制光镊,使原子在空间上排成阵列。通过移动光镊,可以将任何两个原子移动到一起,进行门操作,可以动态地实现All-to-All的全联通性。这是原子阵列实现量子计算的一大特色;(3)利用里德伯激发进行门操作。里德伯态是原子的高激发态,处于里德伯态的原子具有很强的相互作用,被称为“里德伯阻塞效应”。利用这一效应,两个相距几微米光镊中的原子也产生相互作用,以此可以实现两比特,甚至多比特的量子门操作。

图1 原子阵列量子计算示意图。Rb87原子的两个内态能级被用于编码量子比特,原子被光镊俘获和操控,两个原子靠近后可以通过里德伯相互作用实现两比特门操作(其中|r 〉 代表里德伯态,Ω 代表单个原子激发时的拉比频率)

原子阵列量子计算发展简史

基于原子的量子计算方案始于2000年前后,但初期的方案依赖于单比特寻址,效率和准确率一直不高。相对于超导、离子阱来说,原子系统此前是不被看好的通用量子计算平台,基于冷原子的研究更多地是针对量子多体物理等方面。 研究人员于2016年实现了原子阵列重排。经过多年的努力,直到近两年才有了关键性突破,于2022年实现了具有动态的、全联通性的架构。该架构的主要优势是,不再需要进行单比特寻址的局域操作,而是将需要相互作用的原子用光镊全部移动到一个“纠缠区”(entangling zone),然后当激光均匀地作用于“纠缠区”时,就可以实现高度并行的量子门操作。另一方面,通过不断提高两比特门保真度的不懈努力,2023年4月两比特门保真度达到99.5%,突破了量子纠错码所需要的保真度阈值。这些突破解决了此前制约原子阵列量子计算的瓶颈性问题,开展量子纠错编码的技术条件已经具备。不出所料,2023年12月,研究人员宣布用量子纠错码编码了48个逻辑比特,并进行了数百个逻辑门操作。同时,还展示了逻辑比特线路中快速测量和基于测量结果的实时反馈。这项技术是之后量子纠错过程中必不可少的关键环节。

原子阵列量子计算的优势

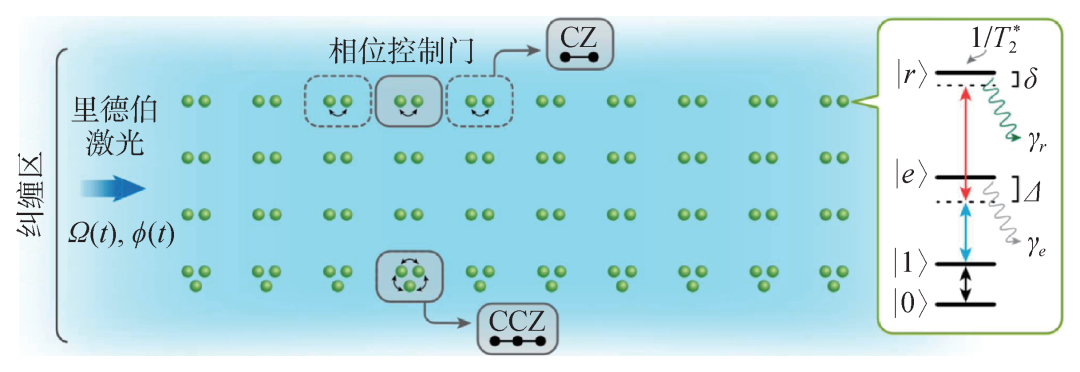

相比于现在正在发展的其他一些量子计算平台,原子阵列平台有如下几个方面的优势:(1)易于扩展。磁光阱中捕获的冷原子通常可超过千万量级,每个原子天然就是一个全同的物理比特。利用光镊技术可以在磁光阱中俘获足够多的原子作为量子比特,并对其进行可编程的单独操控;(2)全联通性。通过光镊移动原子可以将任意两个或多个原子靠近,进行量子门操作;(3)高度并行。通过将数十、数百个量子比特同时移动到“纠缠区”,一次经典操控可以同时实现大量的量子门操作(图2);(4)统计属性。很多量子计算的应用场景,比如量子化学和材料计算,涉及到电子的费米子属性。如果要用不带统计属性的量子比特来研究电子问题,需要编码费米统计,这是十分困难的。原子天然具有统计属性,如果能利用费米原子来实现费米量子计算,则可以自然地解决这一困难。

图2 利用里德伯阻塞并行地进行多对原子间的两比特或三比特量子门操作,使得一次经典操控可以同时驱动大量的量子门和量子操作。CZ代表两比特相位控制门,CCZ代表三比特相位控制门。右侧能级图展示了如何通过一束蓝光(420 nm)和一束红外光(1013 nm)将原子能级|1〉态激发到里德伯态|r〉

原子阵列量子计算近期突破的重要意义

该工作迈出了容错通用(fault-tolerant universal)量子计算的关键一步。我们现在使用的经典计算机就是“容错通用”的。“容错”是指在计算中允许硬件层面发生一些错误,这些错误可以通过纠错码得以纠正,最后仍然得到准确的计算结果。“通用”是指可以通过在计算机上运行代码,执行不同功能的任务,而不是只执行特殊定制的任务。 通过量子纠错编码,可以将多个“物理比特”编码成一个“逻辑比特”,其错误率将被指数压低。“逻辑比特”才是容错量子计算的基本单元。当然,逻辑比特也不是绝对没有错误的。纠错码有一个码距(code distance)的概念,一个码距为d的纠错码,只有同时发生大于等于d个物理比特的错误时,逻辑比特才会发生错误。对于一个有效的纠错码,码距越大,逻辑比特的错误率就越小。这次的实验进展,通过纠错码最多编码了48个码距为2逻辑比特;最大实现码距为7的纠错码编码方案。同时,展示了随着码距的增大,逻辑比特的错误率在降低,这说明实现的纠错码是有效的。此外,他们还进行了逻辑比特层面的操作,这已经远远超过了此前其他平台在容错量子计算方面所达到的水平。

原子阵列实现容错通用量子计算的前景和挑战

目前原子阵列量子计算的进展,可以说是刚刚踏入了容错通用量子计算的大门,未来的道路还很漫长,也充满挑战。按照目前最先进的技术,达到上万甚至十万量级的物理比特数目,并将两比特门的保真率达到99.9%,并以此为基础,产生百位数的逻辑比特,是未来几年极有可能达到的目标。届时,如何利用这样规模的量子资源,特别是利用上述四点原子阵列平台的硬件优势,做出一些有意义的量子计算成果,需要理论和实验的共同努力。这是当前该领域具有重要实际意义的研究问题。

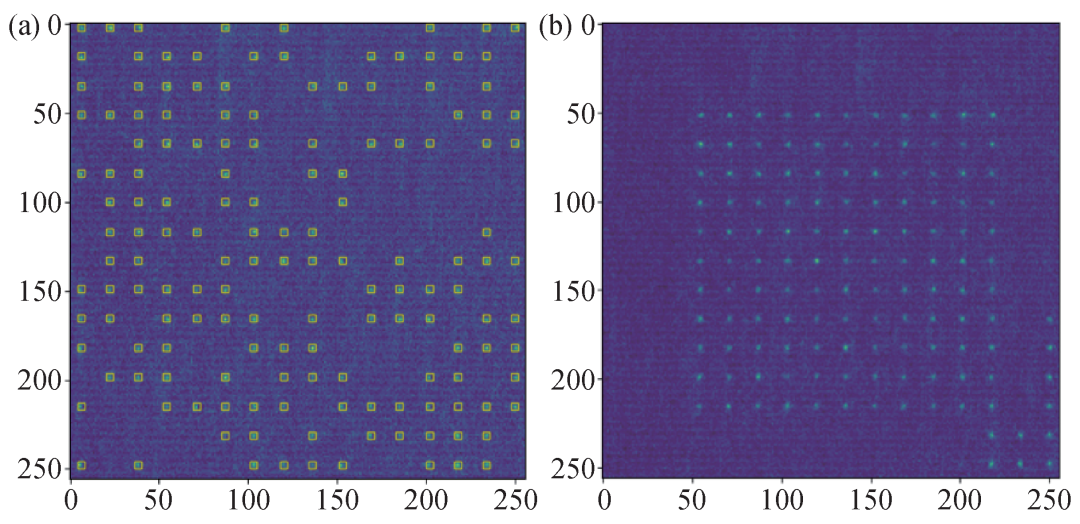

图3 原子阵列以及原子阵列重排 (a)重排前随机装载的原子,小框圈出了算法自动识别出的原子坐标,根据这些信息决策并执行重排算法;(b)经过重排后的无缺陷原子阵列。横纵轴为成像相机的像素,每个像素对应了原子处的空间尺度2 μm×2 μm 另一方面,当前技术距离实现完全的容错通用量子计算仍有相当的差距,其中主要有以下四个方面的挑战:(1)更多。将物理比特数量提升到至少千万量级甚至更大的规模,需要克服光学成像系统的视场限制、激光功率的限制、光学元件耐受性等问题;

(2)更准。要进一步提高门操作的保真度,需要解决激光噪声、里德伯态的寿命、黑体辐射和原子温度等效应的影响,以及提高量子态测量的精度;(3)更长。要保持原子阵列不间断地计算,需要发展模块化的实验装置,建立存储模块不断补充原子;

(4)更快。要实现实时的量子纠错,线路中快速测量和反馈是必不可少的,因此需要实现更快地信息读取和量子比特的移动。研究者要开发新的光镊操控的硬件、光腔和原子阵列的耦合等新技术以实现快速测量和量子纠错。

总之,原子阵列物理平台已经展示出实现容错通用量子计算的巨大潜力。未来5年左右,如何利用上万量级的物理比特和原子阵列平台的硬件优势,初步实现容错量子计算,完成一些有意义的量子计算任务,这是摆在我们面前亟待解决的科学问题。实现完全的大规模通用量子计算,是一个漫长的过程。通过未来5—10年的发展,人们有望看清楚原子阵列平台能否最终达到这一目标。

审核编辑:黄飞

- 相关推荐

- 热点推荐

- 量子计算

-

利用AI构建实用量子计算应用2024-09-09 1720

-

【《计算》阅读体验】量子计算2024-07-13 990

-

通过 ORCA-Quest 成像单原子阵列以实现中性原子量子计算2024-04-15 1095

-

【量子计算机重构未来 | 阅读体验】+ 了解量子叠加原理2024-03-13 5093

-

什么是量子计算?2023-09-19 4552

-

NTT:实现面向容错大型通用光量子计算机的模块化量子光源2021-12-29 12433

-

通用量子计算机详解2020-12-28 3508

-

基于硅量子位的可容错量子计算机体系结构的一种构建方法2020-03-27 4615

-

通过硅自旋量子位的应用来实现量子计算2019-12-26 3745

-

量子计算机实现商用仍面临着巨大挑战,任重而道远2019-12-18 4708

-

可编程离子为通用量子计算机奠定了坚实的基础2019-12-09 963

-

推进模拟量子计算机研究、实现“量子霸权”具有重大意义2018-05-18 5802

-

谷歌发布全球首个72量子比特通用量子计算机2018-03-07 4608

全部0条评论

快来发表一下你的评论吧 !