影响高速差分信号辐射发射因素之阻抗设计分析

电子说

描述

影响高速差分信号辐射发射因素之阻抗设计

1、阻抗对高速差分信号辐射发射影响的深入分析

阻抗对高速差分信号辐射发射的影响分析:

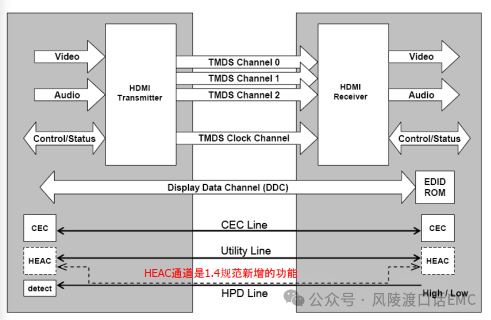

信号从SOURCE端传输到SINK端,两者之间是通过高速线缆互联,信号传输过程源端阻抗、线缆阻抗、SINK端阻抗之间完全匹配,信号无损耗的由源端传输到SINK端。而实际上由于源端阻抗、Cable线阻抗、SINK端阻抗不可能完全做到阻抗匹配,主要原因是连接器处阻抗突变、Cable线材阻抗的控制、PCB布线阻抗的控制、器件本身的阻抗设计。

在高速差分信号规范中明确给出了通用阻抗的设计要求即100±15%,以此来保证信号传输的质量。从EMC的角度来说,阻抗突变与不匹配就会产生反射,导致信号出现过冲、振铃,驻波,导致信号基频和高次谐波的辐射发射问题。

阻抗与高速差分信号辐射发射问题的关系:

特征阻抗满足100±15Ω标准要求,不意味着高速差分信号的辐射发射测试就能够顺利通过;相比于特性阻抗,瞬时阻抗对高速差分信号的辐射发射测试结果影响更大。在满足100±15Ω阻抗标准限值的情况下, 瞬时阻抗更加平坦(阻抗变化范围越小越好)则意味着信号感受到的瞬时阻抗变化越小,向外空间辐射发射的能量也相应的最小。

阻抗匹配是高速差分信号辐射发射通过的最基本的条件,即必要条件,是非充分条件。阻抗失配对高速差分信号辐射发射测试结果肯定有影响。抛开源端阻抗、线缆阻抗不谈,我们重点谈一谈SINK端阻抗。

影响阻抗的实际因素:

前面我们谈到影响阻抗的因素是:线宽线距、铜厚、介质与介质厚度、与参考平面的间距、元件的焊盘引脚宽度与厚度等。在阻抗设计过程中需要对以上因素进行严格控制,并对生产制造工艺进行控制,方可以做出阻抗精确的PCB布线。

2、阻抗设计管控原则

影响阻抗的因素众多,如何管控阻抗设计,成为EMC工程师的必修课之一。前面我们谈到元件的焊盘或者引脚宽度与厚度是影响阻抗的因素之一,从而说明在高速差分信号链路中应尽量使用最少的元件,严格控制阻抗突变点,阻抗测试曲线趋于平坦。

另外互接接口的连接器引脚处、BGA芯片的引脚焊盘、ESD保护器件的焊盘处由于器件标准化设计的原因,可以通过PCB设计进行相应的阻抗优化设计。

差分信号的线宽线距、铜厚、介质与介质厚度在PCB设计过程中需要进行严格的管控,同时在PCB生产制造工艺中也需要进行测量管控。多层板设计中,跨分隔不仅影响信号的回流路径完整性,也影响信号阻抗,参考地平面的完整性PCB设计时应给予重点管控。

由于芯片设计问题、高速差分信号端子设计问题,通常其连接处阻抗都会偏低,这时就需要增加电阻做串联匹配,若连接处出现阻抗偏大,就需要调整焊盘宽度、引脚布线宽度来调节阻抗。

对于高速差分信号设备之间互连,大部分采用线缆连接的方式,线缆本身的阻抗设计控制,也是影响阻抗匹配的最重要因素之一。由于实际上线缆生产制作厂商的参次不齐,线缆成为制约辐射测试通过的因素。高速差分信号之间采用FFC线材互连,FFC线材的阻抗控制在业界相对成熟,主要注意折线处对阻抗突变的影响。

3、PCB阻抗设计案例:

修改器件PCB封装优化阻抗:

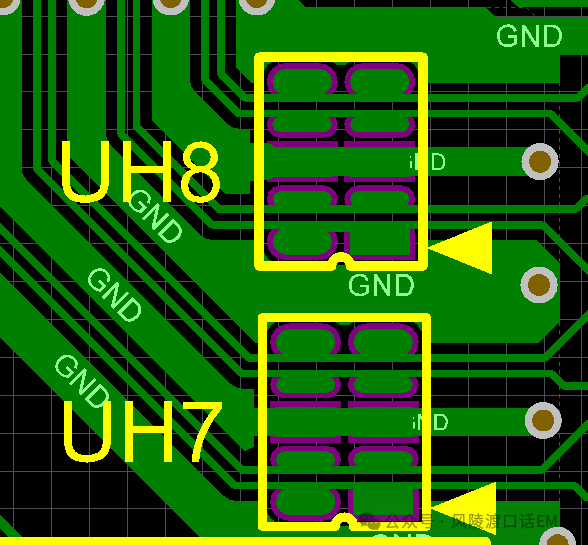

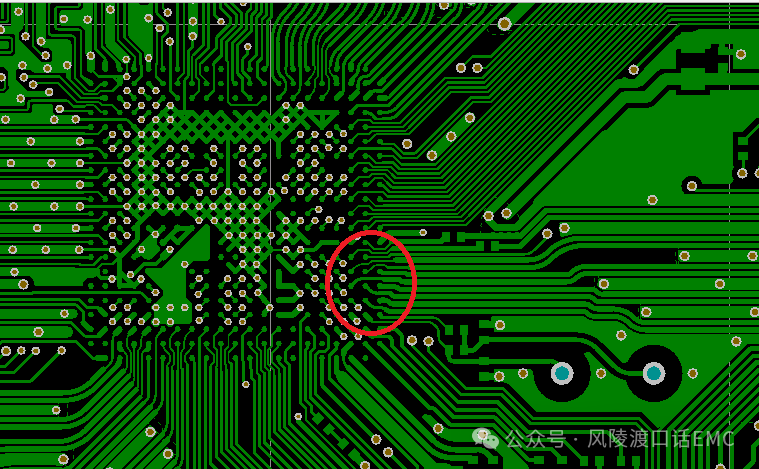

PCB Layout修改前差分信号阻抗设计

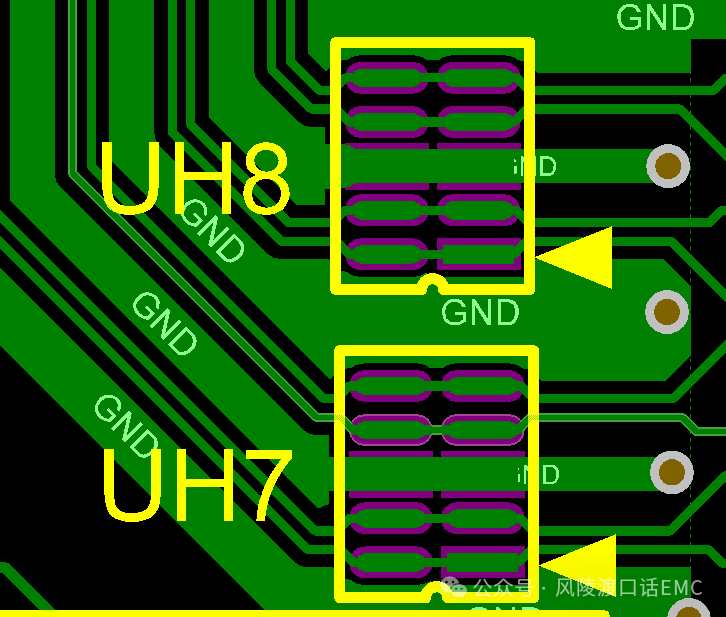

PCB Layout修改后差分信号阻抗设计

设计案例解析说明:

器件焊盘引脚是阻抗突变最严重的地方,在实际PCB设计过程中,可以通过修改器件引脚焊盘大小,来达到优化阻抗设计的目的。对于多层板因为参考层间距的问题,器件下方参考层需要做净空处理,保证阻抗设计达到标准要求。

控制线宽变化优化阻抗设计:

PCB Layout修改前差分信号阻抗设计

PCB Layout修改后差分信号阻抗设计

设计案例解析说明:

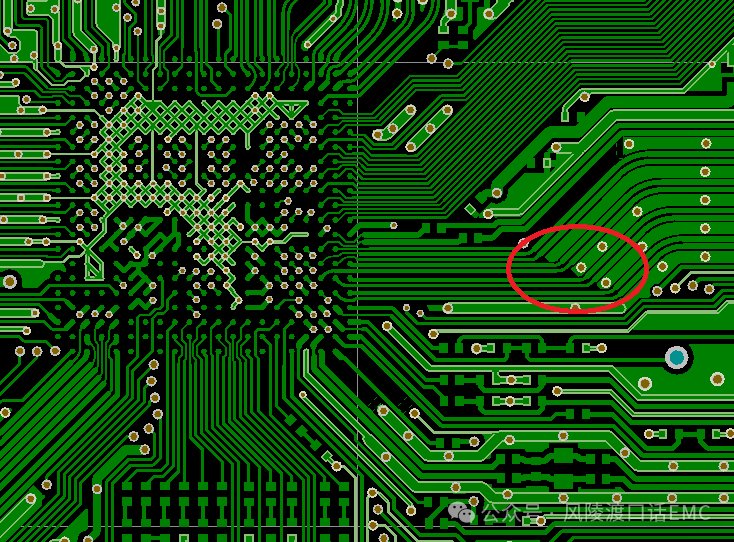

PCB布线线宽的改变,阻抗随之改变,阻抗变化的剧烈程度与线宽变化成正比。解决因线宽突变造成的阻抗突变,最好的方法就是线宽保持不变;而实际PCB设计过程中是无法达到的,退而求其次可以采用渐变线的方式解决。

介质厚度对阻抗的影响案例:

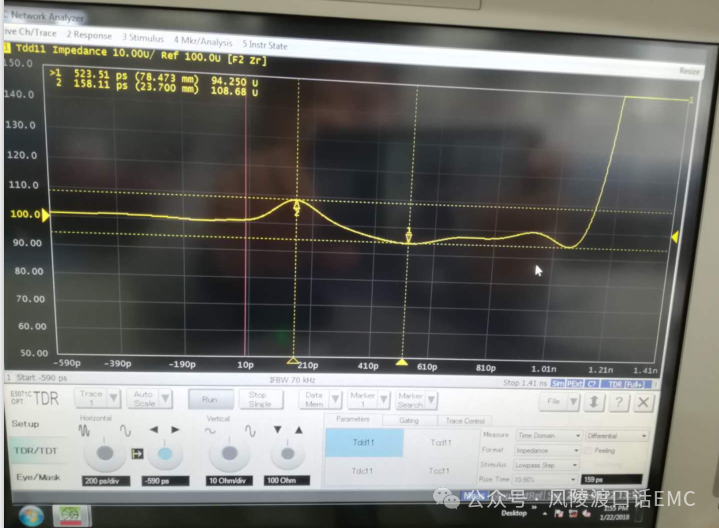

撕掉高速差分信号线上贴纸前阻抗

撕掉高速差分信号线上贴纸后阻抗

设计案例解析说明:

介质材质及厚度也是影响阻抗非常重要的因素之一,由于高速差分信号布线处平坦、器件较少,PCB设计师习惯将板卡信息贴纸、板卡型号丝印放置在高速差分信号布线上,殊不知这样会导致高速差分信号阻抗的不连续,产生信号反射及高速差分信号辐射发射问题。

审核编辑:黄飞

-

差分信号在高速通信中的作用2024-12-25 2162

-

差分信号的阻抗匹配2024-10-31 2964

-

高速差分信号阻抗匹配详解2024-05-16 7014

-

高速信号中的差分信号设计2023-06-19 3603

-

差分信号等长及阻抗匹配2023-03-06 2829

-

差分信号基础知识2019-05-31 2052

-

PCB设计高速差分信号的布线技巧2012-03-03 4965

-

基于FPGA的差分信号阻抗匹配2011-01-04 1252

-

基于低电压差分信号(LVDS)的高速信号传输2010-12-17 1151

-

差分信号,什么是差分信号2009-09-06 38887

全部0条评论

快来发表一下你的评论吧 !