什么是锁存器?数字IC设计中为什么要避免锁存器?

描述

数字IC设计里,常会出现锁存器,D触发器和寄存器,很多人(比如我)老傻傻分不清,搞不懂他们的区别是什么。

寄存器,D触发器和锁存器都是数字电路中的重要组件,它们之间存在着密切的关系和明显的区别。寄存器是一种重要的存储单元,通常由触发器组成,用于暂存指令、数据和地址。寄存器的输出端平时不随输入端的变化而变化,只有在时钟有效时才将输入端的数据送输出端。

D触发器是一种边沿敏感的存储单元,具有缓存数据的功能。当CLK输入上升沿时,D被传输到Q,之后Q将在CLK下一个上升沿到来前保持不变。也就是说,D触发器可以作为寄存器使用。

锁存器与触发器不同,它不在锁存数据时,输出端的信号随输入信号变化,就像信号通过一个缓冲器一样;一旦锁存信号起锁存作用,则数据被锁住,输入信号不起作用。锁存器一般由电平信号控制,属于电平敏感型。其状态的变化和特定电平有关(高电平和低电平),而寄存器的状态变化往往需要边沿信号(上升沿和下降沿),因此锁存器不属于寄存器。

总的来说,锁存器为电平敏感器件,而D触发器和寄存器为边沿信号敏感器件;两个锁存器可以构建一个D触发器;D触发器属于寄存器。这些设备由于其各自的特性和工作方式,决定了它们在数字电路中的不同应用场合。

什么是锁存器

锁存器是一种电路元件,用于存储和保持输入信号的状态。它通常由一个触发器和一个或多个门电路组成。当输入信号发生变化时,锁存器会将当前状态保存下来,并在下一个时钟周期中输出该状态。

换句话说, 如果一个模块的只有在特定电平的作用下,才会将输入信息更新到他的输出引脚 ,否则该模块的输出将保持不变,那么这个模块就可以被看成是一个锁存器。

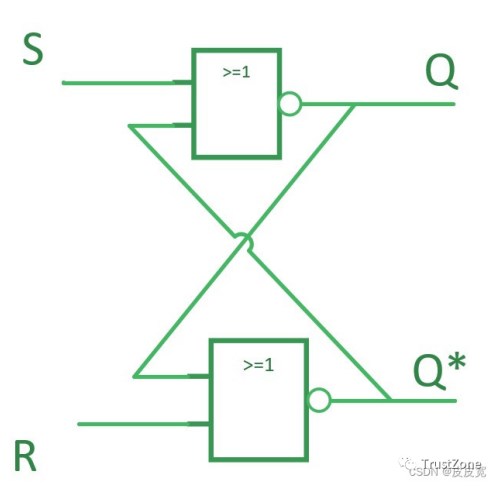

常见的S-R寄存器的结构如下所示:

锁存器在数字电路设计中有多种应用,例如数据存储、计数器、移位寄存器等。然而,在某些情况下,锁存器可能会导致电路出现错误或不稳定的行为。

什么情况下会出现锁存器

以下是一些可能导致锁存器出现问题的情况:

1.竞争条件:当多个信号同时改变锁存器的输入时,可能会出现竞争条件。这会导致锁存器无法正确地存储和输出预期的状态。

2.亚稳态:在某些情况下,锁存器的输出可能会处于不稳定的状态,即亚稳态。这可能会导致电路的误操作或故障。

3.毛刺:当输入信号发生突变时,可能会产生毛刺信号。这些毛刺信号可能会干扰锁存器的正常工作,导致错误的输出。

4.时序问题:如果锁存器的时钟信号与其他电路的时序不匹配,可能会导致电路的不稳定行为或错误。

锁存器的危害

锁存器的危害主要体现在以下几个方面:

1.数据丢失:由于锁存器只能存储和输出当前状态,如果输入信号的变化被锁存器忽略或丢失,可能会导致数据的丢失或错误。

2.竞争条件:竞争条件可能导致锁存器无法正确地存储和输出预期的状态,从而导致电路的错误或不稳定行为。

3.亚稳态:亚稳态可能导致电路的误操作或故障,影响电路的稳定性和可靠性。

4.时序问题:时序问题可能导致电路的不稳定行为或错误,影响电路的性能和可靠性。

数字IC设计中为什么要避免锁存器

为了避免锁存器的问题,数字IC设计中通常会采取以下措施:

1.使用同步电路:同步电路通过使用统一的时钟信号来控制电路的操作,可以避免竞争条件和时序问题。

2.引入延迟:通过在输入信号路径中引入适当的延迟,可以确保锁存器能够正确地采样和存储输入信号的变化。

3.使用触发器:触发器是一种具有自定时功能的锁存器,它可以确保在正确的时间点存储和输出输入信号的状态。

4.进行时序分析:通过对电路进行时序分析,可以评估电路的稳定性和可靠性,并采取相应的措施来避免锁存器的问题。

总之,锁存器在数字IC设计中具有重要的应用价值,但在某些情况下可能会出现问题。为了避免这些问题,设计人员需要了解锁存器的工作原理和可能的危害,并采取相应的措施来确保电路的稳定性和可靠性。

全部0条评论

快来发表一下你的评论吧 !