如何知道一个板卡上所能运行的最大时钟频率

描述

来源:XILINX开发者社区

Q1请问如何知道一个板子上所能运行的最大时钟频率?

如果查手册应该是芯片手册还是板子手册呢?

对应手册的关键字应该是什么呢?

比如我的芯片是KCU115,但是搜索出来的没有这个芯片的资料,我应该怎么获取它的手册呢?

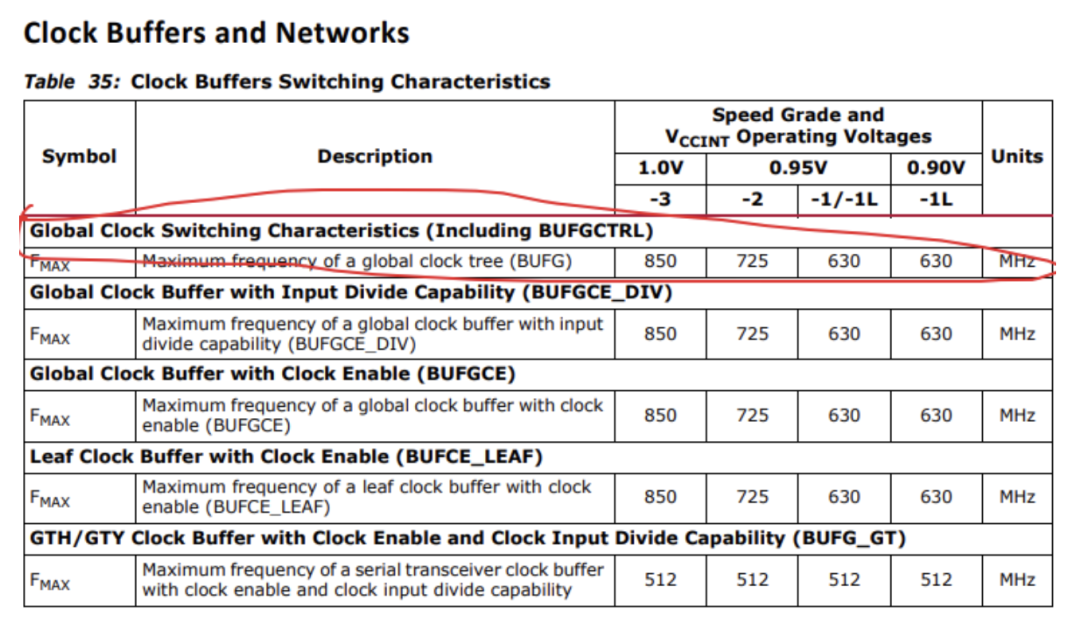

A:可以查看Kintex UltraScale FPGA Data Sheet: DC and AC Switching Characteristics (DS892)手册中关于BUFG的部分。另外,还应结合设计的时序情况:

Q2我发现FIFO这些IP的最高频率达到400MHz+,而在实际应用中,板子没有跑到这么高的频率,是不是板子资源有限制?

A:实际逻辑在board上能跑到的频率和设计本身强相关:资源使用情况,代码风格,fanout情况,逻辑级数,控制逻辑的数目...等等。

Q3ILA IP 的最大频率是250M,但是一般300M给到ILA没有出现问题,时序报告也没有警告,这是什么原因呢?

A:ILA IP是用普通逻辑搭建的,实际能跑到的频率和采样数据的数量和原有逻辑资源的使用量基本成反比。

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

调试一块使用lmk04228作为光纤通讯的参考时钟的板卡,遇到的疑问求解答2024-11-11 399

-

精准时刻,掌控未来:解锁新一代PCIe时钟板卡!2024-06-24 1293

-

四个单片机能共用一个晶振时钟频率来工作吗?2024-01-31 3780

-

ADSP-21584的SPORT所能支持的最大频率是多少?2023-11-29 523

-

时钟频率和晶振频率的区别2022-01-29 12475

-

系统时钟的最大频率2021-08-19 849

-

怎么在一个时钟区域内使用多个时钟频率?2020-03-20 1436

-

如何运行主模式下的pic18f2xk40最大spi时钟?2019-10-30 1325

-

什么是最大时钟频率?2019-10-17 3619

-

psoc3上wavedac8的最大输出频率是多少?2019-09-09 2216

-

关于电容所能承受的最大的瞬时电压问题2019-05-28 8230

-

什么是设计可以运行的最大时钟频率2019-02-26 3600

-

信号在fpga内部结构上运行的最大频率是?2019-01-30 4404

-

处理器一条指令需要几个时钟周期2018-03-11 15322

全部0条评论

快来发表一下你的评论吧 !