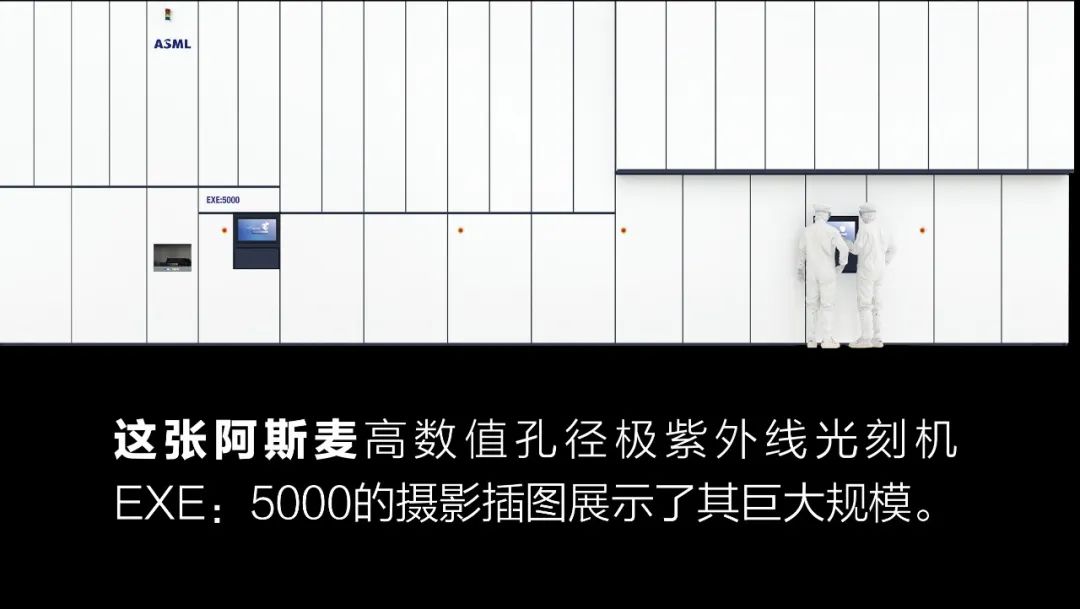

高数值孔径EUV光刻:引领下一代芯片制造的革命性技术

制造/封装

描述

可实现更小晶体管的下一代技术是高数值孔径EUV光刻。

摩尔定律是指在给定面积的硅片上,晶体管的数量大约每两年翻一番,这种增益推动了计算技术的发展。在过去半个世纪里,我们将该定律视为一种类似进化或衰老的不可避免的自然过程。然而,现实却大不相同。要跟上摩尔定律的步伐,需要花费几乎难以想象的时间、精力和人类智慧,地球上无数的人和无数台最复杂的机器都被裹挟其中。

其中最重要的可能就是极紫外(EUV)光刻机了。EUV光刻技术是几十年研发工作的产物,是过去两代尖端芯片背后的驱动技术,过去3年里,每一款高端智能手机、平板电脑、笔记本电脑和服务器中都有它的身影。然而,摩尔定律必须继续前进,芯片制造商也在继续推进他们的路线图,这意味着需要进一步缩小设备的几何尺寸。

而下一代光刻技术——高数值孔径EUV光刻,涉及了对系统内部光学系统的重大改造,在这个十年结束前,芯片行业有望依靠它来持续进步。

分辨率与数值孔径

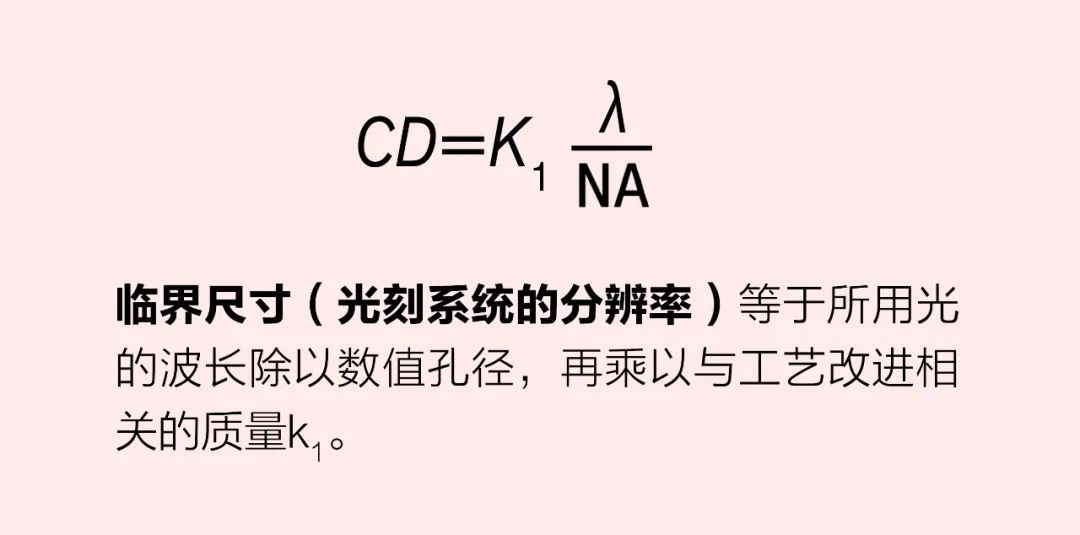

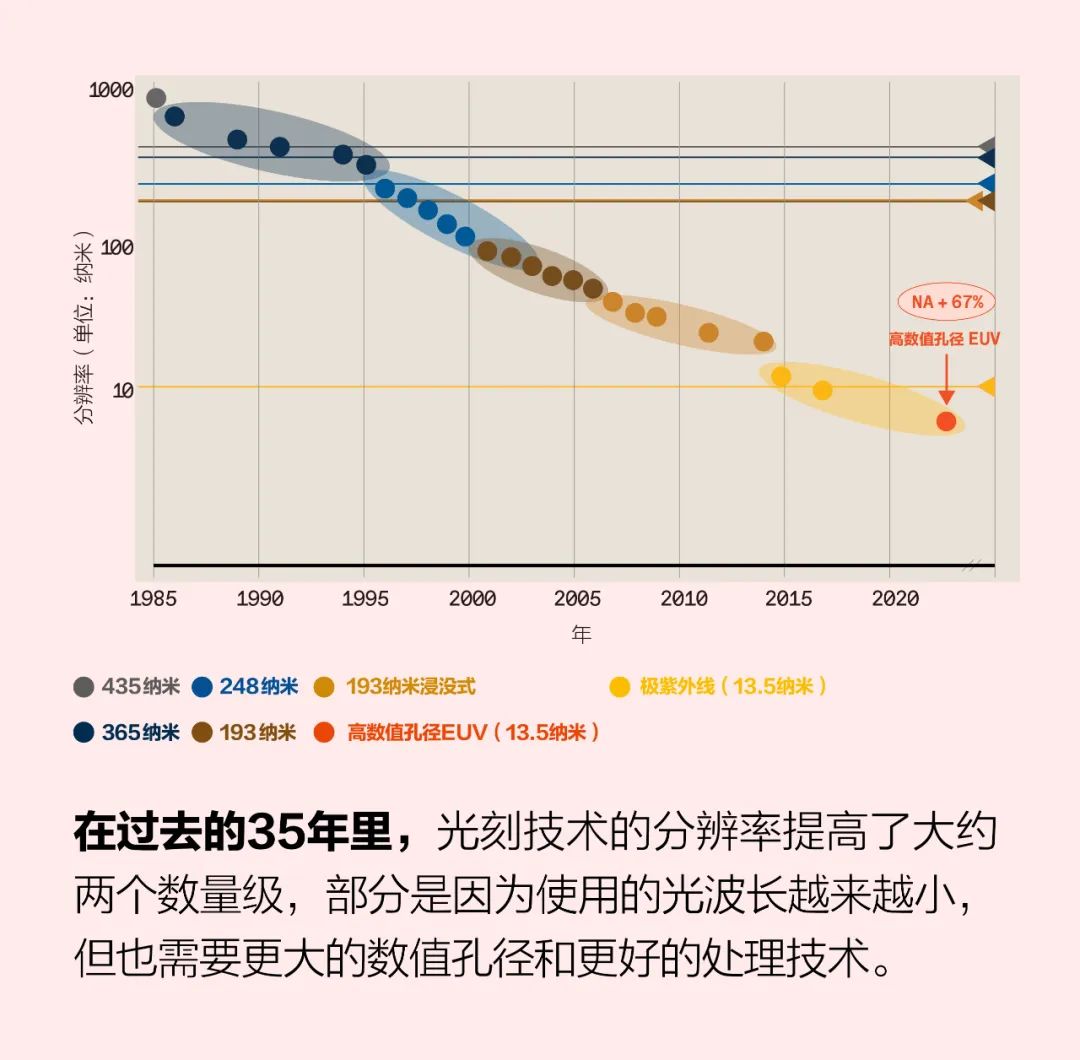

摩尔定律的维系有赖于光刻技术分辨率的提高,这样一来,芯片制造商就可以制造越来越精细的电路。在过去的35年里,通过研究光的波长、封装过程相关因素的系数k1以及衡量系统发光的角度范围的数值孔径(NA)这3个因素的组合,工程师们已经将分辨率提高了两个数量级。

临界尺寸是使用某种光刻曝光工具可以打印的最小产品尺寸,它与光的波长除以光学元件的数值孔径所得的值成正比。因此,我们可以通过使用更短的光波长或更大的数值孔径,或者两者的结合来实现更小的临界尺寸。例如,通过改进制造过程控制,k1值可以尽可能地接近其物理下限0.25。

一般来说,提高分辨率最经济的方法是提高数值孔径,以及改进工具和过程控制以实现更小的k1。芯片制造商只有在无法进一步提高数值孔径和k1时,才会想办法缩短光源波长。

不过,半导体行业已经多次修改了波长。波长历史的发展从使用汞灯产生的365纳米开始,到20世纪90年代后期通过氪-氟激光器生产的248纳米,再到本世纪初通过氩-氟激光器生产的193纳米。对于每一代波长,在行业采用更短的波长之前,光刻系统的数值孔径都是逐渐增大的。

例如,随着193纳米的使用即将结束,人们又引入了一种新的方法来扩大数值孔径:浸没式光刻。通过在透镜底部和晶圆之间放置水,数值孔径可以从0.93大幅提高到1.35。自2006年左右推出以来,193纳米浸没式光刻技术一直是业界领先的主力光刻技术。

提高数值孔径迫在眉睫

不过,随着对印刷小于30纳米产品的需求增加,以及193纳米光刻技术的数值孔径已经达到极限,要跟上摩尔定律的步伐变得越来越复杂。要制造小于30纳米的产品,要么需要使用多种图案来制造单层芯片产品(这是一种技术成本和经济成本都很高的技术),要么需要改变波长。经过20多年的时间和前所未有的开发研究,13.5纳米EUV这一新波长才得以上线。

EUV需要一种全新的发光方式。这是一个非常复杂的过程,需要用强大的二氧化碳激光撞击在半空中滴落的熔锡液滴。激光会将锡蒸发成等离子体,发射出光子能量光谱。EUV光学元件可从这个光谱中获得所需的13.5纳米波长,并引导它通过一系列镜子,再将其反射到有图案的掩模上,将图案投射到晶圆上。整个过程必须在超净真空中完成,因为13.5纳米波长会被空气吸收。(前几代光刻技术都是引导光穿过掩模,将图案投射到晶圆上。但是EUV非常容易被吸收,因此掩模和其他光学元件必须具有反射性。)

从193纳米光转变为EUV在一定程度上缩小了临界尺寸。一种名为“可制造性设计”的方法大大降低了k1。该方法设置了电路模块的设计规则,利用了光刻技术的局限性。现在是时候再次提高数值孔径,从目前的0.33提高到0.55了。

在真空室中,EUV光(紫色)在从光掩模)反射之前,会被多面镜子反射。光从那里继续反射,直到被投射到晶圆上,且携带光掩模的图案。这张插图显示了目前数值孔径为0.33的商业系统。在数值孔径为0.55的未来系统中,光学元件将有所不同。

面对的挑战

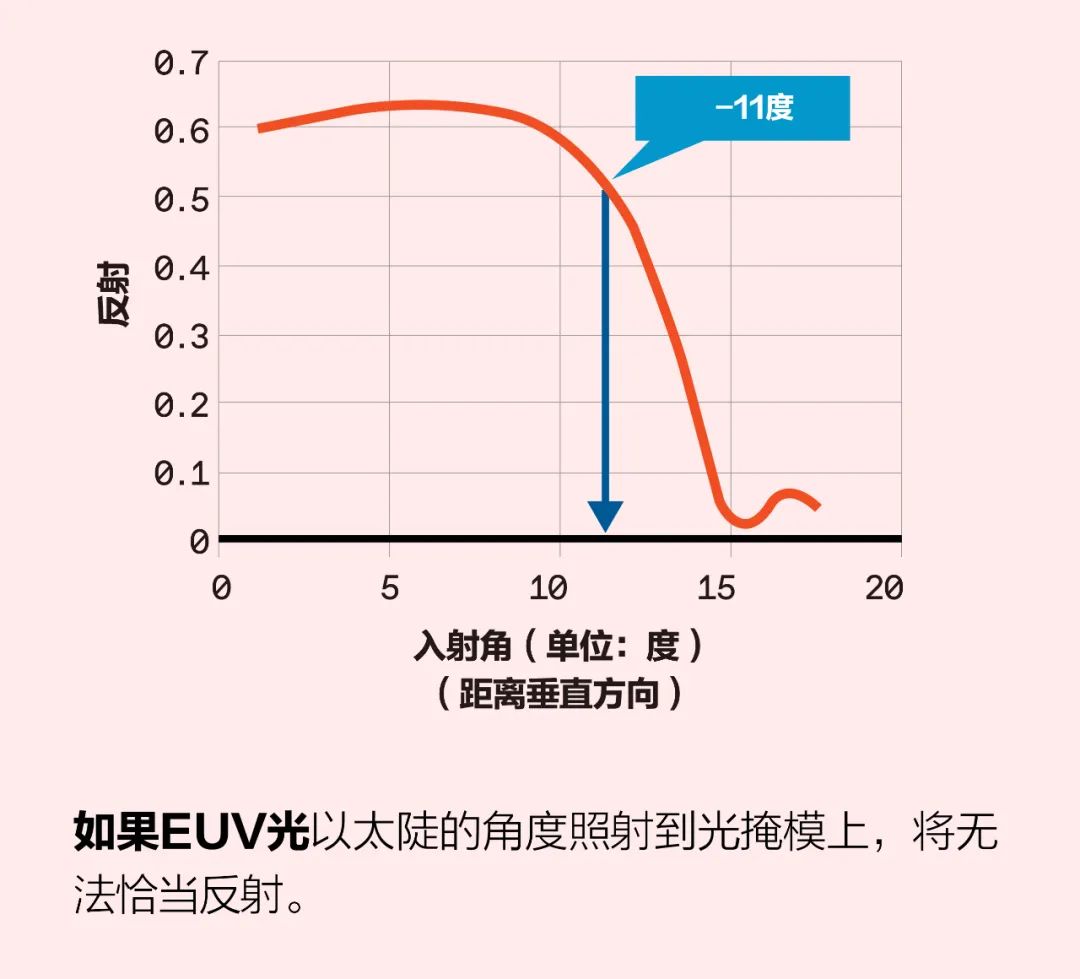

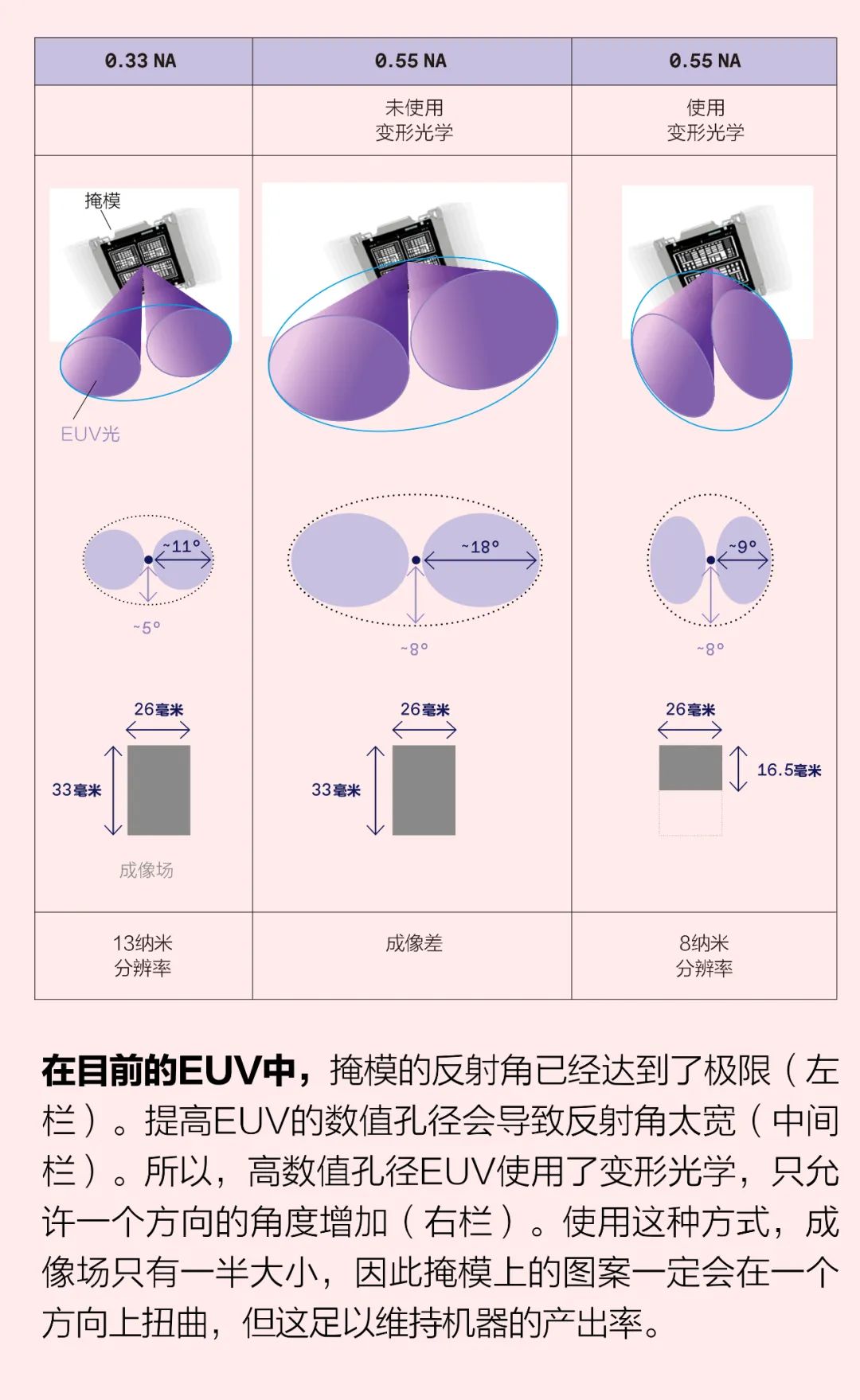

要将数值孔径从0.33提高到0.55的目标值,不可避免地需要一系列其他调整。EUV光刻等投影系统在晶圆和掩模上都有数值孔径。增大晶圆上的数值孔径时,掩模上的数值孔径也会增大。因此,掩模入射和出射的光锥会变得更大,且必须彼此斜向远离以避免重叠。重叠的光锥会产生不对称的衍射图案,进而带来不理想的成像效果。

但是这个角度是有限制的。因为EUV光刻技术所需要的反射掩模实际上是由多层材料制成的,所以我们无法确保在某个反射角以上产生合适的反射。EUV掩模的最大反射角为11度。虽然还有其他困难,但反射角是最大的挑战。

克服这个挑战的唯一方法是增加一种叫做“缩倍”的特征。顾名思义,缩倍是指从掩模中取出反射图案并缩小它。为了弥补反射角的问题,不得不将缩倍数提高到8。结果,在晶圆上成像的掩模部分小了很多。成像场较小意味着需要更长的时间来产生完整的芯片图案。事实上,这一要求会使我们的高数值孔径扫描仪的产出率降低到每小时100片晶圆以下,该生产率水平会使芯片制造变得不经济。

令人欣慰的是,研究人员发现只需要在一个方向上提高缩倍,也就是反射角最大的方向,另一个方向上的缩倍可以保持不变。如此一来,晶圆上就有了一个大小可以接受的成像场——大约是今天EUV系统所用尺寸的一半,即26毫米×16.5毫米,而不是26毫米×33毫米。这种方向相关或失真的缩倍形成了我们高数值孔径系统的基础。

为了确保半尺寸场具有相同的生产率水平,还必须重新开发系统的掩模台和晶圆台(分别固定掩模和晶圆的两个平台),并在扫描过程中同步移动它们。高数值孔径EUV是维系摩尔定律的关键组成部分,但实现0.55数值孔径并不是最终目标,整个半导体生态将在此基础上向更好、更快、更新颖的技术迈进。

审核编辑:黄飞

-

[VirtualLab] 高数值孔径物镜焦斑分析2026-04-01 533

-

ASML研发更先进光刻机 高数值孔径极紫外光刻设计基本完成2020-12-29 3173

-

ASML下一代EUV光刻机延期:至少2025年2021-01-22 3842

-

ASML开发的下一代EUV平台2022-06-02 2673

-

焦点芯闻丨ASML 阿斯麦 CEO 透露高数值孔径极紫外光刻机 2024 年开始出货2022-11-18 5032

-

高数值孔径EUV的技术要求是什么2023-08-11 1267

-

关于高数值孔径EUV和曲线光掩模等灯具的讨论2023-10-17 1077

-

高数值孔径EUV的可能拼接解决方案2023-10-23 2339

-

高数值孔径 EUV技术路线图2023-11-23 1745

-

ASML推出首款2nm低数值孔径EUV设备Twinscan NXE:3800E2024-03-15 2449

-

单模光纤数值孔径一般是多少2024-04-09 5001

-

阿斯麦(ASML)公司首台高数值孔径EUV光刻机实现突破性成果2024-04-18 2125

-

英特尔完成高数值孔径EUV光刻机,将用于14A制程2024-04-19 1389

-

英特尔率先推出业界高数值孔径 EUV 光刻系统2024-04-26 1104

-

高数值孔径投影光刻中的偏振效应2026-03-19 391

全部0条评论

快来发表一下你的评论吧 !