DC-DC EMC问题产生原因分析

电源/新能源

描述

01

DC-DC工作原理及电流环路分析

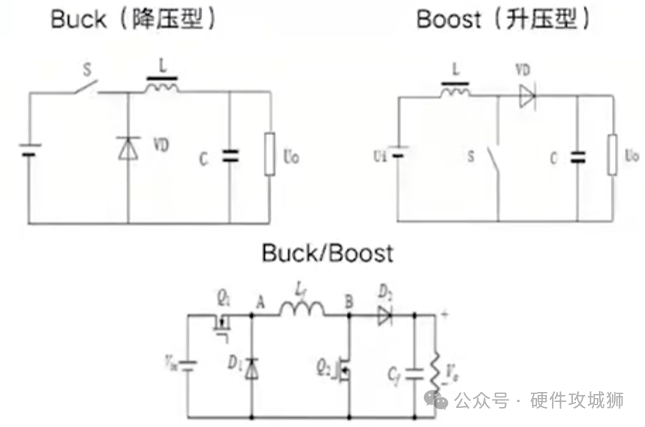

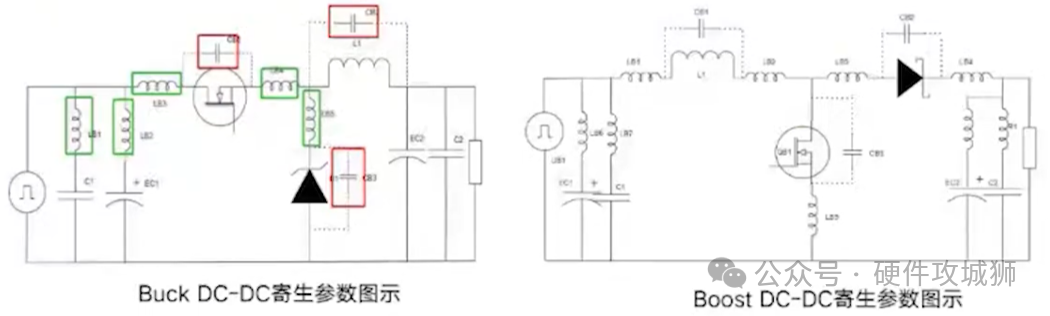

首先从dcdc的拓扑开始,一般DCDC的拓扑类型会有BUCK,BOOST,BUCK/BOOST,BOOST/BUCK等,它们是开关式DCDC,利用电容和电感储能的特性,通过开关管进行开关动作,将电能储存在电容和电感里,当开关管断开时,电能释放给负载。

若进一步细分DCDC的种类,以激励方式分为自激式和他激式;以调制方式可以分为脉宽调制和频率调制;以隔离方式分为隔离式(反激,LLC)与非隔离式;以承受电应力分为硬开关和软开关(软开关和硬开关的最大区别就是电压应力和电流应力);以开关同步方式分为同步开关和异步开关;以储能电感连接方式分为串联型和并联型。

一:BUCK拓扑

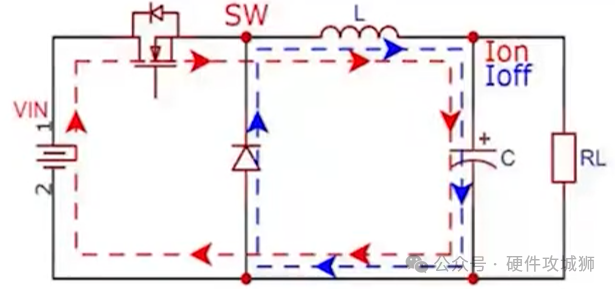

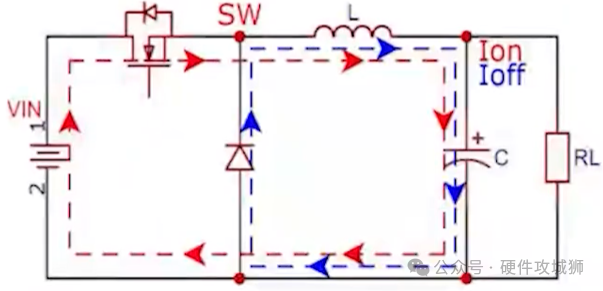

BUCK工作原理之开通环路:

上图的红色部分就是开通环路,MOS管导通时,输入源电流流经MOS管对电感进行储能,流经电感电流开始上升,同时有一部分能量传递到输出端,此时二极管承受反向电压而不导通。

BUCK工作原理之续流环路:

上图蓝色部分就是续流环路,MOS管关断时,输入源不再提供能量,电感产生反向感应电压,使得二极管导通,电感储存的能量通过二极管形成的续流回路传递到输出端,流经电感电流开始下降。 在DCDC中遇到的EMC问题中最多的就是开通环路和续流环路,有时遇到一个DCDC的EMC的问题时给二极管串联一个磁珠就好了,有时会出现振铃,那么这个振铃如何解决,这两种情况就跟拓扑的环路有关系,接下来通过电流分析说明EMC问题产生的原因。

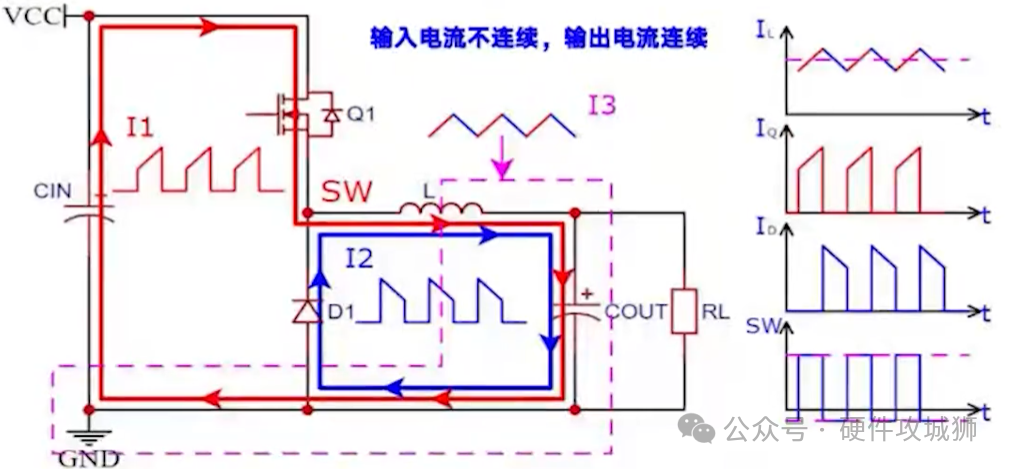

BUCK工作原理之电流分析:

由上图可知,BUCK的输入电流是不连续的,输出电流是连续的,在MOS管关断之后,电感左侧就没有电流输入,此时所有电流都往输出端流了。再看波形,第一个是电感电流的波形,因为负载的电流波形肯定是连续的,而MOS管的电流和二极管的电流就是一半有一半没有。 EMC问题:MOS管在开通和关断的瞬间会产生很高的电压尖峰,取决于开关频率的高低,SW是方波电压波形,它是dv/dt电压变化率和di/dt电流变化率的地方,也就是EMC问题产生的地方,另外就是自激振荡。 EMC问题:二极管的噪声来源于它的反向恢复。

二:BOOST拓扑

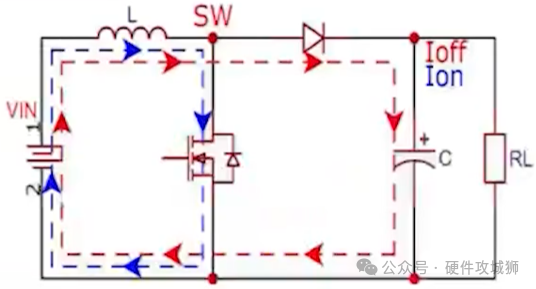

BOOST工作原理之开通环路:

上图的红色部分就是开通环路,MOS管导通时,电流流经MOS管对电感进行储能,流经电感电流开始上升,此时SW节点电压为MOS管压降,二极管承受反向电压而不导通,能量不传递到输出端,输出端能量由电容提供。

BOOST工作原理之续流环路:

上图蓝色部分就是续流环路,MOS管关断时,电感储存的能量通过二极管传递到输出端,同时直流输入源也对负载提供能量,流经电感电流开始下降。

BOOST工作原理之电流分析:

BOOST的电流环境中,有SW的节点,二极管是升压用的,存在反向恢复的问题,mos管也一样,存在开关噪声,它跟buck最大的不同就是它的输入电流连续而输出电流不连续,因为电感要有持续的电流流过,实际上EMC问题和BUCK差不多,就不多赘述了。

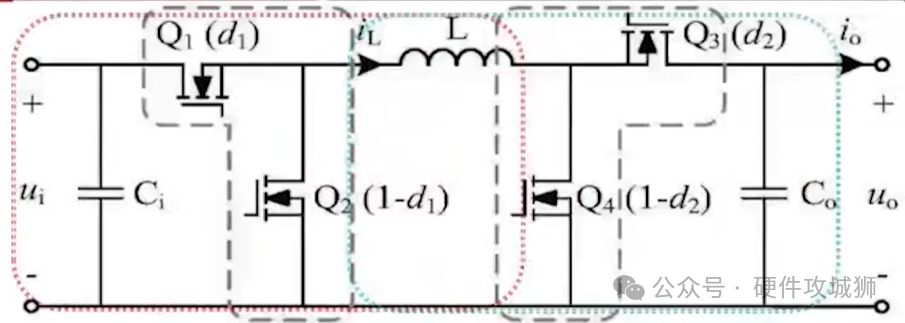

三:BUCK/BOOST拓扑

BUCK/BOOST工作原理之降压功能:

Q1、Q3管导通, Q2、Q4管关断,完成Buck电路开通环路; Q2、 Q3管导通,Q1、Q4管关断完成Buck电路续流环路。

BUCK/BOOST工作原理之升压功能:

Q1、Q4管导通,Q2、Q3管关断,完成Boost电路开通环路;Q1、Q3管导通,Q2、Q4管关断完成Boost电路续流环路。另外,此电路也可以反过来用。

BUCK/BOOST工作原理之电流分析:

此拓扑的电流模式也和buck跟boost的差不多,就不多赘述了。

02

DC-DC EMC问题产生原因分析

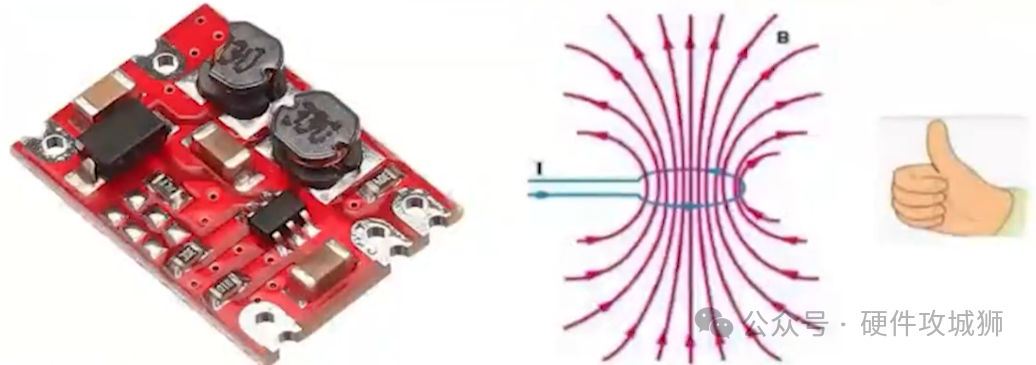

一:电感(电感磁场空间辐射,耦合电感磁场产生的涡流效应)

通常使用几种BUCK电感:磁屏蔽电感和非磁屏蔽电感和环形电感和工字电感,不同的电感产生的效果是不一样的。 环形电感:它的磁路是闭合的,没有磁场泄露在空气中,漏磁相对较小。 工字电感:它的磁场变化形成闭合回路,是非磁屏蔽电感,有很多的磁场落到空气中,造成磁场耦合。 磁屏蔽电感:无法泄露磁场。 非磁屏蔽电感:会泄露磁场。 EMC问题:电感磁场辐射,以工字型非磁屏蔽电感为例,当脉动电流流过时就会产生磁场辐射,低频磁场在附近的信号回路、磁性元件(共模电感、差模电感)产生感应电压与感应电流,造成信号干扰、或者引发其他问题;低频磁场穿过附近金属平面时会产生涡流效应,若不能有效消除涡流噪声,则会产生严重的辐射问题。 解决方法:如果说预算充足可以直接使用磁屏蔽电感,这样可以省略这部分问题。

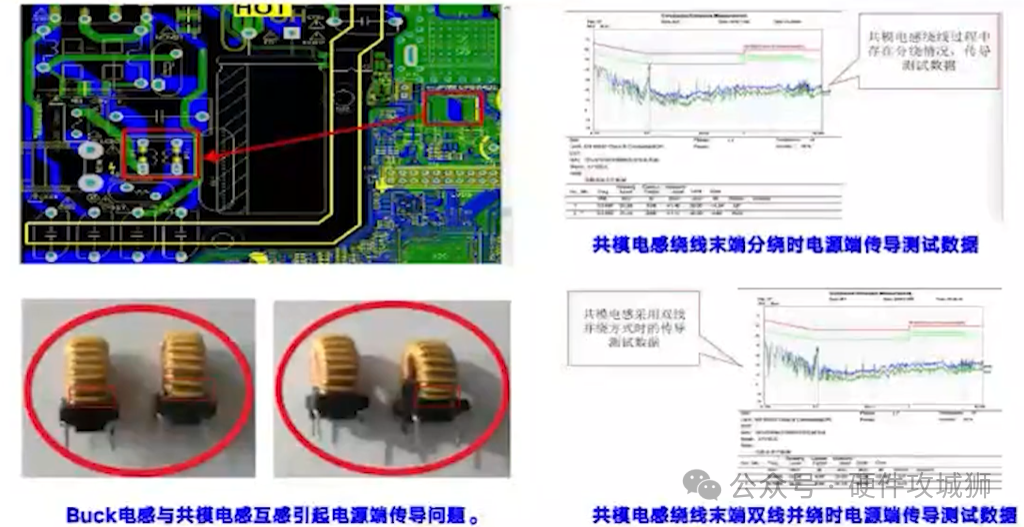

EMC问题:如果共模电感靠近电源电感太近了,就会导致互感的问题。 EMC问题:双线分绕的和双线并绕的共模电感出现的问题不一样,在各种资料中都会说电感要双线并绕,那为什么要双线并绕呢,就是因为双线并绕的时候两根线感应到的能量是一样的,相减去差不多就抵消掉了。

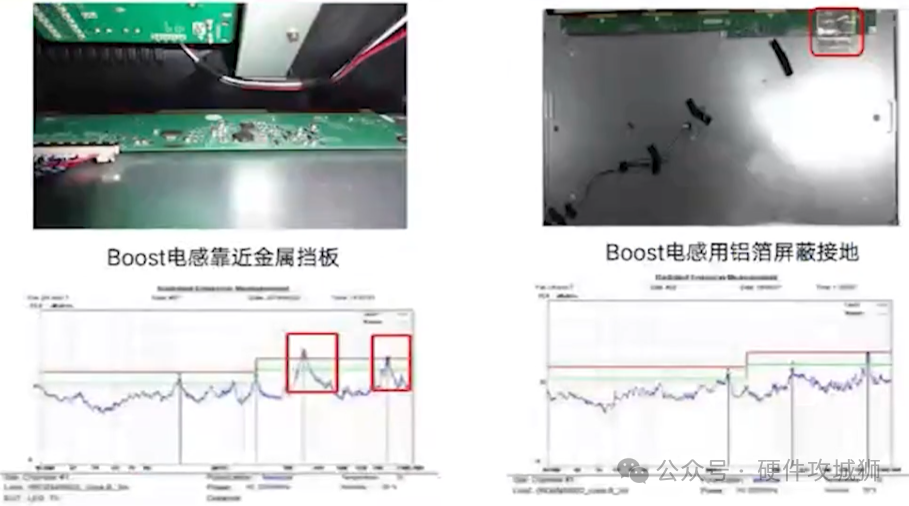

EMC问题:接下来是涡流,当电感靠近金属的时候,就会产生涡流,如上图的显示器的电感太靠近金属支架,就会产生涡流,那这个金属支架就成了一个天线。 解决方法:第一就是把这个电感换成屏蔽电感,第二就是金属支架接地,让它产生的涡流能量回到原点,这个环路也保持最小。

二:开关噪声(MOS管开关噪声,二极管续流开关噪声)和寄生参数(功率器件寄生参数,PCB寄生参数,器件+PCB寄生参数,结构装配寄生参数)

EMC问题:开关噪声跟辐射的关系,功率器件工作于开关状态时,di/dt环路会产生磁场,dv/dt节点会产生电场;高频电流环路和高频开关节点分别产生交变磁场与交变电场,从而引发严重的空间辐射问题。

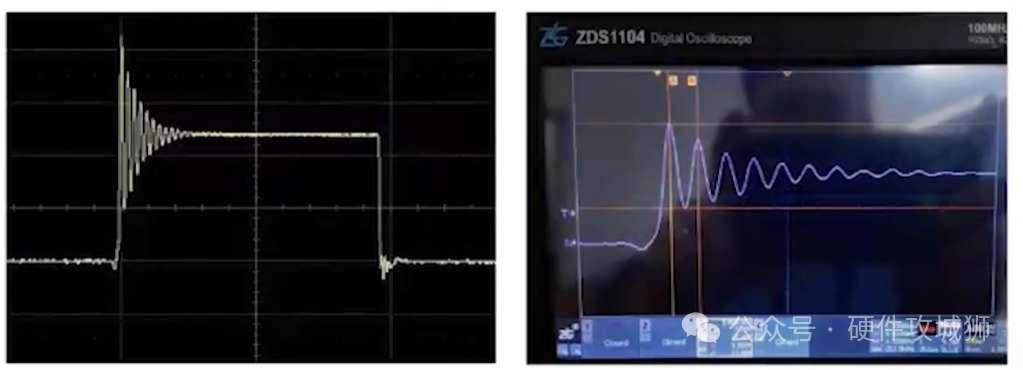

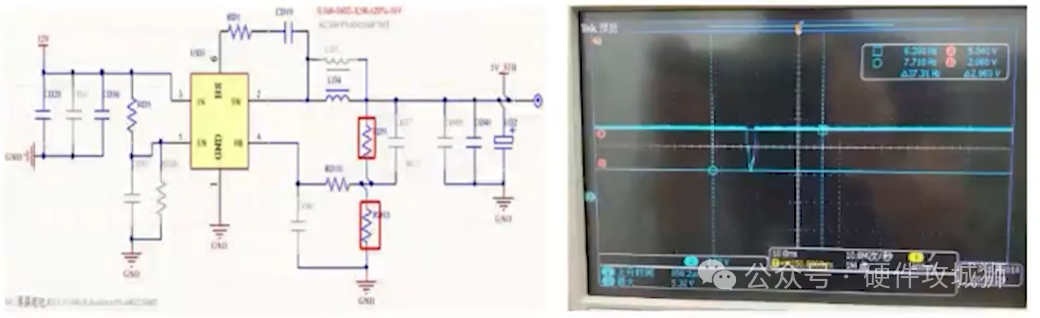

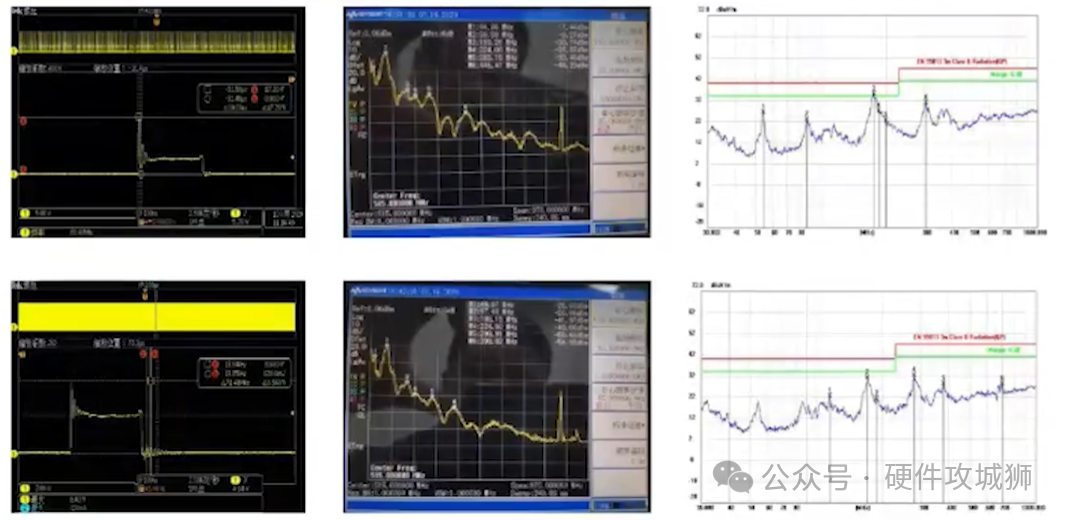

EMC问题:由下图可知,开关波形的SW信号振荡导致有振铃产生,这个电压会很高,甚至高于MOS管的电压应力时会击穿MOS管(二极管同理),烧坏整个电路。那么这个振铃是怎么产生的呢,由上右图可以看到,如果将此波形展开来看,可以发现一个220M频率的信号,这个信号就是振铃,接下来讨论它如何产生的。

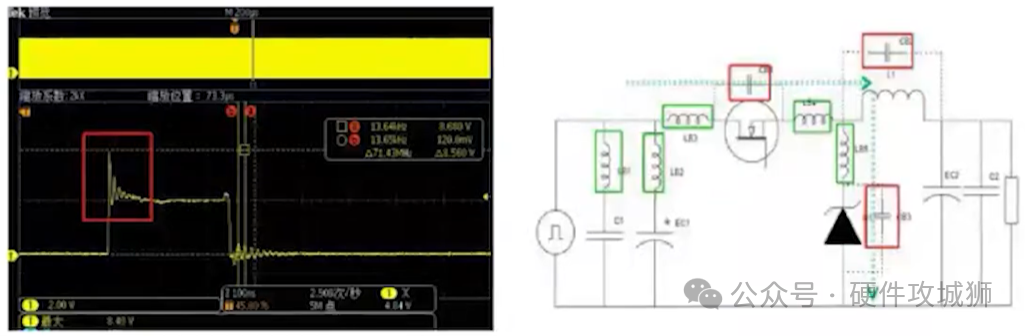

振铃的产生:MOS管开通时,续流二极管寄生电容CB3被充电,寄生电感LB3, LB4积蓄能量,当SW动态节点的电压等于输入电压时,积累在LB3、LB4中的能量与CB3电容产生LC串联谐振,从而产生上冲振铃干扰,因此可以总结出来上冲振铃实际上是续流二极管产生的。

振铃的产生:MOS管关断时,续流二极管导通,电感中会有电流持续流过,开关MOS管寄生电容CB1被充电,续流二极管寄生电容CB3放电,当输出电压SSW动点电压时,开关MOS管的寄生电容CB1停止充电,储存在寄生电感LB3、LB4的能量与CB1组成LC串联谐振,产生下冲振铃噪声干扰,因此可以总结出来下冲振铃是MOS管的寄生电容产生的。

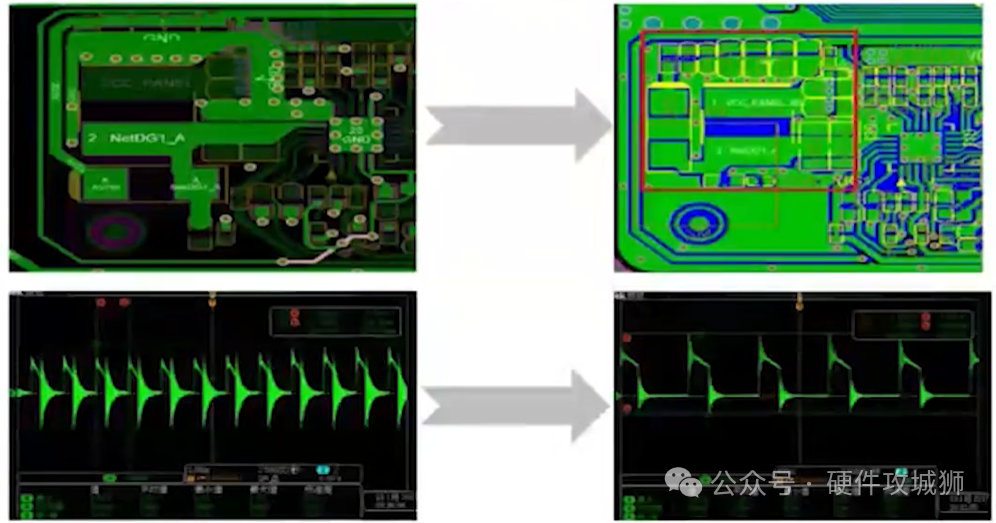

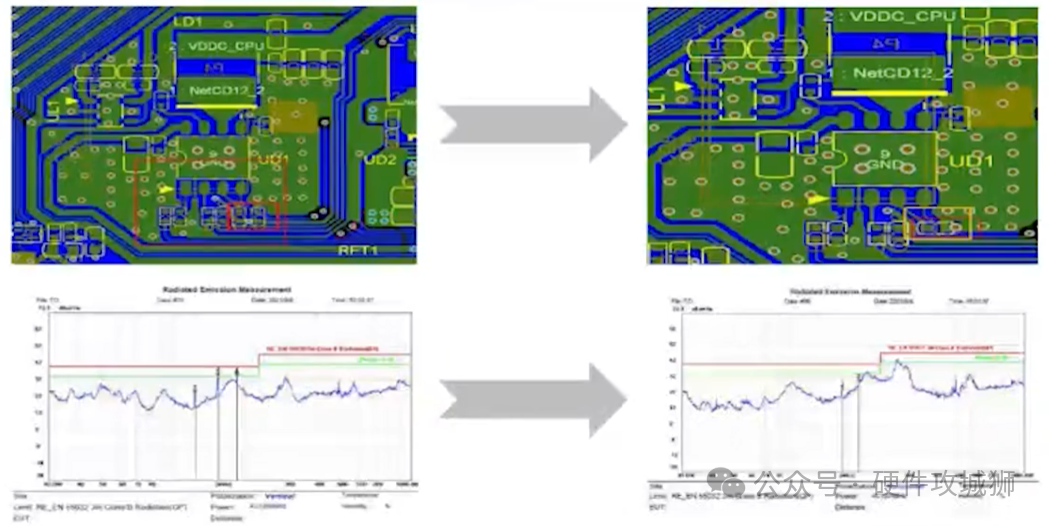

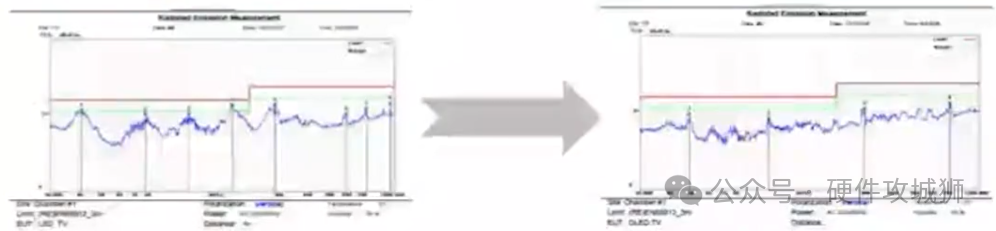

由上可总结出: EMC问题:上冲振铃跟下冲振铃同时存在时就说明环路有问题,PCB布线出了问题。 解决方法:更换了一个MOS管或二极管甚至串联一个磁珠之后寄生振荡有所改变,就说明寄生电容或寄生电感改变了,实际上寄生振荡的频率也改变了。但如果说串联了一个磁珠,就会带来一个新的电压应力的问题和走线的问题。 由下左图所示,BOOST二极管的走线太长了,导致一个很严重的寄生振荡波形,而优化后由上右图所示,可以发现振荡减轻了不少,二极管连接了一个电容,而电容靠近二极管的引脚,此时二极管到电容的导线的寄生振荡就基本可以被抵消掉。 可以看到,能用布线避免的问题就尽量用布线避免,如果加了吸收,引来了纹波的问题;如果加了磁珠,就会引来应力的问题。

寄生振荡产生原因:PCB寄生电感降低高频旁路效果,产生寄生振荡;功率器件寄生电容提供高频电流耦合路径,产生寄生振荡;PCB寄生电容引发近场耦合;高频旁路电容与PCB寄生电感引发寄生振荡。 寄生振荡是高频辐射,高频噪声产生的主要因素,同时寄生振荡可以改变寄生电感和寄生电容。

对于寄生参数的影响,由于寄生参数太复杂,各个元件(二极管,mos管,pcb)都有寄生参数,还有结构的分布参数,糅合在一起就非常的困难。

三:电流环路(开通环路,关断环路,主功率环路,高频环路)

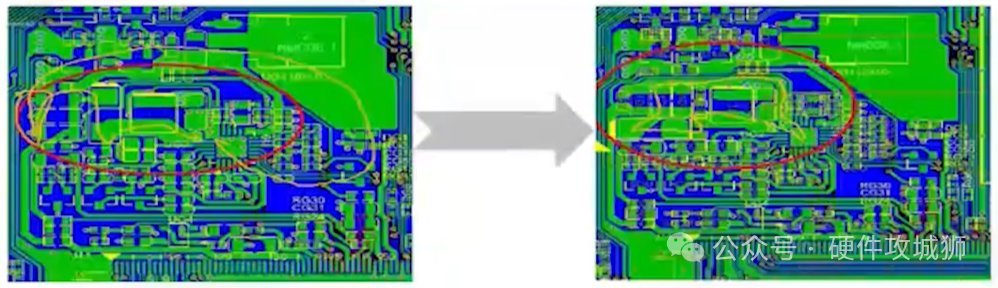

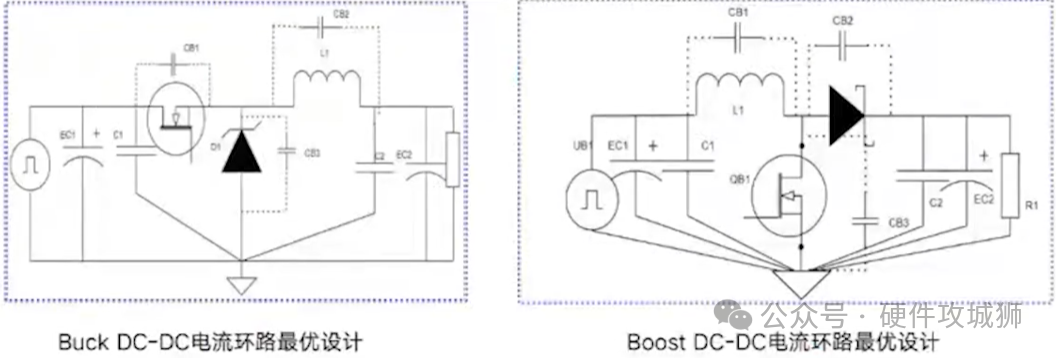

高频电路环路形成的磁场大小取决于环路面积和电流大小,高频电流环路面积越小,磁场对消效果就越好;反之,高频电流环路面积越大,磁场对消效果就越差,空间辐射就越强。 所有的教科书都会说要保持电流环路最小,为什么呢,对于一个电路而言有正和负两个线,一个出一个回,电流方向是完全相反的,此时产生的磁场就可以完全抵消,就不会对外界产生干扰让环路以外没有能量,如果让环路最小,就可以保证这个事情。环路越长意味着走线越长,就会带来寄生电感的影响,就会产生寄生振荡,寄生振荡的效果是很不理想的,如果开关芯片工作在200K的频率下,就可能出现200M的状况。环路最小的第二个好处就是可以避免寄生振荡的出现。

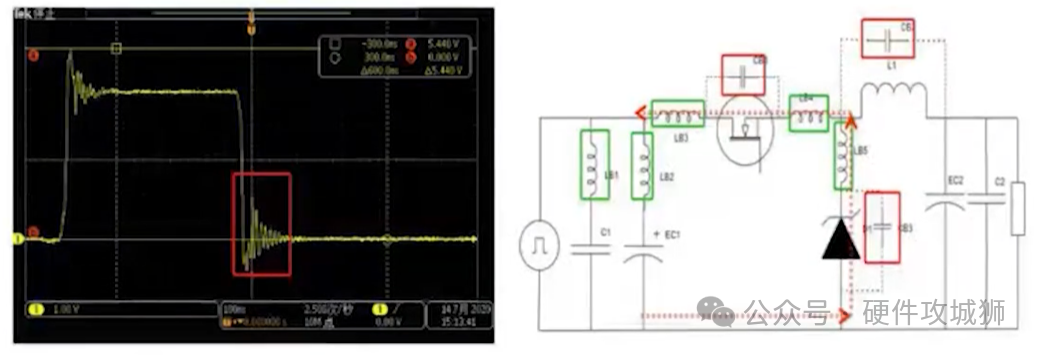

我们要保证环路最小,就要知道环路是怎么走的,还有就是怎么做才能让环路保持最小,接下来分析下图案例。 案例一:如下图,这是一个dcdc的滤波电容,在实际的运用中,就会就地打过孔接地,如下左图所示,问题出在过孔到底层并不能按照我们预期的正常工作,由左图所示,这样打过孔接地相当于让GND绕了一圈回来接地,让环路增大了不少,而将电容的位置改成右图那样,此时这个电容的接地点就是芯片的参考地,此时它的环路是唯一的,直接从顶层回到GND的环路,由于过孔存在寄生电感,那么对于高频来说,寄生电感会选择这条最小的路径回去,既可以直接接地,还可以避免不必要的环路存在。然后看第二个案例。

案例二:如下图,这是一个boost,boost的输出有个二极管,然后再经过电容,那这个电容的接地方式,就应该接到MOS管的GND,这样的话电容的升压环路是最小的,上左图的输出电容是直接接到底层的GND,再从底层回到芯片,这样的话导致环路过大,导致低频段的辐射很严重,如下左图所示,若改成右图那样,让电容从顶层接地,可以看到辐射变轻微了很多。

四:反馈(反馈电路设计,反馈环路)

反馈信号是根据负载轻重反馈给芯片内部运放,调节开关控制的信息窗口;反馈信号本身工作不稳定,反馈给芯片的信息就是错误的,会导致芯片误调整,引起输出电压的跌落或者升高,后端用电设备会因电压波动出现工作状态异常,甚至损坏。

反馈电阻的取值:

目前的DCDC电源模块采用电流反馈比较多,加入一个微弱的电流流过一个很大的电阻,就会很容易产生电压,很容易检测到DCDC输出电压的变换,此时就有一个误区,那就是以为电阻越大,电流越小,电压变化越明显,反馈也就越灵敏,但如果电阻越大,就意味着跌落的电压也就越多,电压波动的时候,就导致电阻两端的电压就不太稳定,而电阻越小,跟DC输出的电位差就越小,也就越稳定,但如果电阻越小呢,就会带来反馈的回应越迟钝的问题。综上,电阻需要折中取值,一般使用k级或者10k级别的,不要用100k级的,100k级的会很容易偏离。

反馈信号的稳定性:

影响反馈信号稳定性的因素,分为反馈信号电路设计和反馈信号PCB设计。 反馈电路设计:最重要的就是分压电阻参数的设计,然后是前馈电容补偿,在分压电阻的上偏置电阻上面加个电容前馈补偿或在下偏置电阻上加个电容,起到补偿或滤波的效果。 反馈信号PCB设计:第一是反馈的电从哪里取到,有时如果从滤波电容之前取,反馈本身就是有杂讯,所以反馈一定要在滤波电容之后取。第二是反馈两侧要加地线进行屏蔽,如果旁边走了一个电源或是其他的信号,那么就肯定会发生串扰。第三是反馈信号要采用差分布线处理,第四是环路面积要小,反馈线要尽量短,若反馈线拉得很长,就很容易收到外界信号的干扰,并且反馈线的影响也会很大。第五是反馈信号要远离干扰源,比如大电流的,强信号的,有电感的存在的。

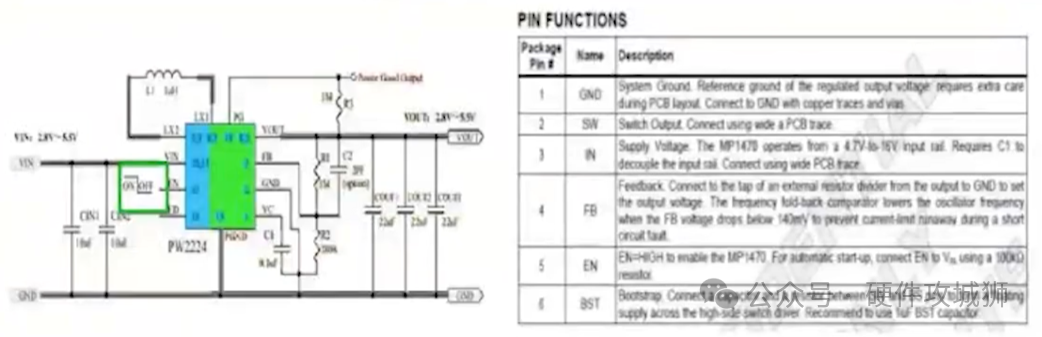

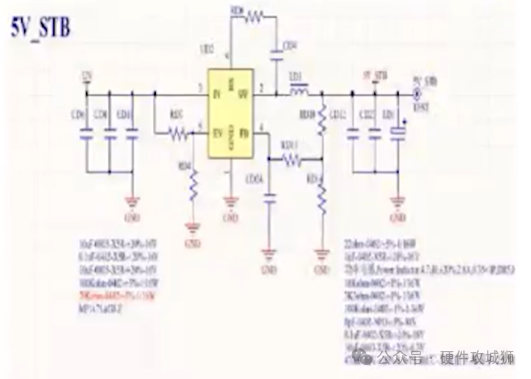

五:开启控制信号(EN脚开启电压设置,EN脚控制信号布线)

很多的芯片都有开启和关闭的动作,这就是控制信号,EN脚是控制DCDC芯片开关控制引脚,其控制电平的稳定是DCDC芯片可靠工作的重要条件,如果在这个电压上设计出了问题,就会引起EMC,首先的就是抗扰度。 EMC问题:当控制电平设置在芯片开启电压的边界值时,若抗扰度测试时EN脚电压波动偏离芯片门限电压,则会出现DCDC芯片误关闭的情况,引起输出电压跌落,导致后端用电设备工作异常。 EMC问题:EN脚电压用分压电阻给到,如果设计的分压电阻输出的电压高于芯片手册给的推荐电压,正常情况下没问题,但在做雷击浪涌等测试的时候让EN脚电压波动,可能就会导致误开或误关,如果误关并且输出端没有很大的电解电容去补偿能量的时候,就会出现问题了。 举例:下图为EN脚偏置电压设置偏低,静电放电测试后端电路工作异常。

举例:下图为EN脚偏置电压设置偏低,雷击浪涌测试后端芯片工作异常。

一般直接给的话,EN脚电压建议设计在2.8V以上(若芯片规格允许的话)。如果是EN脚有时序的话,就要考虑芯片的充电,如果GPIO的驱动电压不够的话,也会出问题。

03

DC-DC EMC问题调试技巧

一:输出电压问题调试

对于DCDC电源而言,首要就是保证输出电压的稳定性,如果遇到了输出电压跌落。 第一:EN脚的对策,EN脚增加高频滤波电容,调整上拉电源的电压值,EN脚控制信号防护设计,分压电阻参数调整。 第二:反馈电路的对策,反馈引脚增加对地高频电容滤掉杂波,反馈信号增加前馈电容加速反馈的速度,反馈分压电阻比例调整。 第三:输出电压稳定的对策,增加电解电容让它放电来补偿不足的输出电压,增加稳压二极管保证输出电压稳定在一个值上避免输出电压过高烧坏后面的负载,增加储能元件。

二:环路面积问题调试(开通环路,续流环路,主功率环路面积,环路低频磁场辐射,共环路耦合,散热)

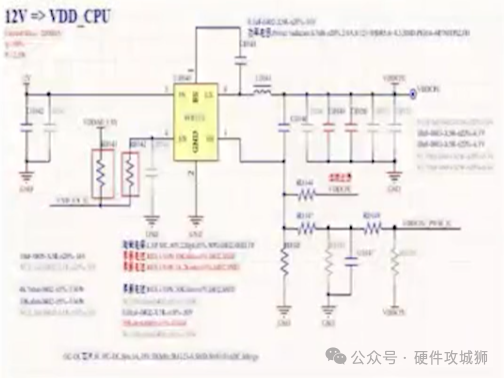

首先来看电流环路,如下图所示,所有的DCDC都有一个功率地,有时可能在电路中加高频旁路环路电容,那么这种电容都应该接到功率地上面去。对于buck而言,假如说以二极管的接地点为参考点,那输出高频电容会回到二极管那里来,此时的续流环路是最小的,对于开通环路而言,C1和C2的地接到二极管那里,从C1流向电感再流到C2,再回来到C1,此时环路最小,对于主功率环路而言也是一样的道理。之前是高频的分析,接下来看低频的情况,低频跟寄生电感无关(低频情况下寄生电感的电感量约为0)。

此时我们可以直到,画原理图十分关键,可以在画原理图的时候养成将环路标清楚,将路径标清楚(如下图那样)的习惯,在绘制pcb的时候就会有个参考。 接下来看寄生环路,如下图所示,电路中的参考地对大地而言实际上不是一个地,在模块上引出了一根线接到大地时,那么这个地线的寄生电感存在的时候是很高频的时候,此时如右下图可以看到,相当于形成了很多的寄生电容再接地,这种通路一般是不可控的,会形成电位差,此时我们就要让他尽可能以原理图的路径走,就要多点接地,让各个接地点都没有电位差。

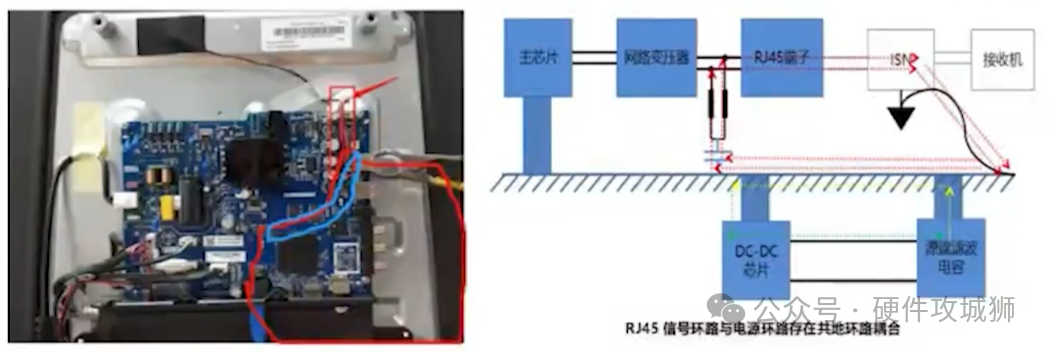

然后看共电流环路耦合,它是两个电流环路拥有共同的路径,弱信号被强信号干扰,干净信号被噪声信号耦合。它合是干扰问题产生的主要形式之一,也是传导测试超标的重要原因之一。在绘制PCB的时候,模拟地和数字地要分开,音频地和视频地分开,等等等等……但此时我们就会发现最后测试的时候一项也无法达标,所有分地的理论是没有问题的,但要弄明白分地的初衷是什么,分地的初衷是为了解决共环路耦合,共阻抗耦合,电流的泄放(比如雷击的时候雷电的电流直接流向地而不通过电路上的元件,如果要让电流往某方向走,就要将某方向的阻抗设计的最低)。 如下右图所示,dcdc的电流环路和网口的环路是同一个环路。此时测网络端传导的时候就出现了dcdc芯片的开关频率,并且在测试地环路的时候示波器夹子夹在不同的地方,环路就会发生改变,如果说此时夹到右上角的其他设备,可以发现地环路变得更长了,而且dcdc模块的噪声也会被引到网络上。

然后是电感磁场问题,首先可以考虑更换磁屏蔽电感防止磁场泄露,切断磁场耦合路径,这个就是会增加成本了。次是距离控制,通过空间衰减磁场强度。最后可以利用磁场穿过金属产生涡流效应,涡流磁场与原来磁场互相抵消。

三:开关噪声问题调试

对于开关噪声而言,有时会认为导通损耗等于关断损耗,实际上这是不对的,要分开设计,比如有时候想要导通速度慢一点,关断速度快一点。有时如果导通交叉面积大,就会让导通损耗比较大了,此时就让MOS管导通速度变慢一点,但如果说关断交叉损耗很小,即使导通速度快也无所谓了,但这时候实际上可以分开设计两个不同的驱动,不同的环路。 现在有一些芯片有抖频功能(另外细讲),也可以降低EMI。 解决方式:降低开关频率,开关频率低的时候,开关噪声和寄生振荡都会比较小,至于开关频率低的坏处,就是电感产生的低频磁场的辐射比较强,由于磁场容易受到空间的衰减,越是高频的磁场越容易衰减,而低频的磁场穿透性会更强,高频电流很容易受到电感的影响,而低频电流却不容易。 解决方式:遇到上冲振铃和下冲振铃可以增加吸收电路,如果RC设计小了抑制不了,加大了可能会引发其他问题,而又有可能因为芯片内部的布线导致振荡而无法处理,此时可以考虑电压钳位电路,下图上和下图下就是很鲜明的对比。

四:寄生参数问题调试

所有的寄生振荡都由几个地方产生:器件,PCB,结构,组合寄生参数。 解决方式:器件的寄生参数可以更换器件或者加吸收电路来解决。 解决方式:PCB的寄生参数可以通过优化布局来解决,或者优化接地,比如屏蔽的金属罩可以接地(一个反例:电感或变压器的漏磁场穿过金属罩产生涡流,由于涡流电流必须要回到原端,如果接地点不足,就导致高频电感两端电位差很大和辐射路径远)。 解决方式:在结构上可以在开孔,比如电脑电源就会开很多孔,不仅是为了通风散热,还可以避免高频寄生电感,这是从电流的角度出发的,如果从电位差的角度出发,如果寄生电感过大了的话,还会产生新的电位差。 解决方式:在增加电容或电感的时候,就要考虑是电压造成的干扰还是电流造成的干扰,电压造成的干扰就增加电容滤波,而加电感可以衰减旁路电容的电流,让辐射变小。 解决方式:增加阻尼,加磁珠(加电阻是破坏寄生振荡最有效的方式,但为了维持电流,肯定不能加电阻的),磁珠又有电感的特性又有电阻的特性,如果加了磁珠可能会产生电压应力,也就是反向的时候由于电压突变会产生反向电压,导致过冲。

五:传导问题和辐射问题调试

电源端传导问题:

电感空间磁场辐射:使用磁屏蔽电感/与ac电源输入端拉开距离

输出电源环路低频磁场辐射:与ac电源输入端拉开距离/衰减环路中低频噪声电流 共电源阻抗耦合:调整pcb布线采用点对点布线方式衰减输入电源线上的低频噪声电流

电信端传导问题:

共电源阻抗耦合:调整pcb布线采用点对点布线方式/衰减输入电源线上的低频噪声电流

共地环路耦合:电源信号环路与dcdc输入噪声分开/衰减输入电源线上的低频噪声电流/dcdc电路远离外部端子放置 电信端电路参数调整:Bob smith电路参数调整/Bob Smith电路电容接地点选择/电信差分信号与buck电感距离控制/buck电感使用屏蔽电感

辐射问题:

环路面积问题:开通环路面积控制/续流环路面积控制/开通高频旁路环路面积/续流高频旁路面积 寄生参数影响:开关MOS管寄生电容/PCB布线寄生电感/同步MOS管寄生电容/动态线分布电容/续流二极管寄生电容 滤波设计:开关环路或者续流环路增加高频磁珠/同步开关MOS管RC吸收/开关MOS管RC吸收/输入供电电源滤波设计/续流二极管RC吸收 寄生振荡:开关MOS寄生电容与PCB布线寄生电感振荡/续流二极管寄生电容与PCB布线寄生电感振荡/同步开关MOS管寄生电容与PCB布线寄生电感振荡/PCB布线寄生电感与高频开路寄生振荡

04

DC-DC EMC设计要点分析

一:原理图设计

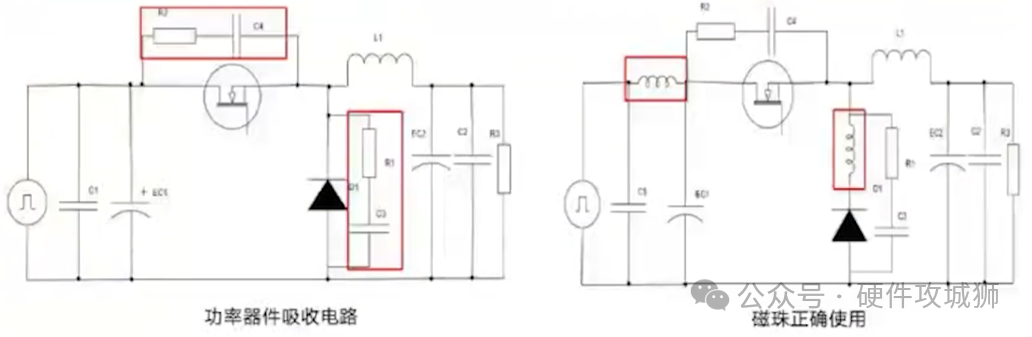

RC吸收设计,高频旁路设计,磁珠正确应用:

如果PCB的环路设计的合理,实际上可以不需要加吸收,也可以预留吸收电路焊接位,避免调试的时候改板。下图二极管的磁珠加的不正确,磁珠的高频会和RC产生谐振,应该让RC并联在二极管的两边,这样的话还可以让磁珠对二极管的应力产生的小一些(举一个反例:在电源输入端加一个磁珠,然后加电容到地,然后导致芯片烧毁,如果没有电容吸收电压,就会产生很高的电压应力,让芯片烧毁,正确的方式是先加一个高频电容再加磁珠,对于的电源输入端的电容先高频再低频还是先低频再高频的问题而言,在PCB布线很短的情况下问题不大,但在PCB布线很长的时候就要先高频再低频,因为高频有寄生电感,会引起寄生振荡小电容要放近一些,大电容可以远一点)。电容可以提供阻抗滤掉电压引起的干扰但会造成大的电流,而磁珠可以变成电流环进一步消耗电流,所以下图的磁珠如果加上效果会更好。

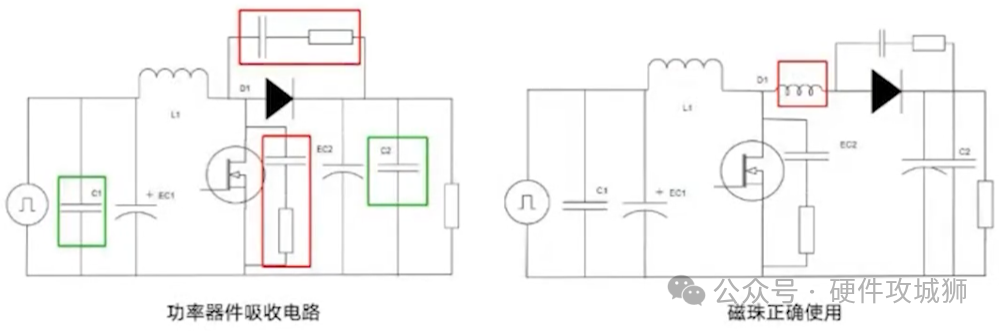

插入一个磁珠位置的问题,一般是哪里振荡,磁珠就串在哪里,磁珠的作用就是为了解决寄生振荡的问题,假如MOS管到二极管的走线过长会引起寄生振荡,那就串在这里,假如是MOS管到电感的走线过长引起的寄生振荡,那就串在那里,也可以直接留下预焊接位,哪个有问题串在哪里。然后看BOOST的设计,如下图所示,原理基本差不多。

滤波与防护设计:

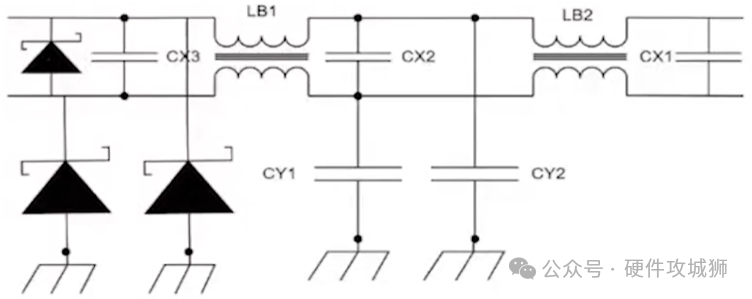

电源与外部连接滤波与防护的设计,静电放电防护与雷击浪涌防护。差模雷击防护与共模雷击浪涌防护。差模滤波与共模滤波,高频滤波与低频滤波设计。 如果是外部端口要考虑雷击浪涌防护,差模防护,共模防护,可以在正负之间并联一个TVS管做差模防护,正负分别对地是做共模防护,X电容做差模旁路,Y电容做共模旁路,避免外部线缆感应外部噪声,两个共模电感形成pai型滤波电路。下图最后一个电容有时候可以不加,跟噪声源有很大的关系,所谓的感性负载产生电压和容性负载产生电流(与常识恰恰相反),因为电感在通断的时候会产生一个感应电动势应对电流突变,噪声就来源于这里,电容在充电放电是电流在急速变化。如果电压成分较多的时候,在前面加个电容的话旁路效果就不一样,如果电流成分较多的时候,加电容也没关系,因为电容阻抗比较低(高频噪声),总的来说要靠电感量来设计。而如果不加CX2的话,两个电感串联,两级滤波就会变成一级,总的来说可以很灵活的调整这个滤波器,在PCB设计的时候就应该全部预留焊接位,因为不知道实际上的噪声是什么情况,在实际调试了之后,再来设计这个滤波电路。

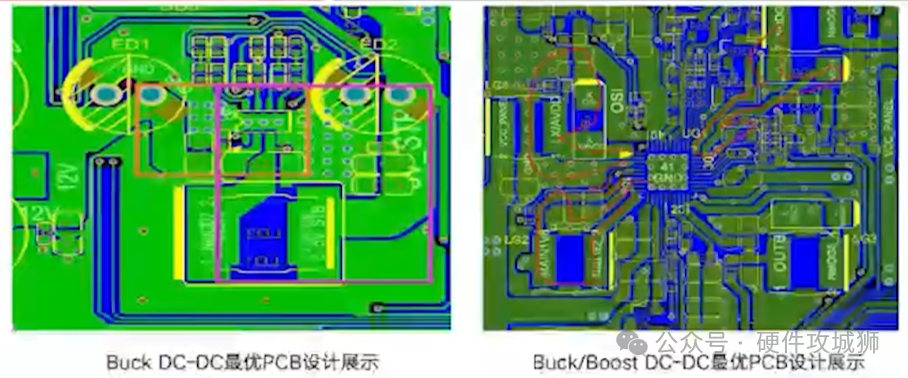

二:PCB设计

有关叠层,在高速信号过程中与叠层相关,而电源也跟叠层有关,由于功率原因,很多会使用多层板,而多层板又带来环路的改变,因此叠层和环路设计也需要注意。对于DCDC而言,首先就是参考地,保证环路最小,对于多层板而言,可以用中间层做参考,但一定要保证参考地在同一层,否则会导致环路面积直线上升。

审核编辑:黄飞

-

DC-DC电源基础知识(PPT版)2025-06-19 434

-

航天器DC-DC模块电源电磁兼容设计2025-05-30 29785

-

DC-DC转换电路的纹波分析2025-03-20 2289

-

DC-DC电源设计分析及使用注意2024-01-03 2273

-

介绍产生干扰源的DC-DC电路的工作原理2023-04-24 6489

-

DC-DC开关电源的开关波形产生高频振荡的原因2022-07-28 32446

-

LDO和DC-DC有什么不同?2021-11-17 1399

-

DC/DC电路啸叫声产生的原因2021-11-16 3441

-

DC/DC发出啸叫声的原因分析2021-11-09 3568

-

DC-DC降压2018-08-15 3675

-

DC-DC电路啸叫的原因2016-01-28 9452

-

DC-DC 高频噪声2013-01-08 2637

-

减少DC-DC Converter中的地弹2010-06-07 787

-

DC-DC基础入门教程 Advanced DC-DC Converters2009-10-31 40416

全部0条评论

快来发表一下你的评论吧 !