汤谷智能发布全栈RISC-V硬件仿真加速系统方案

描述

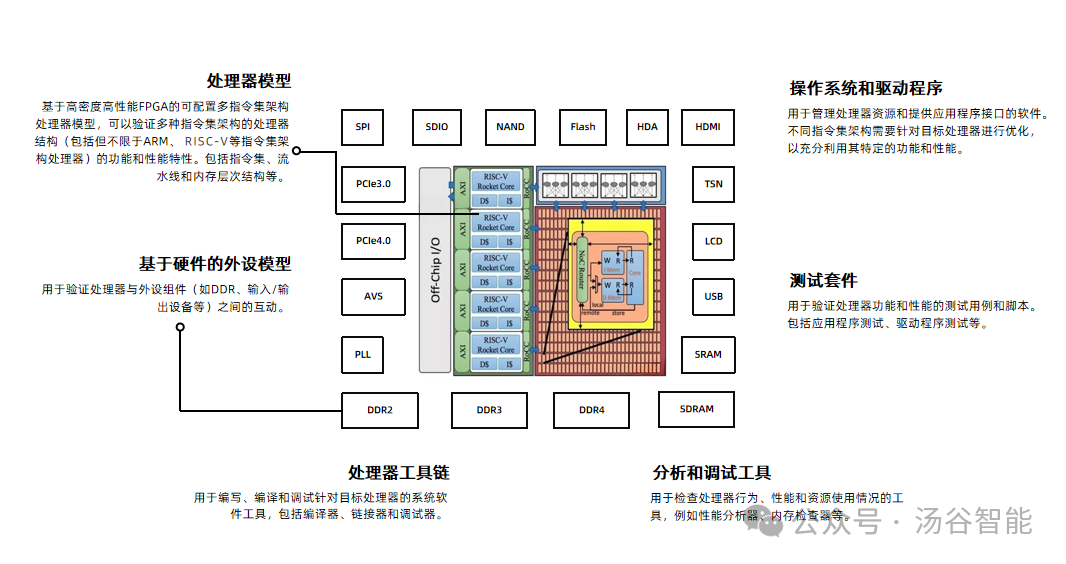

面向高性能计算、IoT、无线接入、音频、多媒体、消费类电子、边缘计算等迅速扩展的RISC-V使用场景,汤谷智能发布了基于自研Logic Giant原型验证硬件平台的全栈RISC-V硬件仿真加速系统方案。

方案可支持阿里玄铁、香山南湖等多款常用RISC-V Core,并同时支持Verilog及Chisel等多种设计语言,配合自研TGOriPartition软件工具,支持多核、大规模分割。支持MCU到AP多个处理器级别,流水线从2级到12级。方案支持基于RISC-V的SoC系统,常用外设齐全,可通过EDA工具选择不同的RISC-V Core和外设,自动生成可直接在原型平台运行的SoC系统,支持适配SoC系统的驱动软件及操作系统运行,极大提高开发效率。

从客户使用效果来看,方案可同时支持8路以上可编程独立时钟源,每一路都能支特全局时钟同步,传输距离为1.5米时,采用LVDS 传输性能可大于1.6Gbps,延迟小于900ps。采用自研的互联IP总线和电缆,超低延迟可同时运行512个RISC-V Core并保持系统统一同步运行,系统主频可达到8~10MHZ以上。

为了支持多个用户的同时使用的场景,方案中单个机箱可支持几十个虚拟用户和真实5用户同时使用,特别是真实5用户可动态独立使用分配到的FPGA逻辑资源,不与其他用户从逻辑、时钟、复位和外设等各种资源产生冲突。

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

重磅合作!Quintauris 联手 SiFive,加速 RISC-V 在嵌入式与 AI 领域落地2025-12-18 845

-

大象机器人×进迭时空联合发布全球首款RISC-V全栈开源小六轴机械臂2025-04-25 1995

-

芯来科技携手芯芒科技发布RISC-V CPU系统仿真平台2025-03-19 1900

-

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,赋能RISC-V高效落地2024-08-30 1779

-

润开鸿基于高性能RISC-V开源架构DAYU800通过OpenHarmony兼容性测评2023-12-14 2290

-

256核!赛昉发布全新RISC-V众核子系统IP平台2023-11-29 2079

-

阿里平头哥发布首个 RISC-V AI 软硬全栈平台2023-08-26 814

-

RISC-V,正在摆脱低端2023-05-30 2098

-

risc-v是什么意思2023-03-30 2201

-

新品发布|业界首款!润开鸿最新推出RISC-V 高性能芯片➕ OpenHarmony标准系统的智能硬件开发平台HH-SCDAYU8002023-01-13 2539

-

平头哥发布首个高性能RISC-V芯片平台“无剑600”2022-08-25 2454

-

阿里平头哥宣布开源玄铁RISC-V系列处理器2021-10-20 2461

-

阿里开源玄铁RISC-V系列处理器,大幅加速RISC-V软硬件技术融合2021-10-19 4127

-

为什么选择RISC-V?2020-07-27 5006

全部0条评论

快来发表一下你的评论吧 !