PCB叠层结构与阻抗计算笔记分享

描述

1. PCB叠层结构与阻抗计算

1.1. Core 和 PP

PCB由Core和Prepreg(半固化片)组成。

Core是覆铜板(通常是FR4—玻璃纤维&环氧基树脂),Core的上下表面之间填充的是固态材料;

常见半固化片类型:106,1080,2313,3313,2116,7628

PP原始厚度:7628(0.185mm/7.4mil),2116(0.105mm/4.2mil),1080(0.075mm/3mil), 3313(0.095mm/4mil )

实际压制完成后厚度:通常会比原始值小10-15um左右

常用铜厚:1/3oz、1/2oz、1oz、2oz

1.2. PCB的叠层机构和阻抗设计

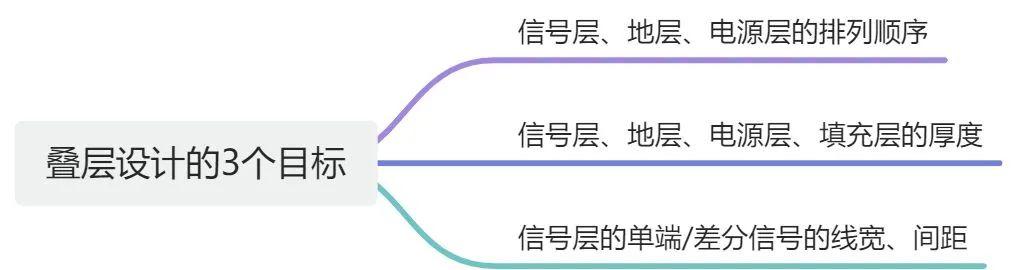

1.2.1. 层叠结构设计的先决条件

1.2.2. 层叠结构与阻抗设计的流程

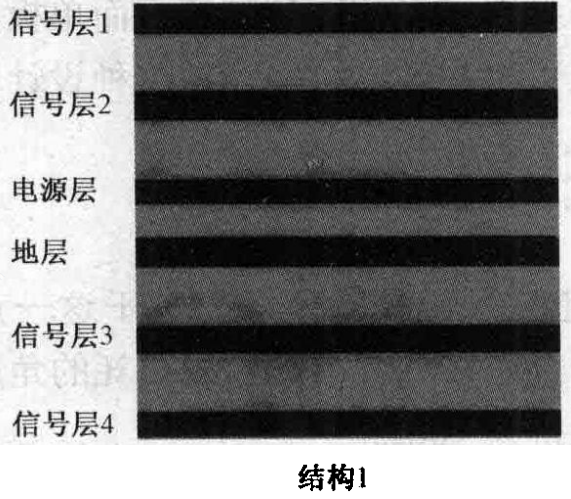

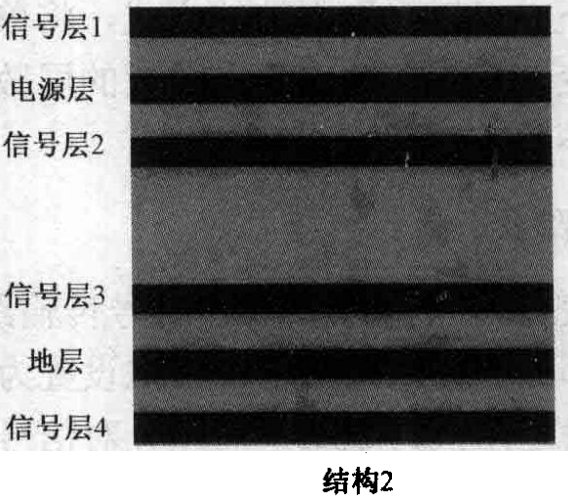

(1)信号层、地层、电源层的排列顺序(2种层叠对比)

a. 对结构1的分析

电源层与地层相邻,且距离较近,可以很好地实现电源与地之间的耦合。

信号层3与地层相邻,以完整的地层作为参考平面,因此信号完整性最好。

信号层2与电源层相邻,若电源层是完整的平面,则同样也能获得较好的信号完整性,但若电源种类不止一种,则电源层需分块,不完整的参考平面会导致信号回流路径不通畅,对信号完整性存在一定影响。

信号层1,4与信号层2,3相邻,很容易受到相邻信号层的影响,因此完整性最差。

b. 对结构2的分析

电源层与地层不相邻,耦合较差,无法形成有效的寄生小电容。

信号层1,2,3,4相邻层都能找到地层或电源层作为参考平面,信号质量相对结构1更好一些,其中,信号层1和4位于表层,而表层的阻抗控制比内层更难。因此,从信号完整性而言,信号层2和3要好于1和4。

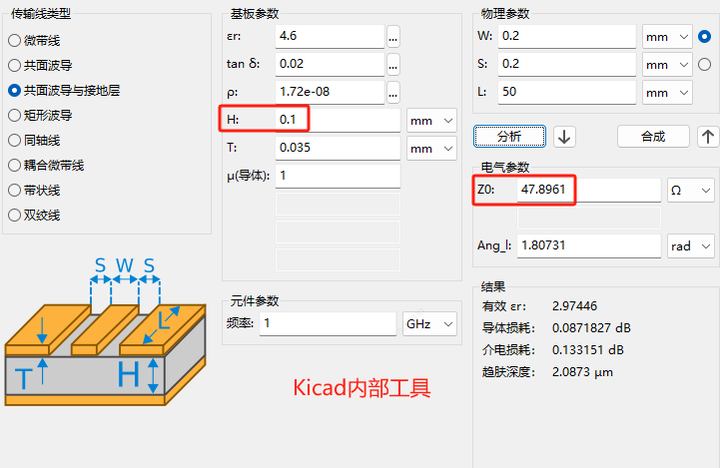

(2)线宽与层厚

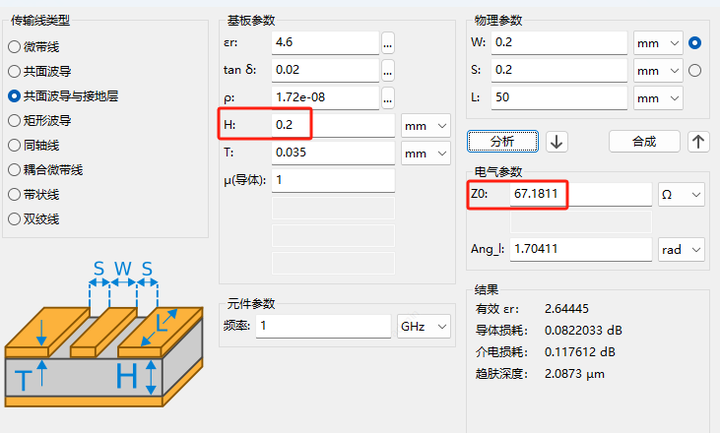

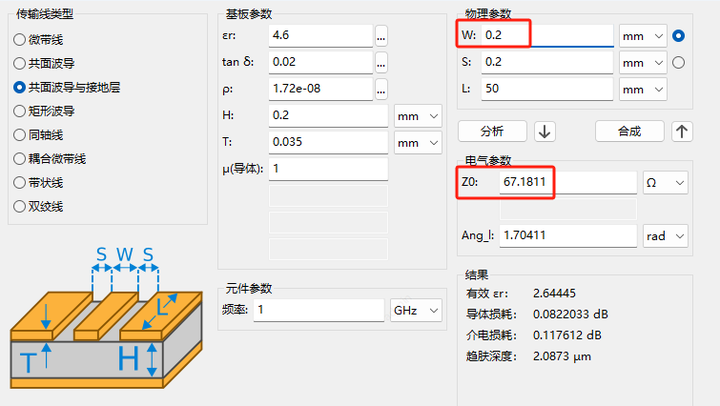

a. 改变参考层厚度0.1mm为0.2mm,阻抗从47Ω增加到67Ω

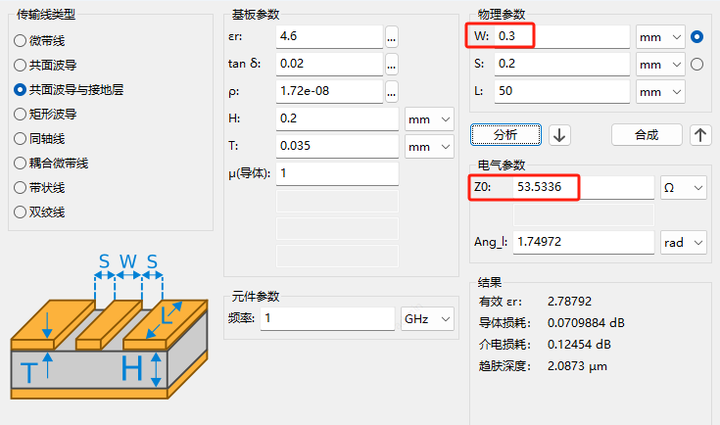

b. 改变线宽0.2mm为0.3mm,阻抗从67Ω增加到53Ω

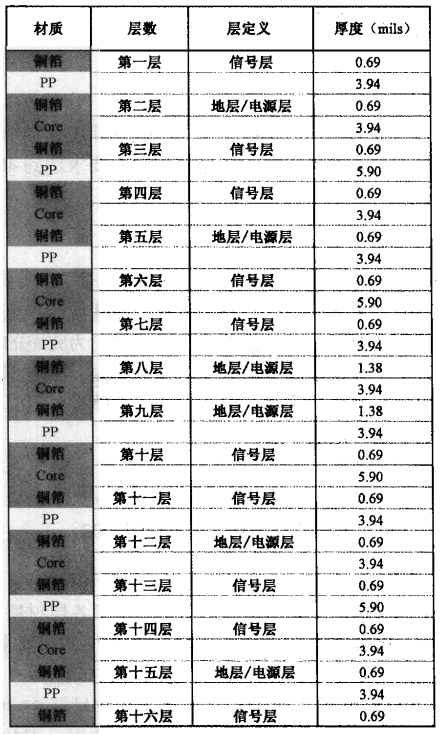

(3)叠层结构与阻抗设计的示例(16层板、信号最高频率400MHz)

a. 先决参数确定

单板层数:信号层8个,3个电源层,3个地层,2个表层(器件+信号)

单板厚度:2mm

目标阻抗:单端信号55±15Ω,差分信号100±15Ω

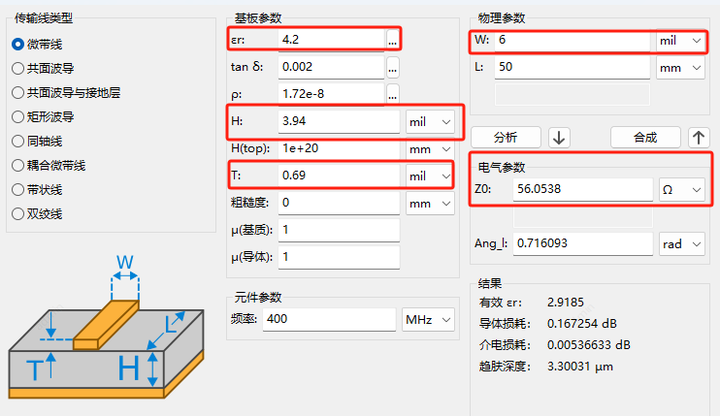

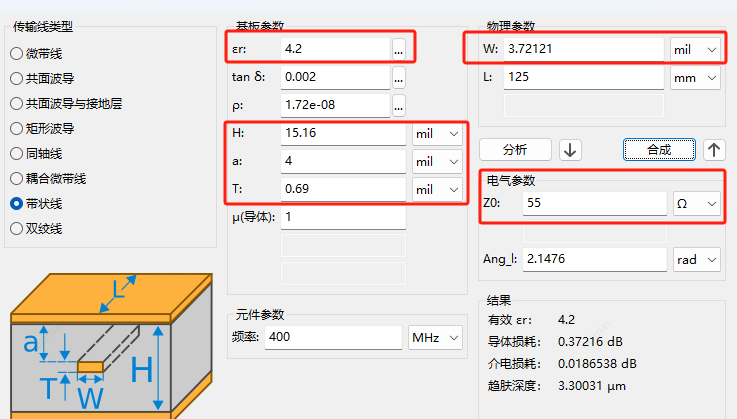

材质选择:FR4,Er=4.2,tanδ=0.002

b. 层叠结构与阻抗设计

层叠特征:PCB层叠结构在材质、厚度上完全对称

确定每层厚度,正确选取Core ,PP,Cu:

5*Core1 : 0.69+0.69+3.94 mil=5.32 mil

2*Core2 : 0.69+0.69+5.9 mil=7.28 mil

6*PP1: 3.94 mil

2*PP2: 5.9 mil

Cu : 0.69 mil

总厚度:5*Core1+2*Core2+6*PP1+2*PP2+2*Cu=77.98 mil = 1.98 mm

确定每层厚度后,计算各层信号走线宽度:

表层单端信号

内层单端信号

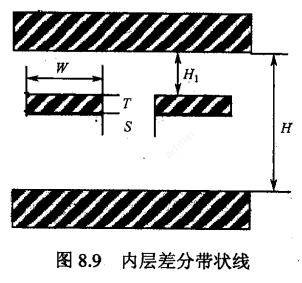

内层差分信号(SI9000计算)

c. 电源层、地层的确定

层叠已经确定了电源层或地层的位置,这一步确定第二、五、八、九、十二、十五层对应电源层还是地层。

第八,九层位于PCB的中央,紧密相邻,一层作为电源层,另一层作为地层,能起到很好的耦合效果。考虑到需分割的电源层(由四种电源共用)的电源平面较零碎,更需要与完整的地平面的耦合,因此,可确定第八层为地层,第九层为分割的电源层;

第二,十五层直接与表层相邻,从EMC的角度考虑,应选择为地层;

第五,十二层用作为2.5V和3.3V的电源平面。

在确定好电源层和地层后,还需相应地为信号层制定如下规则:

第十层的主要参考平面是第九层,而第九层是分割的电源层,对信号回流的影响较大,因此不建议在第十层走高速信号,对于一些非重要的信号,如控制信号,JTAG信号等,由于它们的阻抗控制要求较弱,可走在第十层。

第七层的主要参考平面是第八层,第八层是完整的地平面,可为第七层提供很好的回流路径,但这两层之间填充的材质是PP,PCB制成后,在阻抗控制上可能存在一定偏差。因此,第七层可走高速信号,但对一些非常关键的高速信号,如单板上速率达到400MHz的差分对总线SPI4.2,不建议走在第七层。

第三层的主要参考平面是第二层,而第二层是完整的地平面,且两层之间采用固态材质填充,阻抗控制较好,适于走高速关键信号,同理,第十四层也适于走高速关键信号。

第四层的主要参考平面是第五层,第五层是完整的2.5V电源平面,两层之间用固态材质填充,可将高速关键信号走在第四层。在本设计中,有大量的DDR SDRAM接口信号线,其中,DDR SDRAM的地址,控制信号等都以2.5V为参考,建议将这些信号也走在第四层。

第十三层的主要参考平面是第十二层,第十二层是完整的3.3V电源平面,两层之间用固态材质填充,高速关键信号可走在第十三层,同时,建议将由3.3V供电的许多单端信号,如时钟信号等,走在第十三层。

第六,十一层的主要参考平面分别是第五,十二层,与参考平面之间用PP填充,阻抗控制可能存在偏差,因此,在这两层上可走高速信号,但不建议走非常关键的高速信号。

设计时需注意,第三,四层,第六,七层,第十,十一层,第十三,十四层,这四对信号层彼此相邻,存在互相干扰的可能,因此在走线时,相邻信号层应正交走线,如第三层走线方向成横向,则第四层走线应成纵向。

【以上信息由艾博检测整理发布,如有出入请及时指正,如有引用请注明出处,欢迎一起讨论,我们一直在关注其发展!专注:CCC/SRRC/CTA/运营商入库】

-

DDR电路的叠层与阻抗设计!2023-12-25 2195

-

RK3588 PCB推荐叠层及阻抗设计2023-08-01 4284

-

【华秋干货铺】一文轻松搞定PCB叠层和阻抗设计2023-07-27 1528

-

PCB叠层和阻抗设计(RK3588方案)2023-07-20 1553

-

一文轻松搞定PCB叠层和阻抗设计2023-07-19 2111

-

浅谈PCB叠层设计原则及阻抗设计2023-07-18 2320

-

PCB叠层结构设计详解2022-09-30 2929

-

关于PCB叠层及阻抗计算2021-03-22 1755

-

总结了PCB设计叠层算阻抗的4大注意事项 帮助提高计算效率2018-01-22 6700

-

【珍藏版】PCB阻抗设计与叠层方案2016-07-26 1715

-

PCB叠层设计及阻抗计算2016-06-02 20296

-

PCB叠层设计2016-05-17 4653

全部0条评论

快来发表一下你的评论吧 !