CCD与CMOS图像传感器的比较(CMOS Sensor原理)

MEMS/传感技术

描述

摄像机用来成像的感光元件叫做Image Sensor或Imager。目前广泛使用的2种Image Sensor是CCD和CMOS Image Sensor(CIS)。

前言

在数码摄影机市场上已经广泛应用了CCD技术,但是CCD需要消耗大量的能量和相当多的支持芯片。所以CMOS Image Sensor应运而生。其每个像素都可以进行自己的电荷转换,从而显著减少产生图像所需要的能量和支持电路。此外,CMOS Image Sensor采用与大多数微处理器和存储器芯片相同的材料和技术制造,使其更容易制造并且更具成本效益,所以被手机以及其它移动产品广泛使用。这里主要将以CMOS Image Sensor为主详细介绍。

1 CMOS Sensor 原理

CMOS 是英文Complementary Metal Oxide Semicondutor 的缩写,这是一种主流的半导体工艺,具有功耗低、速度快的优点,被广泛地用于制造CPU、存储器和各种数字逻辑芯片。基于CMOS 工艺设计的图像传感器叫做CMOS Image Sensor(CIS),与通用的半导体工艺尤其是存储器工艺相似度达到90%以上。

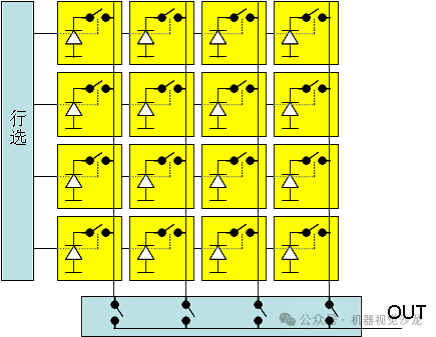

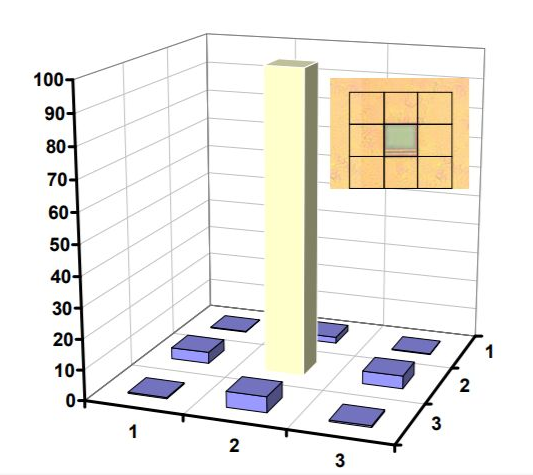

CMOS图像传感器采用CMOS开关来切换各个光电二极管的信号,如图1所示,每一个像元由一个光电二极管和一个CMOS开关构成。当行驱动电路选中某一行时,此行像元输出信号的CMOS开关导通,其余行的CMOS开关不导通,此行像元的光电信号传输到列选多路器。列选多路器也是由一系列的CMOS开关构成,依次将此行的信号顺序联接到输出端,完成一列信号的顺序读出。

图1 CMOS图像传感器原理 2 CCD图像传感器

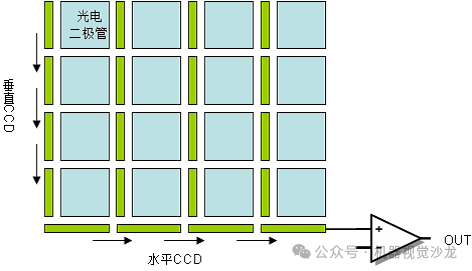

CCD 器件实质上是一种模拟移位寄存器。其原理是在时钟的控制下,将信号电荷由一个势阱转移到另一个势阱,从而实现模拟信号的移位转移。CCD 图像传感器利用CCD 器件的信号转移功能来实现电扫描。如图2 所示为CCD 图像传感器的工作示意图,信号的多路转换由垂直转移CCD 器件及水平转移CCD 器件两部分组成。在实际的CCD图像传感器中,光电转换器件与垂直CCD 器件是集成在一起的。垂直CCD 器件将每一行的光电二极管信号顺次转移到水平CCD器件上;而水平CCD器件将这一行信号转移到输出端。重复以上过程,形成一场图像信号。

图2 CCD图像传感器原理

3 CCD与CMOS图像传感器的比较

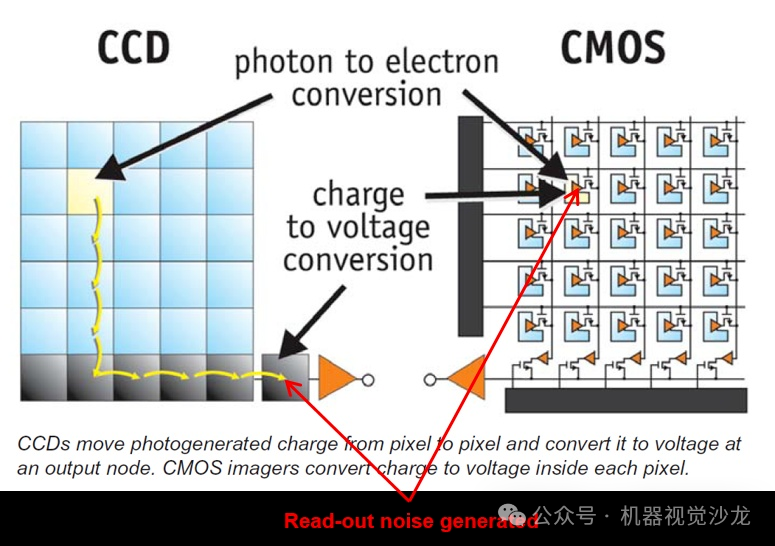

CCD与CMOS的主要区别如下图3所示,CCD 器件通常只有一个电荷-电压转换器(Charge-Voltage Converter),当Sensor读出像素数据时,每一行像素中积累的电荷需要在行电压的控制下一步步“蠕动”到下一行,直到最终抵达阵列所属的行缓冲(Row Buffer),然后开始在列电压的控制下继续一步“蠕动”到阵列出口处的电荷-电压转换器,完成读出过程。CCD的一个主要优点在于所有像素共享同一个电荷-电压转换器,所以像素一致性非常好。相比之下CMOS每个像素都有自己专用的电荷-电压转换器,一致性很不容易控制。当CCD像素数多于200万时,所有像素共用一个电荷-电压转换器会严重影响读出速度,所以此时会考虑把像素设计成两个或四个阵列,每个阵列配备专用的行缓冲和电荷-电压转换器,可以成倍加快读出速度。

图3 CCD与CMOS的主要区别

4 CMOS Sensor像素结构

被动像素 (Passive Pixel)

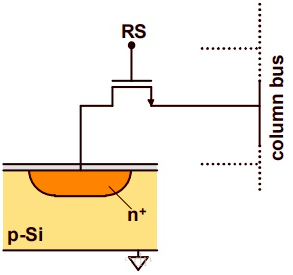

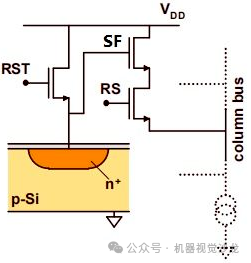

最简单的Pixel结构只有一个PN结作为感光结构,以及一个与它相连的reset晶体管(RS)作为一个开关,如图4所示:

图4 单PN节像被动素结构体

Passive Pixel结构的工作方式如下:

开始曝光前,像素的行选择地址会上电,于是RS使能,连通PN结与列选择器(Column Bus),同时列选择器会上电,使PN结上加高反向电压(如3.3 V),短暂延时后PN结内电子空穴对达到平衡,于是reset 操作完成,RS 信号失效,隔断PN结与columnbus的连通。

开始曝光时,PN结内的硅在吸收光子激发出电子-空穴对。受PN结内电场的影响,电子会流向PN结的n+端,空穴会流向PN结的p-substrate。因此,曝光后的的PN结反向电压会降低。

曝光结束后,RS再次使能,读出电路会测量PN结内的电压,该电压与原反向电压之间的差值即正比于PN结接受到的光子数。

在读出感光信号后,会对PN结进行再次reset,准备下次曝光。

当RS使能且列选择器通高电平时,在电路原理上相当于对PN结的电容进行充电,但是充电后得到的电压值却有一定的随机性,一方面每个PN结的实际电容大小会服从一定的概率分布,结与结之间存在固定的偏差,这会构成一种固定模式噪声(Fixed Pattern Noise, FPN);另一方面由于电路中存在暗电流噪声,即使是同一个结每次充电后得到的实际电压也不完全一样,这就构成了另一种模式的噪声,它与PN结的结构、温度和结电容大小都有关,称为kTC噪声。

主动像素 (Active Pixel)

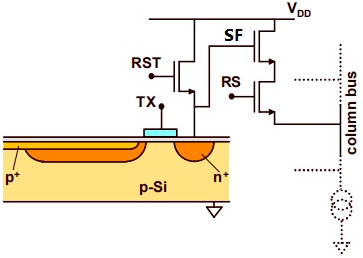

目前主流的CMOS传感器都采用Active Pixel 结构设计。如图5所示的Active Pixel 结构称为3T结构,每个像素包含一个感光PN结和3个晶体管,即一个复位管RST,一个行选择器RS,一个放大器SF。

图5 3T主动像素结构体

Active Pixel 结构的工作方式如下:

复位。使能RST给PN结加载反向电压,复位完成后撤销RST。

曝光。与Passive Pixel 原理相同。

读出。曝光完成后,RS会被激活,PN结中的信号被SF放大后读出。

循环。读出信号后,重新复位,曝光,读出,不断输出图像信号。

基于PN结的Active Pixel 流行于90年代中期,它解决了很多噪声问题。但是由PN结复位引入的kTC噪声却并没有得到解决。

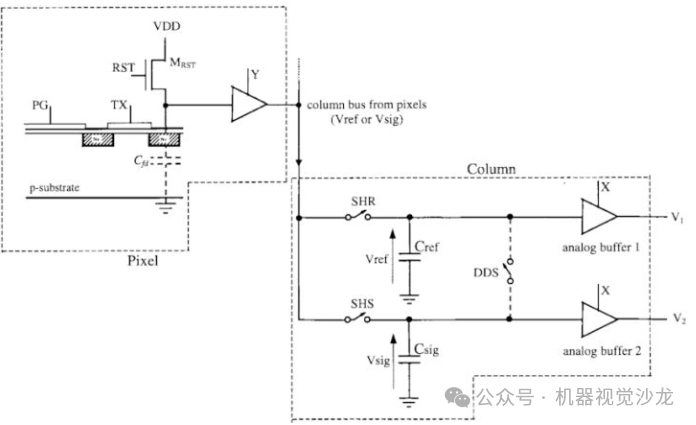

PPD结构

PPD(Pinned Photodiode Pixel)的出现是CMOS性能的巨大突破,它允许相关双采样(CDS)电路的引入,消除了复位引入的kTC噪声,运放器引入的1/f噪声和offset噪声,如图6所示。

图6 PPD结构

PPD结构的工作方式如下:

曝光。

复位。曝光结束时使能RST,将读出区(n+区)复位到高电平。

读复位电平。读出n+区的电平,其中包含运放的offset噪声,1/f噪声以及复位引入的kTC噪声,将读出的信号存储在第一个电容中。

电荷转移。使能TX,将电荷从感光区完全转移到n+区准备读出,这里的机制类似于CCD中的电荷转移。

读信号电平。将n+区的电压信号读出到第二个电容。这里的信号包括:光电转换产生的信号,运放产生的offset,1/f噪声以及复位引入的kTC噪声。

信号输出。将存储在两个电容中的信号相减(如采用CDS,即可消除Pixel中的主要噪声),得到的信号在经过模拟放大,然后经过ADC采样,即可进行数字化信号输出。

PPD像素结构有如下优点:

读出结构(n+区)的kTC噪声完全被CDS消除。

运放器的offset和1/f噪声,都会因CDS得到明显改善。

感光结构因复位引起的kTC噪声,由于PPD电荷的全转移,不再存在。

光敏感度,它直接取决于耗尽区的宽度,由于PPD的耗尽区一直延伸到近Si−SiO2界面,PPD的光感度更高。

由于p-n-p的双结结构,PPD的电容更高,能产生更高的动态范围。

由于Si−SiO2界面由一层p+覆盖,减小了暗电流。

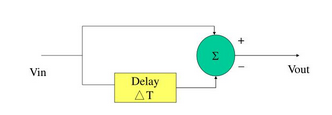

双相关采样(CDS)

双相关采样(Correlated Double Samping),其基本思想是进行两次采样,先采样一个参考信号用于评估背景噪声,延迟很短时间后再采集目标信号,从第二次采样中减去参考信号即得到去除了大部分背景噪声的目标信号,其原理模型如下图7所示。

图7 去噪原理模型

CDS成立的条件是在两次采样间背景噪声的幅度变化不大,因此它对去除固定噪声(FPN)和低频噪声效果比较理想,如1/f噪声,kTC噪声等。

图8 CDS电路模型

5 CMOS Sensor特性

CMOS Sensor的本质是计量光电转换事件的线性传感器,在一定意义上可以说是光子计数器,Sensor上每个像素的读值都反映了指定时间内该像素捕获光子的数量。一个理想的Sensor应该具备以下一些特性:

输出与输入恒成正比(无Sensor噪声,只有信号本身的噪声)

输入输出均可以无限大

高灵敏度,小的输入激励大的输出

高帧率

高分辨率

低功耗

工艺简单

低成本

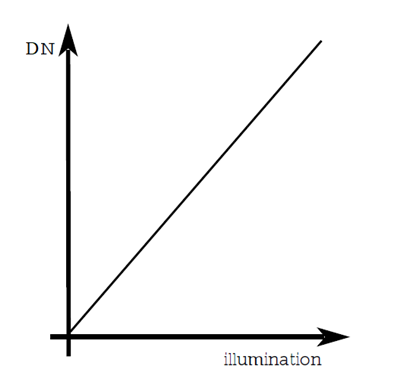

理想CMOS Sensor 的响应特性下图所示:

图9 理想sensor响应特性

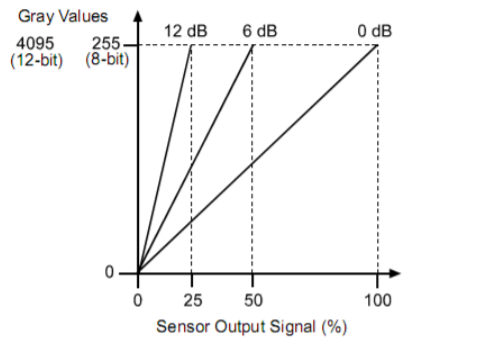

图10中直线的斜率决定了单位输入能够激励的响应大小,这个斜率称为增益系数(Gain)。Sensor 会提供一组接口用于调节实际生效的增益值。

图10 理想Sensor响应特性曲线

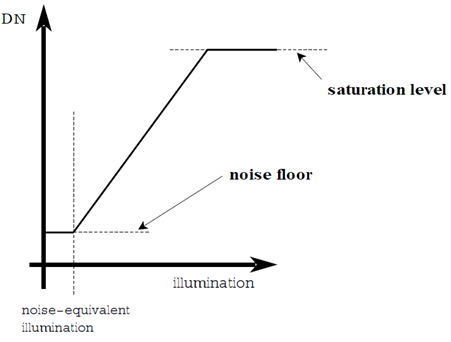

而实际的Sensor只能是在一段有限的区间内保持线性响应,对于幅度过小或者过大的输入信号会不能如实地表示。

图11 实际sensor响应特性

6 CMOS Sensor噪声(Noise)

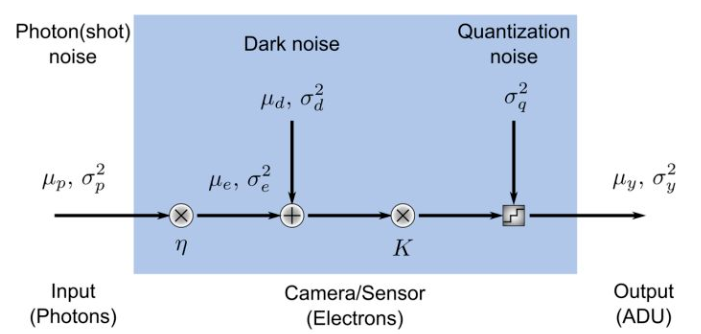

假设照明强度恒定、均匀,相机拍摄图像中的噪声是测量信号中空间和时间振动的总和。下图以传递函数的形式总结了CMOS Sensor 光、电转换模型以及几种主要噪声的数学模型。

图12 传递噪声模型 下图13更加细致地描述了CMOS Sensor 成像过程中各种噪声的来源和作用位置。

图13 噪声的来源途径

暗电流噪声(Dark Noise)

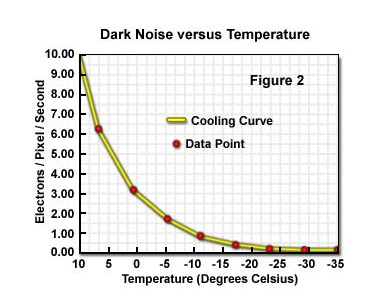

硅片中电子的热运动会导致一些价电子随机激发至导带中形成暗电流(Dark Current),所以即使完全没有光子入射,Sensor也会存在一定的信号输出。在曝光过程中,暗电流的随机变化即形成暗散粒噪声。暗电流变化的主要原因是电子穿过PN结时会遇到PN结的电势屏障(Darrier),电子穿越屏障需要经历动能-势能-动能的转换过程,所以需要耗费一些时间。暗散粒噪声在统计上服从泊松分布,与光信号的高低水平无关,但与传感器的温度有关,一般的规律是温度每升高8°C暗电流翻一倍。所以在设计电路时必须注意把容易发热的电子元件尽可能布置在远离Sensor的地方。

图14 暗电流随温度变化规律

读出噪声

该噪声是在产生电子信号时生成的。Sensor使用AD转换器(ADC)将模拟放大器输出的模拟电压采样为数字电压。由于数字信号的精度总是有限的,通常为10比特至14比特,幅值位于两个相邻数字之间的模拟信号会四舍五入到最接近的数值,所以这个过程会引入量化噪声,这是读出噪声的重要组成部分。该噪声由传感器的设计决定,意义是至少需要多少个电子才能驱动读出电路的ADC变化一个比特。它与信号高低水平和传感器温度无关。

光电流噪声(Shot Noise)

该噪声是与落于传感器像素上光子相关的统计噪声。在微观尺度下,光子流到达传感器的行为在时间和空间上都是不均匀的,就像统计高速公路上的车流,有时车流比较密集,过一会又变得稀疏。有时左边的车道密集,过一会右边的车道密集,整体上其统计规律符合泊松分布。光子散粒噪声是与被测信号的高低水平有关的,与传感器温度无关。

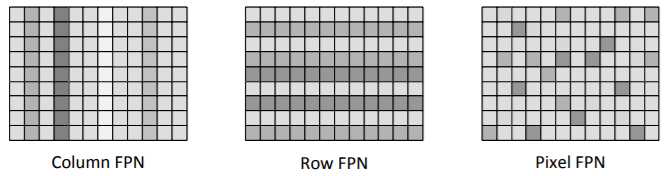

固定模式噪声(FPN)

该噪声是由像素的空间不均匀性引起的,CMOS Sensor 每个像素内都配置一个电荷电压放大器,每行、每列都有一些晶体管用于控制像素的复位和读出,这些器件的工作参数相对理论值的漂移就构成一种固定模式噪声。另外,坏像素、瑕疵像素也可以视为一种固定模式噪声,其效果大致上可以用下面的示意图15模拟。

图15 FPN 模型

复位噪声

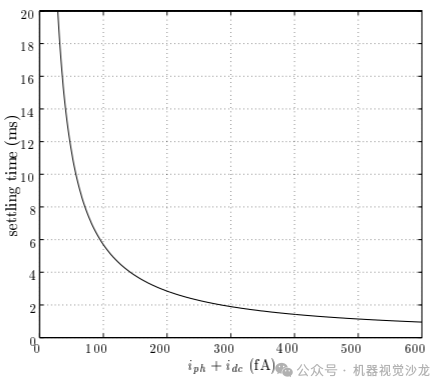

卷帘曝光方式需要在先对势阱复位,将势阱中自由积累的电荷全部释放,为后续的读出准备。但是由于暗电流的存在,每次复位后都会残留一些大小随机的噪声信号,即复位噪声,其大小与像素结构、芯片温度、PN结电容有关,因此也称为kTC噪声。像素的复位是需要一定时间的。定量的研究表明,即使是采用较大的复位电流,一般也需要1ms以上的时间才能将电荷释放干净,如下图16所示。

图16 电荷释放曲线

实际的复位控制信号通常会短于1ms,因此下一帧图像多多少少会残存一些上一帧图像的影子,这个残影叫做Image Lag,也是噪声的一种形式。

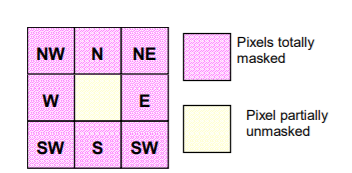

串扰噪声(Crosstalk)

在通信领域中指两条信号线之间由于屏蔽不良而发生了的信号耦合,一条线路上的信号通过线缆间存在的互感和互容馈送到了附近的信号线上,在模拟通信时代可能导致听到别人的通话。在Sensor领域,串扰指的是入射到一个像素A的光信号没有在这个像素里被捕获,反而被其周围的像素B捕获,导致B产生了不该有的信号。

在下图17例子中,粉色表示的是不透光的像素,不应该有任何输出,黄色表示正常像素,应该有输出。实际上,光子是可以在硅片中穿透一定的距离的,从而有机会进入到粉色像素的感光区,从而变成粉色像素的信号,这就是CMOS Sensor的串扰机制。

图17 串扰模型

从下图18可以看出,波长越长,串扰越严重,某些像素位置串扰能量可以达到5%。

图18 波长与串扰能量曲线

7 CMOS Sensor工艺结构

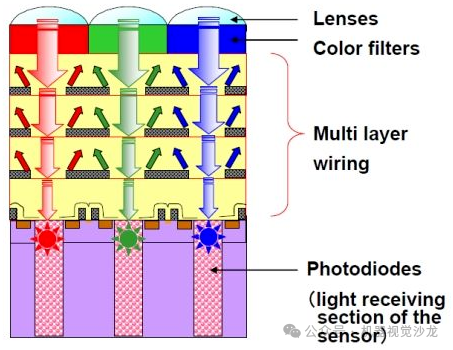

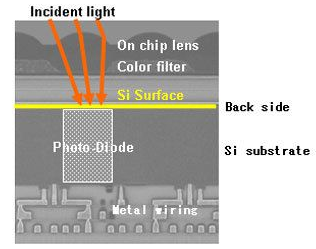

前照式工艺(FSI)

传统FSI工艺的一个主要不足之处在于光敏PN结与滤光膜和微透镜之间需要制造若干层电路结构,由于电路高度问题会限制PN结可收集光线的面积和角度,同时光线在前进过程中会与电路结构发生吸收、散射,所以会增加光能的损耗,如下图19所示。

图19 FSI工艺结构体

背照式工艺(BSI)

随着半导体工艺的进步,人们发现其实可以将wafer打磨得非常薄,让光线穿透wafer,从背面入射到感光PN结,这个想法无论在技术上还是成本上都已经变得可行,于是就产生了背照式工艺(BackSide Illumination, BSI)。

图20 BSI工艺结构体

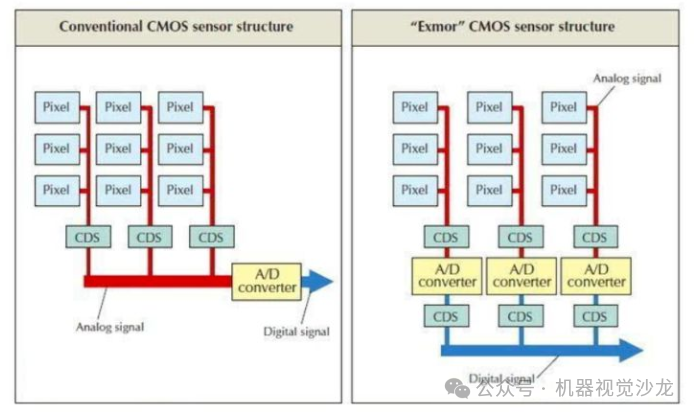

8 CMOS Sensor 进展 Sony 于2007年推出第一代Exmor系列CMOS 图像传感器。与传统CIS技术相比,Exmor 的主要特点是为每列像素配置了专用ADC和额外的CDS。由于ADC单元与像素的物理距离更近,并且由于大规模并行化可以降低单个器件的工作频率,所以极大地改善了Sensor的噪声特性。而新增的CDS又进一步抑制数字噪声。

图21 CDS改进对比

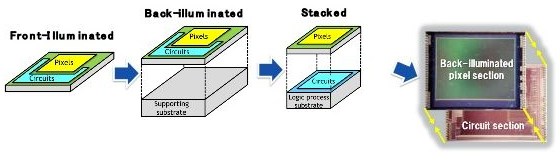

随着制造技术的进一步演进,在背照式工艺的基础上又发展出了堆栈式(Stacked)工艺。顾名思义,堆栈式工艺把两片或者更多片硅片上下堆叠在一起,最上层硅片全部用于制造像素的感光区,而sensor 控制所需的模拟、数字逻辑全部移到下层硅片,所以感光区占Sensor靶面尺寸的比例可以接近100%,终于达到了Sensor效率的巅峰。

图22 FSI,BSI,Stacked结构对比

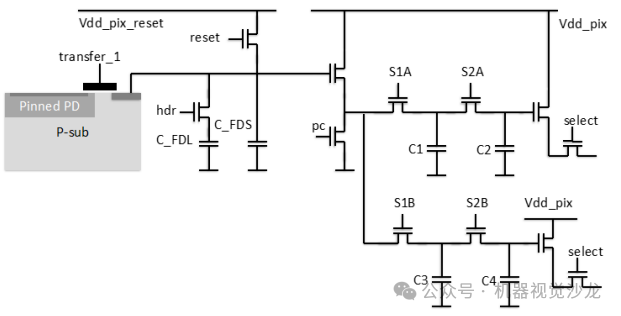

实际上,CMOS Sensor 也可以设计成支持Global Shutter曝光方式。与CCD 类似,Gobal Shutter 的实现原理是每个曝光像素都伴随一个存储电容,感光阵列上所有像素同时曝光,然后光电子立即被转移到存储电容上并锁定,等待读出电路读出。下图是一种较新的Global Shutter 像素设计,该设计支持两种不同的增益系数,因此支持HDR功能。

图23 Global Shutter Pixel 结构

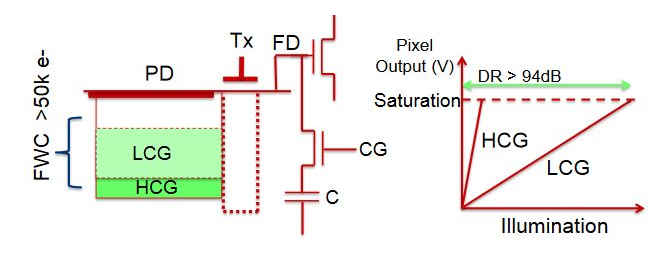

DCG 这种模式由OmniVision提出,原理是每个像素可单独控制增益(使用下图中的CG信号),当工作在HDR模式时,只进行一次曝光,但分两次读出,一次使用HCG (High Conversion Gain)捕捉暗部信息,一次使用LCG(Low Conversion Gain)捕捉亮部信息。

图24 DCG Pixel 结构

审核编辑:黄飞

-

cmos图像传感器的应用2020-06-20 3730

-

CMOS与CCD图像传感器到底有什么差别2019-11-26 3863

-

IBM进军CMOS图像传感器2018-11-19 2422

-

新型CMOS图像传感器设计2018-11-14 2882

-

CMOS图像传感器的原理参数和CCD图像传感器有什么区别等资料概述2018-11-07 3704

-

基于CMOS或CCD图像传感器的经典设计汇总2018-05-25 3210

-

CCD与CMOS图像传感器特点比较2016-03-16 1022

-

CCD和CMOS图像传感器的比较2015-09-06 15444

-

基于CCD与CMOS的图像传感技术2011-02-01 1457

-

CMOS与CCD图像传感器的分析研究2010-11-22 1373

-

CMOS图像传感器,CMOS图像传感器是什么意思2010-03-02 3095

-

监控用CMOS与CCD图像传感器对比2010-01-11 2895

-

CCD与CMOS图像传感器技术简介2009-11-07 1093

-

CCD和CMOS图像传感器性能比较2009-04-07 812

全部0条评论

快来发表一下你的评论吧 !