SD NAND的CLK引脚的注意事项和走线规范

电子说

1.4w人已加入

描述

CLK的作用和注意事项

SD NAND的时钟引脚(CLK)的作用是提供一个时钟信号,用于同步数据传输。时钟信号是由主设备(如微控制器或存储控制器)提供的,用于确保SD NAND和主设备之间的数据交换是按照相同的时序进行的。

1、时钟频率: CLK信号的频率取决于TF卡和主设备之间的通信协议和速率。时钟频率不能超过TF卡规格中定义的最大工作频率,否则可能导致通信错误或数据丢失。

2、时序要求: 时钟信号的上升沿和下降沿需要符合TF卡规格中定义的时序要求。违反时序要求可能导致通信故障。

3、电压要求: 时钟信号的电压应符合TF卡规格中定义的电气特性要求。过高或过低的电压可能对TF卡产生不良影响。

4、连接方式: 确保CLK引脚正确连接到主设备,并且按照TF卡规格连接。通常,CLK引脚连接到主设备的时钟输出引脚。

5、时钟同步: 在进行TF卡通信之前,主设备和TF卡之间需要建立正确的时钟同步。这通常由主设备负责。

6、时钟停止: 在TF卡不被使用时,可以将时钟信号停止以降低功耗。但是,要确保在重新开始通信之前正确地重新启动时钟。

CLK的走线规范

1、CLK的走线越短越好;

2、CLK避免走线经过大电感下面,或者其他干扰强的器件下面;

3、CLK走线不需要加电容滤波,加电容滤波会导致时钟信号变差,

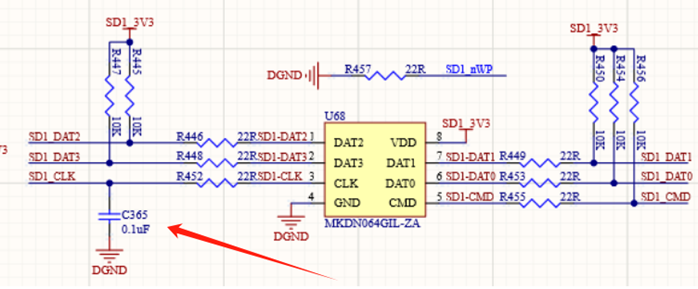

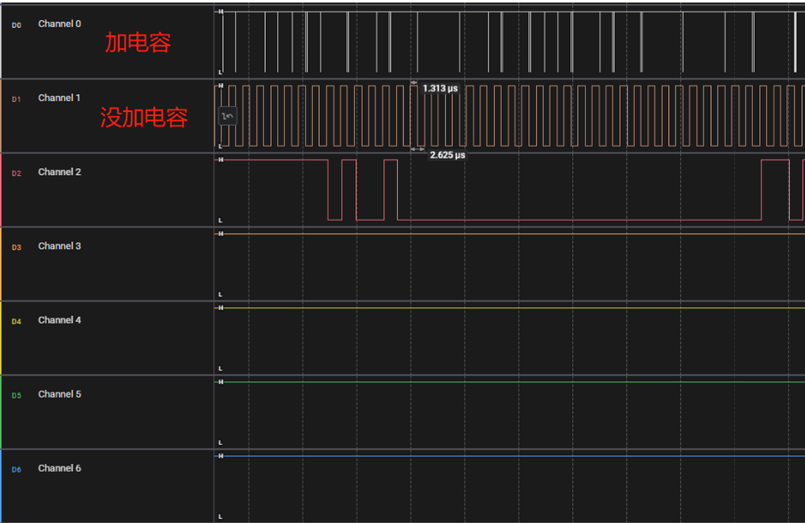

例如下面是CLK加电容的设计原理图和时序

这是同一个程序输出的时钟信号,加了电容的时钟信号看起来不正常,实际也是SD NAND初始化异常。

审核编辑 黄宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

PCB参考设计规范 PCB设计注意事项2009-11-30 6799

-

FPC柔性板走线的注意事项有哪些2020-04-16 3286

-

请问印制板铜皮走线有什么注意事项?2021-04-21 1438

-

PCB抄板软件Protel在PCB走线中的注意事项有哪些2021-04-26 2472

-

TDA8035器件所用引脚有哪些注意事项2022-01-17 1072

-

HDMI在TV应用中的注意事项2008-10-22 2833

-

SD卡与MMC卡的选购注意事项2009-12-19 994

-

RTL8370-GR和RTL8370M-GR布局走线注意事项pdf下载2018-03-09 3668

-

ups电池柜安装规范及注意事项2019-11-14 13236

-

EMI走线注意事项合集2021-12-20 2160

-

KEIL中使用C++注意事项2022-06-01 804

-

使用注意事项2023-07-07 925

-

DC电源模块的使用注意事项和安全规范2024-04-03 1662

-

CS SD NAND 在AI领域的应用和注意事项2025-08-15 903

-

BNC转接头接线注意事项2025-12-19 603

全部0条评论

快来发表一下你的评论吧 !