Chiplet,汽车“芯”风向

描述

导语:英特尔公司正式宣布,将推出一系列AI增强的汽车芯片,首家量产搭载车企将是来自中国的极氪。

异构集成、高速互联、算力灵活可扩展正在成为新一轮汽车芯片竞争的焦点。尤其是随着以ChatGPT为代表的大数据、大模型产品在车端的落地,对于芯片的要求还在持续提升。

本周,12家日本汽车制造商(包括丰田、日产、本田等)、零部件制造商和半导体公司组成了先进汽车芯片研发联盟,重点是利用Chiplet(小芯片)技术开发下一代汽车SoC。

根据该联盟的介绍,Chiplet技术的优势包括效率高、适应多种功能、提高生产过程中的良率、能够及时满足汽车制造商的性能和功能要求。

而在上周结束的2024CES展上,英特尔公司正式宣布,将推出一系列AI增强的汽车芯片,首家量产搭载车企将是来自中国的极氪。

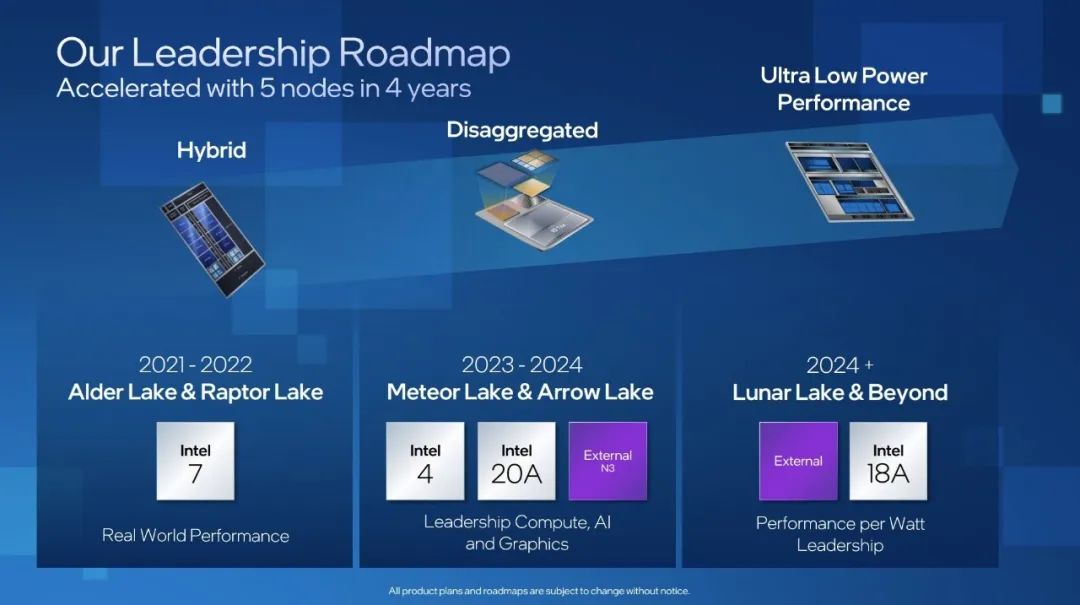

这款芯片的特点就是CPU+NPU+GPU的异构架构作为算力基座,并支持将第三方小芯片集成到SoC。为此,英特尔还宣布将于imec合作,以确保Chiplet封装技术满足车规级的严格质量和可靠性要求。

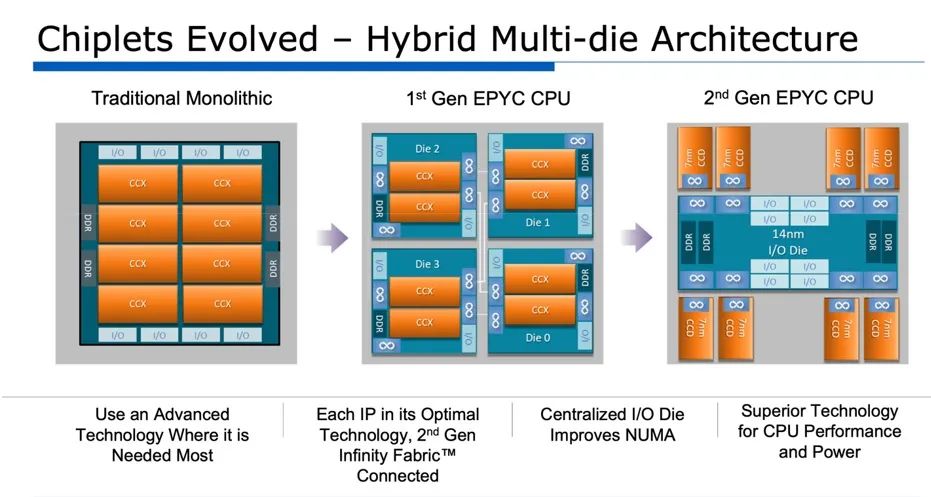

众所周知,芯片不同的制程工艺在一定程度上决定了硬件性能的上限。比如,与10nm工艺相比,7nm工艺性能提升20%,能效提升40%,晶体管密度提升到1.6倍,实现性能与能效的双重提升。

然而,随着先进制程逐步迭代到5nm、3nm甚至是2nm,摩尔定律(单位平方英寸上晶体管的数量,每隔18~24个月就将翻一番)逐渐趋缓,先进制程的开发成本及难度提升。

半导体行业的共识是,先进制程的流片费用越来越高昂,流片成功率也变得越来越低;同时,芯片良品率也开始大幅下降。

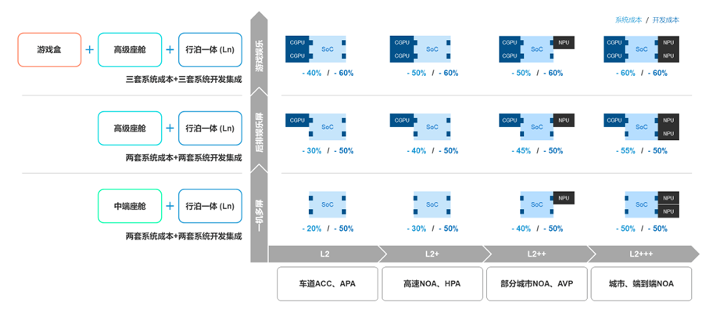

与此同时,头部车企对于芯片的要求,正在出现差异化。由于各家车型的定位不同,导致目前市面上的通用芯片难以满足个性化的需求。

此前,地平线宣布开放BPU IP授权,支持车企实现SoC自研,也是在这一趋势下的产物。“地平线不可能做出一款芯片能够适配任何场景,也不可能设计一堆的芯片去覆盖所有场景。”

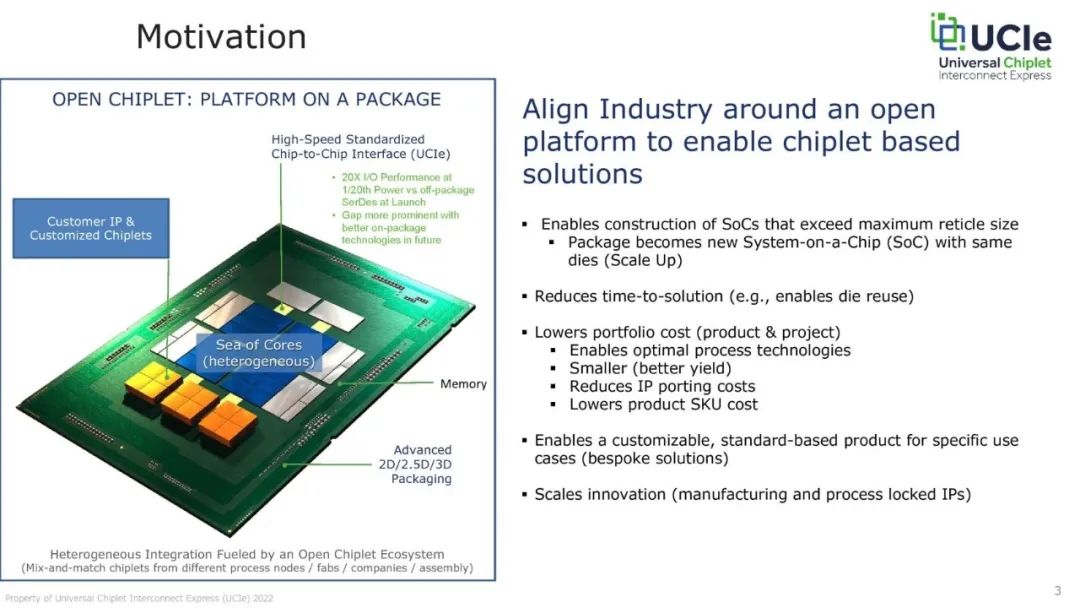

“基于Chiplet技术,客户可以灵活配置第三方IP(基于不同工艺)。”尤其是汽车智能化的需求不断释放,未来异构集成(比如,X86、Arm和RISC-V同时并存)的模式,或许会成为市场主流。

而一组数据显示,在Chiplet的系统级架构设计下,通过2.5D/3D堆叠等先进封装技术,使用10nm工艺制造出来的芯片可以达到7nm芯片的集成度,同时研发投入和一次性生产投入则比7nm芯片的投入要少的多。

此外,模块化的芯粒可以减少重复设计和验证环节,降低芯片的设计复杂度和研发成本,加快产品的迭代速度。同时,降低对先进工艺制程的依赖,对于车载应用市场来说,本身也是一种降本策略。

有意思的是,戈登·摩尔(Gordon Moore)在1965年发表的白皮书《集成电路塞满更多组件》中预言了这一天的到来,“随着芯片密度和复杂性的提高,最终用较小的功能构建大型系统可能会更经济,这些功能被单独封装并相互连接。”

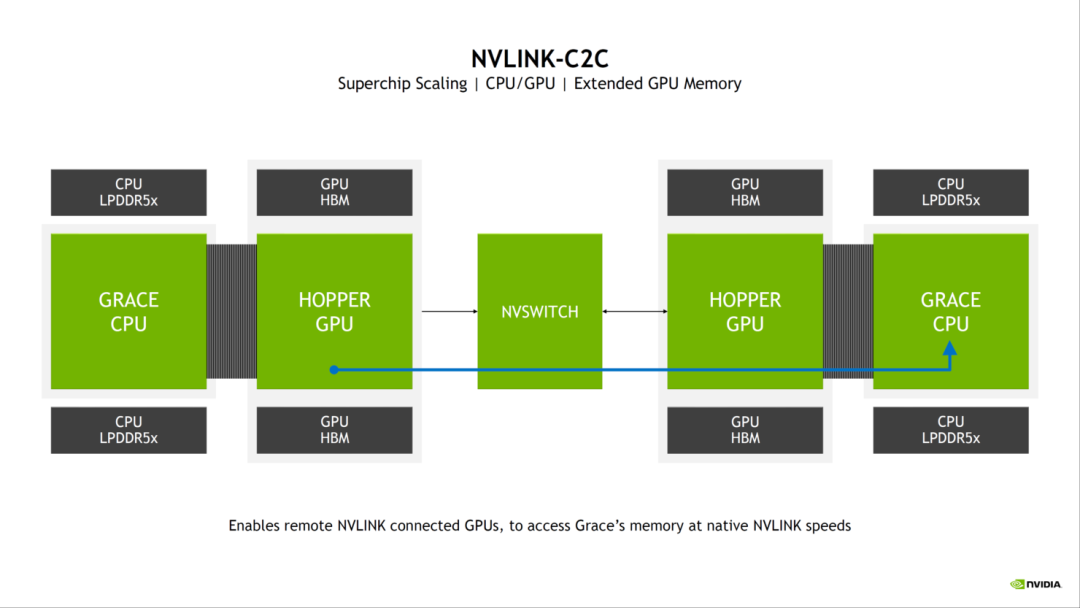

“为应对摩尔定律发展趋缓的局面,必须开发小芯片和异构计算。“站在英伟达的角度,这家已经在自动驾驶赛道占据先发优势的芯片巨头,同样觊觎市场规模巨大的跨域市场。

目前,英伟达的NVIDIA NVLink-C2C,也是一种超高速的芯片到芯片、裸片到裸片的互连技术,支持定制裸片与NVIDIA GPU、CPU、DPU、NIC和SOC之间实现一致的互连。

此前,该公司推出的DRIVE Thor(单颗芯片算力达到2000TFLOPS),就可以通过多颗芯片的NVLink-C2C互连来支持多域计算,以分离自动驾驶等关键安全功能和信息娱乐等功能的处理。

此外,去年,英伟达与联发科宣布,双方将共同为新一代智能汽车提供解决方案,合作的首款芯片锁定智能座舱,预计2025年问世,并在2026年至2027年投入量产。

在这款芯片设计上,联发科将开发集成英伟达GPU芯粒的SoC,搭载NVIDIA AI和图形计算IP,同样基于chiplet实现主芯片与GPU芯粒间高速互连。

引用行业人士的话来说,就是,“基于Chiplet技术的芯片架构,能最大化满足客户的定制化SoC需求,并为系统架构师提供了更高的设计自由度,为系列产品提供多种平台变体。”

而作为全球首家利用Chiplet技术研发车载算力芯片的企业,芯砺智能于2021年正式成立。针对车载芯片的特殊应用需求,芯砺智能开创了独家车规级Chiplet Die-to-Die互连技术。

本周,该公司对外宣布,全自研Chiplet Die-to-Die互连IP(以下称CL-Link)芯片一次性流片成功并顺利点亮;此前,该技术已经获得全球首个车规级ISO 26262 ASIL-D Ready认证。

CL-Link通过一种用于片间互连的总线流水线结构,做到了以较小位宽来实现片间高带宽及低延迟的互连,每条信号速率高达16Gbps,其总线到总线的延时小于5ns,和片内总线延迟在同一量级。

同时,与目前市面上主流的Chiplet技术主要依靠先进封装(对成本、可靠性、功能安全及供应链安全等挑战较大)不同,基于传统封装的CL-Link技术可以实现更高良率及更低成本。

这意味着,中国企业首次在车规级赛道实现Chiplet技术的创新突围,也在一定程度上可以帮助更多的中国芯片企业实现“合纵连横”。更关键的是,这项技术可利用相对成熟的半导体制造和封装技术,突破对先进工艺的依赖。

比如,Chiplet允许使用不同的制程制造异构SoC,例如,高性能模块采用7nm,其他模块只需要14nm或28nm就可以做到性能最大化,使系统整体的功能密度非常接近于7nm的集成。

在芯砺智能看来,在后摩尔时代,Chiplet技术是大算力平台芯片目前最具前景和可实现性的突破性技术路径,并且可以应对未来智能汽车E/E架构走向跨域融合、中央计算平台的趋势。

“单一域控制器内部的标准计算能力,将无法处理未来ADAS、通信和娱乐功能带来的工作负载,尤其是不断的OTA带来的挑战。”在imec公司看来,Chiplet带来的最大效应就是降本增效。

比如,小芯片的开发成本,大概是大芯片的60%;尤其是软件定义汽车概念的逐步落地,不同的算法对于SoC的不同IP核,有着不同的要求。这意味着,为特定任务部署高性能计算,有了更灵活的方式。

同时,随着汽车行业的竞争日益白热化,新车上市周期的大幅度缩短,这意味着,车企需要更加灵活的算力平台,甚至是硬件可插拔的升级方案。

“Chiplet概念带来的另一大革新,就是硬件升级可以做到类似搭乐高积木一样的简单。”在行业人士看来,这是对汽车芯片未来格局的洗牌和整合信号。

而就在两年前,Intel、AMD、ARM、台积电等行业巨头一起发布了新的芯片级别互联标准UCIe,希望解决chiplet行业标准问题。这些企业的大部分,掌控者汽车芯片产业链的核心环节。

这些传统巨头的目标是,创建一个开放的生态系统,使不同厂商在不同工艺技术上设计和制造的芯片与先进的封装技术集成在一起可以实现有效协同。但背后的实质,是继续垄断市场。

而按照芯砺智能的说法,未来车规级高算力可扩展(200-2000Tops)SoC定制化设计将不再是成本难题。“后摩尔时代异构集成,对于行业来说,将是一种普惠方案。”

-

IMEC组建汽车Chiplet联盟2024-10-15 1288

-

北极雄芯获云晖资本投资,加速Chiplet研发与产品化2024-06-13 1583

-

Chiplet成大芯片设计主流方式,开启IP复用新模式2024-01-12 3660

-

奎芯科技参展ICCAD2023,以Chiplet搭建“芯”未来2023-11-14 1507

-

芯和助力Chiplet落地2023-08-28 1508

-

Chiplet的验证需求有哪些变化?2023-07-26 1536

-

芯华章浅谈eda、Chiplet等新型技术趋势2023-05-25 648

-

芯原助力蓝洋智能部署基于Chiplet架构的芯片产品2023-03-30 1091

-

北极雄芯开发的首款基于Chiplet异构集成的智能处理芯片“启明930”2023-02-21 1483

-

芯动兼容UCIe标准的最新Chiplet技术解析2022-12-23 3195

-

芯动科技加入UCIe产业联盟 助力Chiplet标准化2022-08-16 2666

-

芯原股份将进一步推进Chiplet技术和产品的发展2022-04-02 2179

-

芯原股份:正积极推进对Chiplet的布局2021-01-08 3622

-

芯动科技积极推动中国Chiplet产业联盟2020-11-06 2487

全部0条评论

快来发表一下你的评论吧 !