运放VOS对BG输出电压影响

模拟技术

描述

运放VOS对BG输出电压影响:

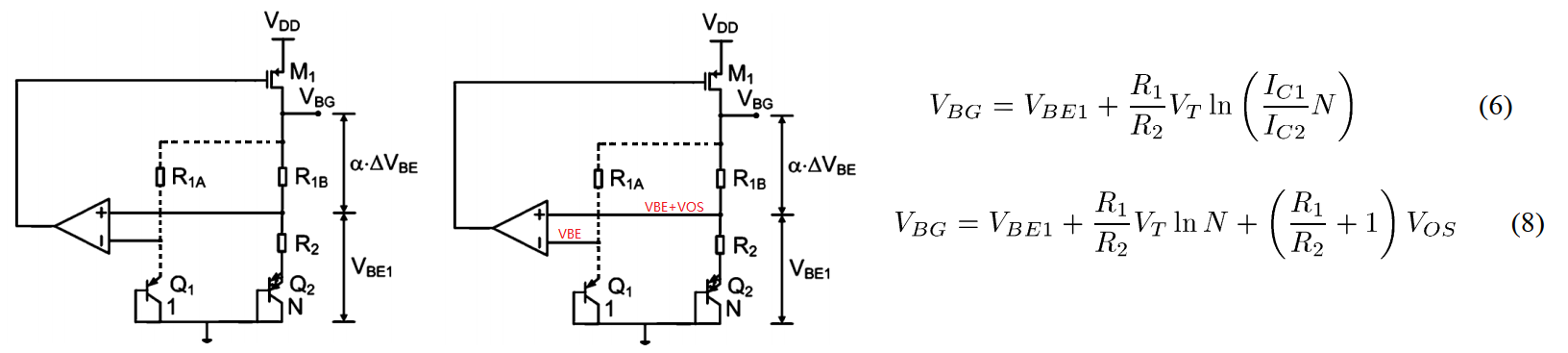

如上图左所示,VBG电压计算式由等式(6)给出

此时,考虑到运放存在总失调电压VOS,此时运放接入电路环路增益为:G_loop=(R1+R2+1/gmQ2)/(R2+1/gmQ2)≈(R1+R2)/R2 (1/gmQ2相对R1、R2比较小),假设运放增益足够大,使得输入两端能够有效钳位为VBEQ1,由负输入端为VBE,正输入叠加失调电压为VBE+VOS → 运放输入端的差值VOS,反映到输出VBG为VBG+VOS*G_loop,得到等式(8),很明显VOS被环路放大了,叠加到VBG上对基准电压产生了影响,所以需要消除该运放失调电压VOS的影响。

原始VBG表达式为:VBG0=VBE2+(R1+R2)*(VBE1-VBE2)/R2,引入+VOS后,R2上端变为VBE1+VOS,则VBG = VBE2+(R1+R2)*(VBE1+VOS-VBE2)/R2 = VBG0+(R1+R2)/R2*VOS

如果使用VBE1这个变量进行等式(8)推导:

引入+VOS后,R2上端为VBE1+VOS,则VBG = VBE1+VOS+R1*(VBE1+VOS-VBE2)/R2 = VBE1+R1/R2*(VBE1-VBE2)+(1+R1/R2)*VOS = VBG0+(R1+R2)/R2*VOS

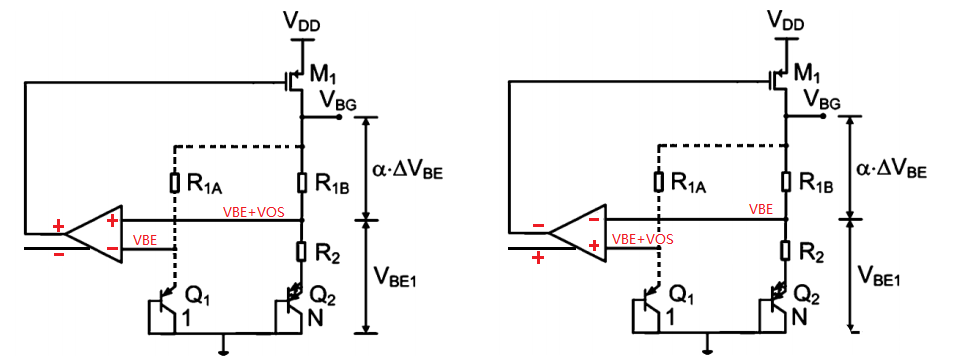

运放失调电压的消除--chopper原理:

运放的失调电压最主要贡献体现在输入对管的mismatch上(其余部分也会存在适配,后续分析)

Chopper的原理在于,周期性的将运放的输入端交换,同时为了保证运放的正负反馈不发生改变,输出端也会相应交换,如下图所示:

前半个chopper周期,运放将﹢VOS叠加到输出VBG,后半个chopper周期运放将-VOS叠加到输出VBG,则在一个choppe周期中,±VOS对VBG的影响被消除。

输入端和输出端需要同时交换,保证运放在环路中的反馈极性不发生变化。

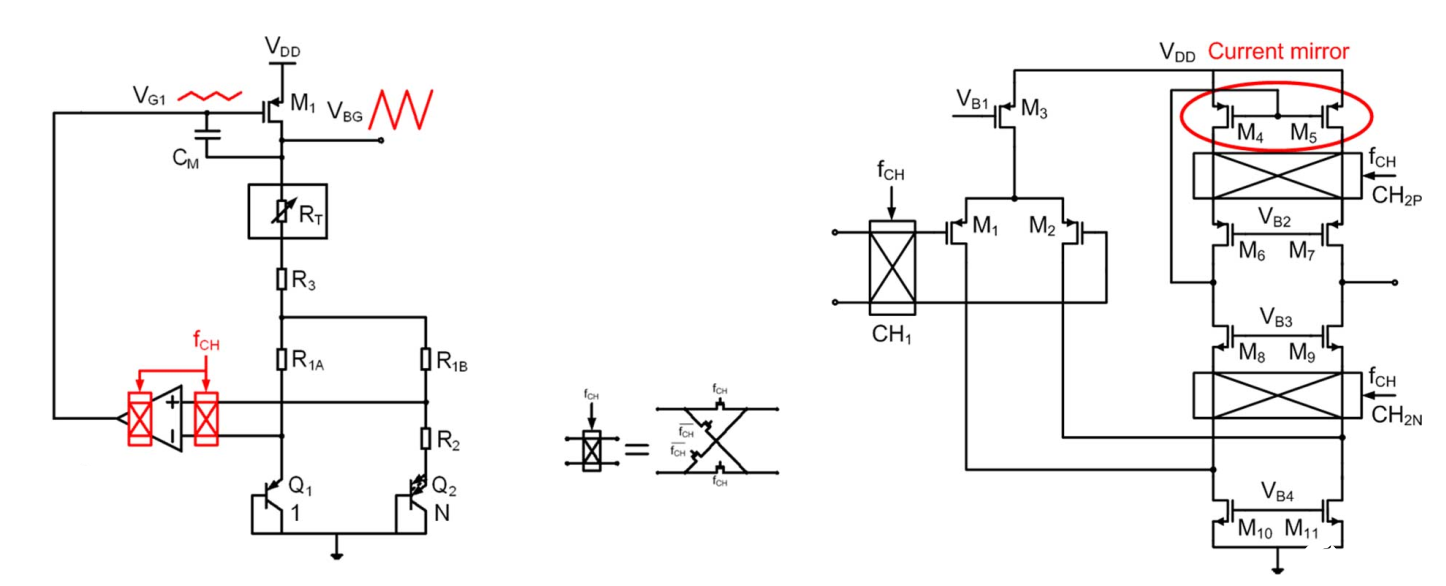

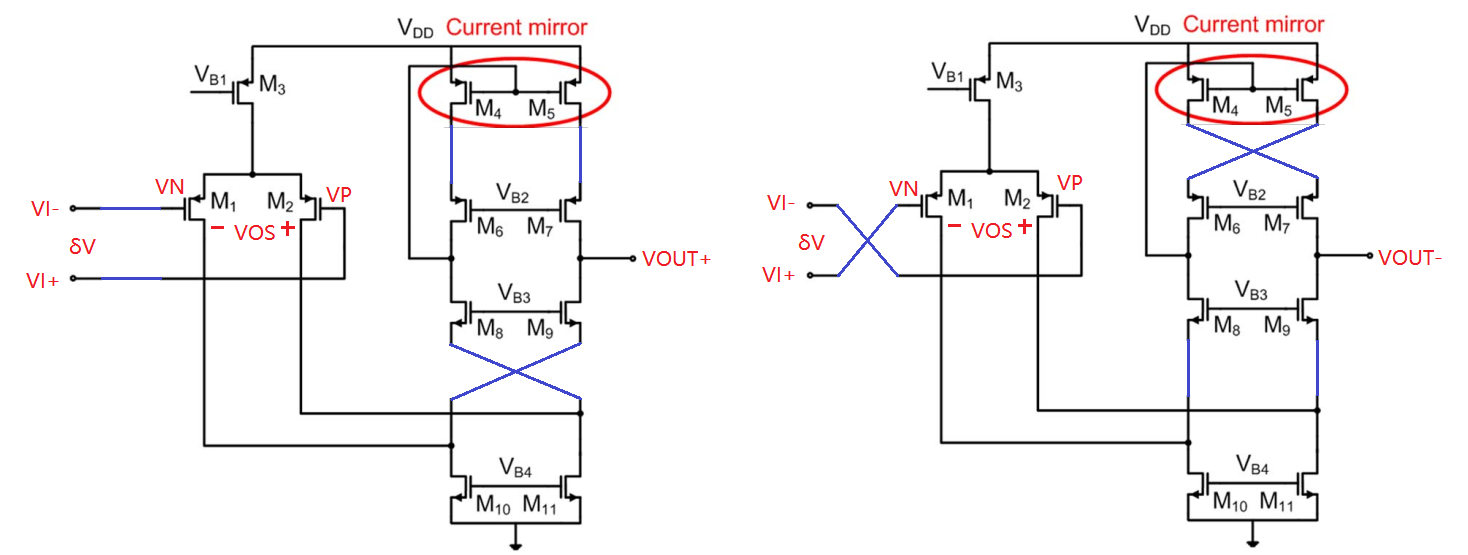

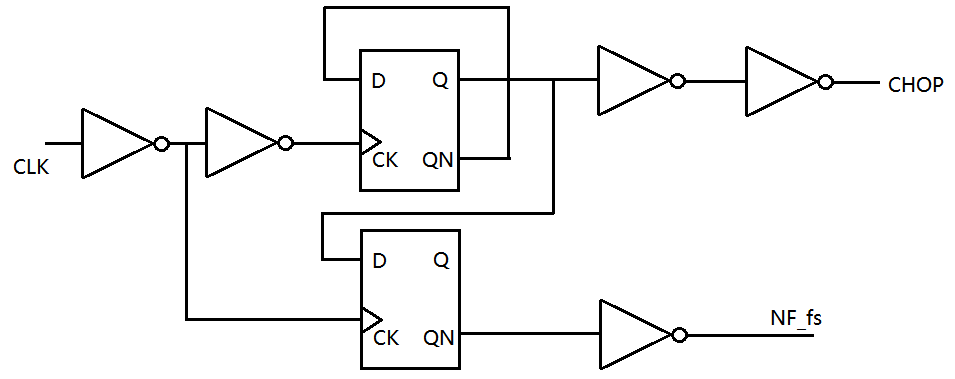

折叠运放电路的chopper分析:

使用chopper时钟,将运放输出周期性反接,如上图右边电路所示,注意CH1和CH2N是反向时钟,得到下图:

假设M1/M2贡献mismatch体现为VP-VN=+VOS,运放开环增益为A:

左图:VI+接VP,VI-接VN,且VI+ - VI-=δV → 输出VOUT+ = A*(δV+VOS)

右图:VI+接VN,VI-接VP,且VI+ - VI-=δV → 输出VOUT- = A*(δV-VOS)

则一周期内两次平均输出(VOUT+ + VOUT-)/2 = A*δV ,则运放的VOS在一个满周期上被抵消

同理,M10/M11之间的mismatch也能被消除,在此不做额外推导

M6/M7/M8/M9之间的mismatch影响相对没有输入管M1/M2、尾电流M10/M11大,不作考虑,保证版图的匹配性良好即可

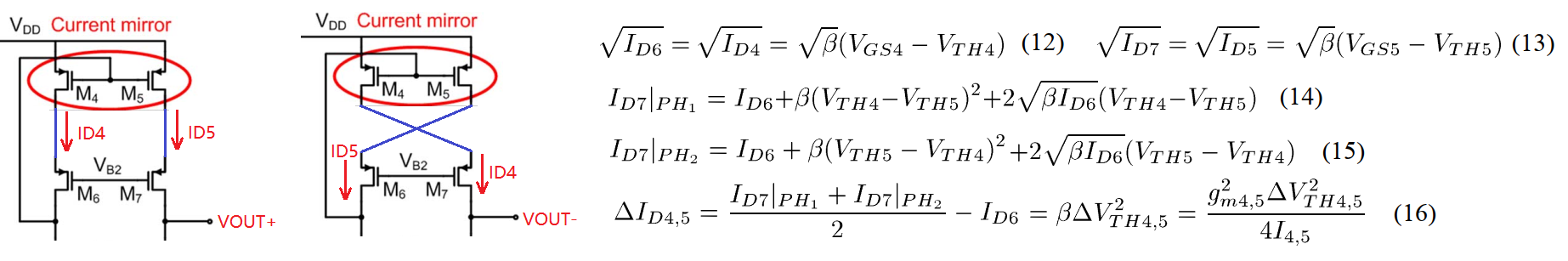

M4/M5之间的mismatch无法完全消除:

前半周期ID7=ID5, ID6=ID4, 得到等式(14);后半周期ID7=ID4, ID6=ID5, 得到等式(15)

等式(14)(15)均已ID6为基准变量,去除了VGS这个变量(如果M4/M5之间存在VTH上的差异,前后半周期得到的VGS是不一样的,会使得计算值很复杂,初次推导时,我认为前后两次VGS相等,得到的结果直接抵消掉了,认为M4/M5的mismatch是能够消除的)

通过等式(14)(15)结合,消掉ID6变量得到前后半周期下的两条支路的电流变化量,可以看到(VTH4-VTH5)的一阶项是能够被chopper消除的,剩下了chopper无法消除的二阶项β*(VTH4-VTH5)^2

该变化电流等效到输入对管,则需要的输入变化量为:

假设mismatch引起的M4/M5之间的阈值电压差值为3mV,则等效到运放输入端的VOS量级为uV,保证M4/M5之间的版图匹配,能有效的减小该值。

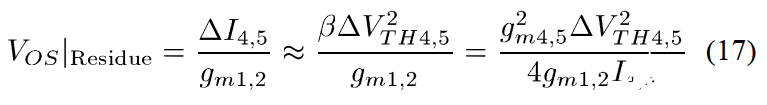

Chopper之后的滤波:

运放加入chopper之后在运放输出端加入噪声抖动,该抖动需要通过添加notch filter滤波消除

简单的SC notch filter电路由T型结构的开关电容组成,当fs为高时,CS1采样VI电压,CS2保持输出VG1;当fs为低时,CS2采样V1电压,CS1保持输出VG1

开关与电容组成RC低通滤波器,可以滤除V1上的高频噪声,同时为了保证采样的准确性,fs的时钟需要与运放的chopper时钟错位1/4个周期

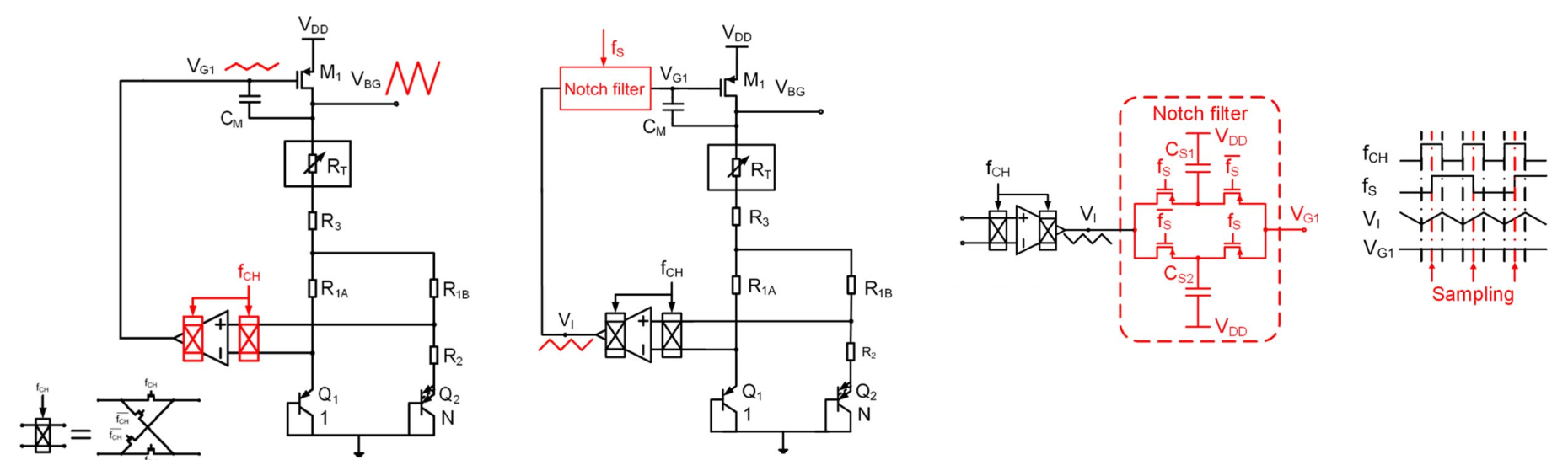

可行的时钟电路实现电路如下:

CLK送进D触发器进行二分频得到CHOP时钟,同时CLK取反,采样CHOP时钟,则得到Notch-Fliter时钟fs,实现两个时钟之间1/4周期的相位差。

审核编辑:黄飞

-

运放输入失调电压的结构和原理2024-08-23 2550

-

求助,帮忙看下以下测量运放的输入失调电压Vos正确否?2024-08-14 418

-

失调电压Vos定义 各类运放失调电压范围 失调电压产生原因2023-11-06 4468

-

什么是输入失调电压Vos?Vos对电源的影响?2023-10-29 2681

-

运放参数解析:输入失调电压(Vos)2023-10-01 13836

-

详解运放的失调电压Vos2023-09-28 3785

-

失调电压Vos的理解和仿真实验2023-08-15 3256

-

运放输入失调电压(Vos)和温漂(ΔVos/ΔT)2023-06-06 3372

-

运放输出电压上升时间的计算指南2023-04-27 1601

-

运放的失调电压Vos的理解与仿真验证2023-02-01 6862

-

输入失调电压Vos及温漂2019-07-04 8400

-

运放失调电压自动补偿设计与实现2017-11-29 18150

-

运放的失调电压是什么?2009-04-22 9191

全部0条评论

快来发表一下你的评论吧 !