半减器和全减器的真值表与门电路图设计

描述

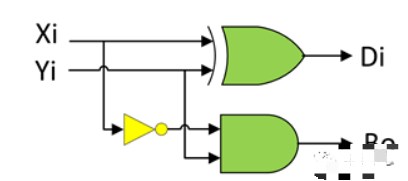

半减器

半减器具有两个输入端(减数与被减数)及两个输出端(差数及借位数)的逻辑电路。

半减器用于计算两比特Xi和Yi的减法,输出结果Di和向高位的借位Bo(Borrow output)。

真值表

门电路图

全减器

全减器是两个二进制的数进行减法运算时使用的一种运算单元,最简单的全减器是采用本位结果和借位来显示,二进制中是借一当二,所以可以使用两个输出变量的高低电平变化来实现减法运算。

同时,全减器可以采用74LS138三线—八线译码器实现。

真值表

全减器真值表如下:其中Ai表示被减数,Bi表示减数,Di表示本位最终运算结果,Ci表示低位是否向本位借位,Ci+1表示本位是否向高位借位。

门电路图

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

LUT与真值表有何关系2021-11-02 3707

-

与门电路、或门电路、非门电路及实例2021-07-05 12952

-

门电路的计算方式 门电路工作原理真值计算2019-12-25 5620

-

逻辑门电路符号图及与门真值表的资料概述2019-08-31 41505

-

与门真值表和与非门真值表的区别2018-01-30 124214

-

求常用单片机的功能表、引脚图、真值表2013-04-25 3307

-

与门电路图2011-07-12 6681

-

晶闸管与门电路电路图2009-06-06 1441

-

光耦合器构成的与门电路图2009-06-04 986

-

二极管与门电路图2009-05-08 2932

-

与门电路符号图2009-04-07 24221

-

高扇入与门电路图2009-04-02 704

全部0条评论

快来发表一下你的评论吧 !