求一种减法器的设计方案

电子说

描述

半减器

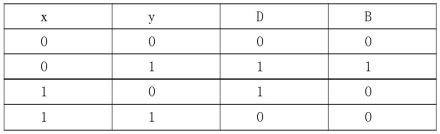

半减器(Half Subtractor,HS),二输入、二输出变量函数模块。一个半减器模块有两个输入 x、y 和两个输出 D、B,其中 x 称为被减数,y称为减数; D 称为差,B 称为借位输出信号。半减器是只有两个输入变量、两个输出变量,无借位输入的一位减法器, 半减器的真值表如图3所示。

图3 半减器真值表

由半减器的真值表可推导出半减器的逻辑表达式为:

D=x⊕y (“⊕”表示异或运算)

B=-x·y (“-”表示非运算,“·”表示与运算)

半减器的门级逻辑电路

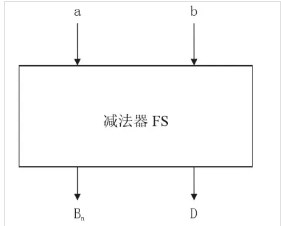

图4 半减器的符号

由半减器模块的逻辑表达式我们可以得到最常用的半减器模块门级的逻辑电路图和半减器模块的符号,如图4所示。

全减器

一个全减器模块有三个输入 a i 、bi和 B i ,两个输出 D i 、B i+1 ,其中 ai称为被减数,bi称为减数,Di称为差,Bi称为第 i 位的借位输入信号,Bi+1称为第 i 位的借位输出信号。

全减器是包含低位借位的三个输入变量、两个输出变量的一位减法器,在半减器的基础上再加一个低位借位输入位,全减器的真值表如图5所示。

图5

由全减器的真值表推导出全减器的逻辑表达式为:

Di**=a i ⊕b i ⊕B**i

Bi+1**=(a i ⊕b i )·b i +(a i ⊕b i )·B**i

图6 全减器的门级逻辑电路

图7 全减器的符号

由全减器的逻辑表达式可以得到全减器模块门级的逻辑电路图和全减器模块的符号,分别如图6、图7所示 。

对于 n 位的二进制数,将两个 n 位的二进制数相减得到一个 n 位的二进制的差以及一个 1 位的借位输出信号,这个借位输出信号可以作为它下一位的借位输入信号,或者作为一个溢出标志,图8为一个 n 位减法器电路的一般表示符号(其中 a、b 和 D 是 n 位的二进制数,Bn是 1 位的二进制数) 。

图8 n位减法器

-

高速低功耗的利器:MC10H180双2位加法器/减法器2026-04-11 233

-

减法器电路与原理 减法器电路图分享2024-02-19 12795

-

FPGA常用运算模块-加减法器和乘法器2023-05-22 7508

-

基于OP07的减法器设计2023-05-15 941

-

数字电路中加法器和减法器逻辑图分析2020-09-01 24987

-

如何用最简单的方法设计一个减法器?2020-04-27 3448

-

减法器电路设计方案汇总(五款模拟电路设计原理图详解)2018-01-17 95817

-

设计一个基于RS触发器余3码十进制减法器2017-11-28 3400

-

哪一个是减法器?负反馈在减法器电路中的原理?2017-08-31 6354

-

减法器设计异常2017-02-14 5996

-

8位加法器和减法器设计实习报告2013-09-04 2738

-

带输入缓冲的减法器电路2010-09-04 3265

-

减法器电路2010-04-24 10209

-

本的二进制加法/减法器,本的二进制加法/减法器原理2010-04-13 5523

全部0条评论

快来发表一下你的评论吧 !