具有低导通电阻的GaN-on-SiC肖特基势垒二极管设计

描述

北京工业大学和中国北京大学报道了碳化硅衬底(GaN/SiC)上由氮化镓制成的全垂直结构肖特基势垒二极管(SBD)的性能,通过使用超薄的氮化镓铝(AlGaN)缓冲层而不是更常见的复杂、厚的AlN/AlGaN结构[Yuting Sun et al, Semicond. Sci. Technol.,2024年1月24日在线发布]。该团队评论说:“这种外延策略也可以通过在单个平台上结合GaN和SiC的优点来用于SiC / GaN异构集成。”

研究人员进一步实施了其它增强功能,例如在高温退火过程中使用帽层来防止材料分解,以及用于边缘端接的氟离子注入。垂直氮化镓电子结构增强了处理高功率和高电压的能力,因为峰值电场通常发生在远离表面的地方,从而增强了抗击穿的鲁棒性,这与横向器件不同。性能最佳的垂直器件是在独立式或块状氮化镓衬底上生产的,但这些衬托往往体积小且成本高昂。

碳化硅衬底制造的最新发展使Wolfspeed和Tankeblue的8英寸直径晶圆商业化,用于大规模生产,提高了SiC和GaN/SiC器件成本降低的前景。碳化硅作为氮化镓电力电子器件基础的另一个优势是碳化硅的高导热性,能够更好地对焦耳热效应进行热管理。

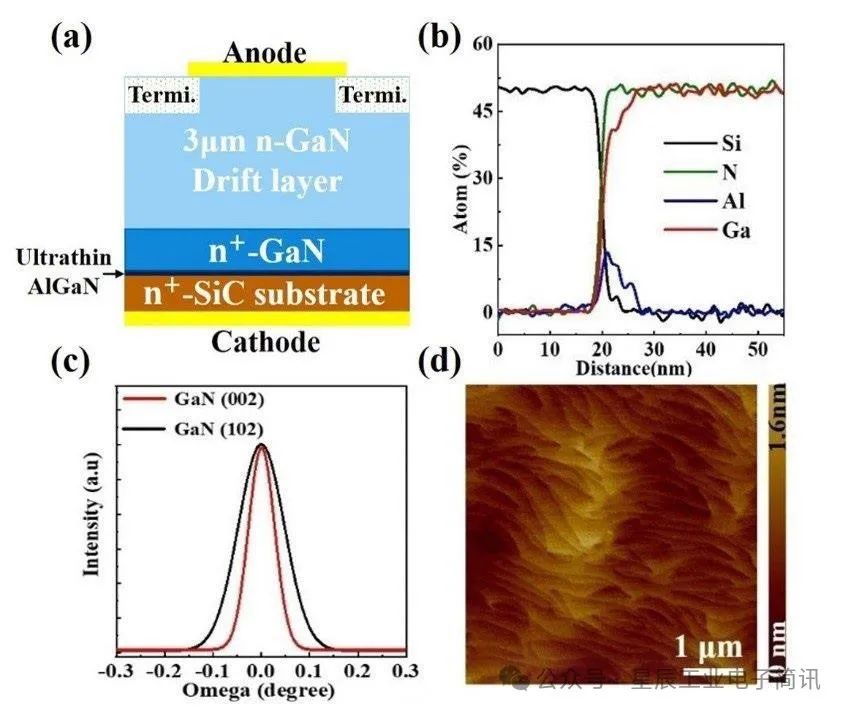

垂直SBD的III-氮化物层(图1)使用金属有机化学气相沉积(MOCVD)在n-SiC衬底上生长。在700nm n-GaN缓冲层的MOCVD之前,用三甲基铝对基板进行预处理。

图1:(a)全垂直结构GaN-on-SiC SBD的横截面示意图。(b)在GaN/SiC界面获得的EELS曲线。(c)对称(002)和不对称(102)X射线衍射摇摆曲线和(d)用超薄AlGaN缓冲层生长的GaN的AFM图像(5 μmx5 μm)。

预处理通过氮化镓/碳化硅界面的原子间自扩散形成超薄层AlGaN。根据电子能量损失谱(EELS)测量AlGaN层的厚度为2nm。III-氮化物外延用3 μm N完成−-氮化镓漂移层。根据原子显微镜(AFM),均方根粗糙度为0.22nm。

研究人员评论说:“合理的晶体质量和表面粗糙度证明了超薄AlGaN缓冲层在适应GaN和SiC之间的不匹配方面的有效性。”

欧姆阴极触点由退火镍组成。研究人员使用了二氧化硅(SiO2)封盖层,可在900C快速热退火(RTA)过程中保持材料质量。通过氢氟酸浸渍除去盖子。没有帽层,AFM表面粗糙度显著增加,GaN原子表面台阶完全消失。相比之下,封盖器件材料的AFM粗糙度仅略有增加。无盖退火的表面分解导致肖特基金属/半导体接触质量降低,从而降低电流-电压行为。

研究人员报告说:“尽管退火后表面粗糙度从0.22nm增加到0.28nm,表面凹坑更多,但在改进的SBD的GaN表面上仍然清晰可见有序排列的原子步骤。这些结果表明,SiO2加盖层可以有效保护GaN表面在RTA过程中不被分解。”

该器件通过氟离子注入用于边缘端接,并沉积镍/金用于肖特基阳极接触。使用超薄AlGaN层可降低比导通电阻(R开,SP) 的SBD为1.5m-cm2,而具有50nm厚重掺杂Al0.25Ga0.75N缓冲层的参考SBD为50m-cm2。研究人员将超薄AlGaN层SBD的更好性能归因于隧道电流的增加,而厚AlGaN缓冲层的带偏移量要大得多,从而削弱了隧穿能力。

在器件性能方面,RTA期间的封顶将导通电阻降低了近2倍。肖特基势垒高度为0.79eV(带封顶)和1.02eV(不带封顶)。此外,RTA 期间的上限将理想因子从1.22降低到 1.08(理想因子=1)。此外,相应的开/关电流比为8.5x106和 5x109,改进了近三个数量级(28dB)。

RTA期间加帽的改进SBD的导通电阻为0.85m -cm2,该团队将其描述为“在通过复杂制造工艺制造的异质衬底上的垂直氮化镓二极管中相对较小的价值”。

3V偏置时的正向电流密度达到1.8kA/cm2。该团队评论说:“正向I-V特性的优越性表明,超薄AlGaN缓冲层在SiC衬底上实现了基于简化外延堆栈的低RON,sp和稳定电导率的全垂直GaN SBD。”

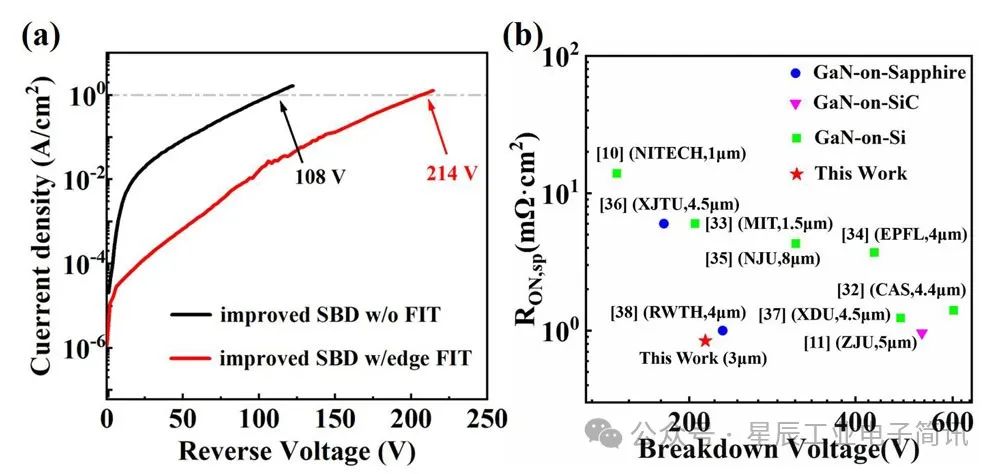

在25-120°C范围内增加器件温度的效果发现Ron的缓慢斜坡上升,SP的0.00345m-cm2/C。导通电压同时受到0.0016V/C缓慢下降速率的影响。研究人员发现,氟离子端接(FIT)的效果是反向击穿电压(BV,1A/cm2)从108V增加到214V(图2)。

图2:(a)无FIT和边缘FIT的改进SBD的反向电流-电压特性。(b)RON,sp 与BV在异质衬底上完全垂直或准垂直GaN SBD的基准。

研究人员报告说:“对于具有相同漂移层的器件(在掺杂浓度为1.5x1017/cm3时厚度为3μm)的器件,理论BV为221V)。测得的BV略低,为214V,表明漂移层的晶体质量良好,并且该工作的边缘端接有效。

与异质(即非GaN)衬底上SBD的其它报道相比,其低电阻表明“外延堆栈具有良好的导电性”。该团队补充说:“通过降低n型掺杂浓度可以实现更高的BV。”。其它报告中的漂移层的掺杂浓度通常低十倍。

转载: 星辰工业电子简讯

审核编辑:刘清

-

肖特基势垒二极管的作用 肖特基势垒二极管的工作原理2023-09-02 4707

-

SiC产品和Si产品的两点比较 SiC肖特基势垒二极管的特征2023-07-18 1398

-

碳化硅SiC MOSFET:低导通电阻和高可靠性的肖特基势垒二极管2023-04-11 2250

-

低VF MEGA 肖特基势垒二极管-PMEG2005EB2023-02-20 487

-

SiC肖特基势垒二极管和Si肖特基势垒二极管的比较2023-02-08 1583

-

东芝开发带嵌入式肖特基势垒二极管的低导通电阻高可靠性SiC MOSFET2022-12-12 2010

-

肖特基势垒二极管电路设计2021-01-19 4161

-

肖特基势垒二极管的特点2019-04-30 3402

-

浅析肖特基势垒二极管2019-04-11 1867

-

罗姆肖特基势垒二极管的特点2019-03-21 1938

-

肖特基势垒二极管的特征2018-12-03 2140

-

什么是肖特基势垒二极管2010-03-05 2630

-

肖特基势垒二极管,肖特基势垒二极管原理/结构2010-02-26 4071

全部0条评论

快来发表一下你的评论吧 !