四位二进制减法器的设计与实现

描述

总体方案设计

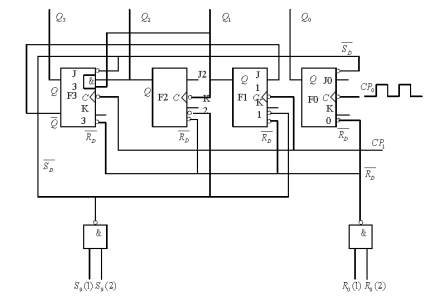

本设计使用EWB进行仿真,使用74LS48、七段译码器、LED、开关、异或门、或门、非门、与非门等。电路按功能分为三个部分:减数部分:减数变成补码(原码取反加1);被减数部分:被减数与减数的补码相加;差部分:被减数减减数的结果显示。四位二进制减法器的总体仿真图如图所示。

图9 四位二进制减法器的总体仿真图

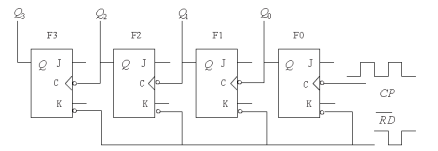

被减数模块的设计

本模块由开关、74LS48、VCC(+12 V)、GND、七段译码器构成,用开关控制输入信号( 被减数),5、6、7、8 从高位到低位,用74LS48和七段译码器构成显示电路。四位二进制减法器的被减数模块的仿真图如图10所示。

图10 四位二进制减法器的被减数模块的仿真图

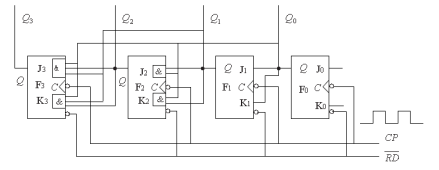

减数模块的设计

本模块由开关、74LS48、VCC(+12 V)、GND、七段译码器、异或门、或门、非门、与非门构成。用开关控制输入信号(减数),1、2、3、4 从高位到低位,将输入信号的原码变成补码供计算使用,用74LS48 和七段译码器构成显示电路。四位二进制减法器的减数模块的仿真图如图11所示。

图11 四位二进制减法器的减数模块的仿真图

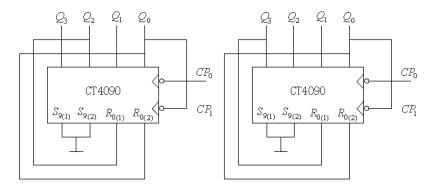

差模块的设计

本模块由VCC(+12 V)、GND、七段译码器、74LS48、LED 构成。从右到左依次是从高位到低位,并用74LS48和七段译码器构成显示电路。四位二进制减法器的差模块的仿真图如图12所示。

图12 四位二进制减法器的差模块的仿真图

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

深入剖析 DM74LS283:4 位快速进位二进制加法器2026-04-10 231

-

减法器电路与原理 减法器电路图分享2024-02-19 12795

-

如何去实现一个2位二进制乘法器的设计呢2021-11-03 4261

-

## 线上实验五:2个2位二进制乘法器 精选资料分享2021-07-30 2121

-

集成四位二进制计数器2021-07-29 5568

-

数字电路中加法器和减法器逻辑图分析2020-09-01 24987

-

DM74LS83A四位快速进位二进制加法器的数据手册免费下载2020-05-26 2512

-

如何理解二进制运算规则 二进制是如何运算的2019-12-11 8538

-

二位BCD码减法器2019-09-18 6050

-

二进制加法器电路框图2019-06-22 28971

-

4位二进制乘法器电路2018-10-09 7361

-

8位加法器和减法器设计实习报告2013-09-04 2738

-

本的二进制加法/减法器,本的二进制加法/减法器原理2010-04-13 5523

-

采用减法计数简化二~十进制一二进制码变换2009-04-10 830

全部0条评论

快来发表一下你的评论吧 !