串行进位减法器电路设计

描述

数字减法器电路的基本原理

对于两个二进制数 x 和 y,用“x-y”表示他们的二进制差,其结果有如下四种情形:

(1)0-0=0;(2)1-0=1;(3)1-1=0;(4)10-1=1。

对于上述四种情形中的 “10-1=1”的特殊情形,也即是当 x=10(即十进制的 2),y=1 时,它们的二进制差为 1,这表明在二进制减法中,作差过程存在向前一位借位的情形。

串行进位减法器电路

一个 n 位串行进位减法器是由 n 个全减器的借位位首尾相连、依次串联在一起形成的,在串行进位减法器中,其借位从最低有效位( Least Significant Bit,LSB)传到其最高有效位(Most Significant Bit,MSB)需要很长的的时间(电路的延时)。

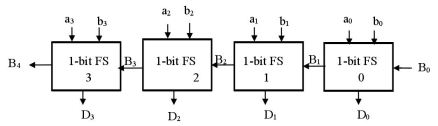

图1 四位串行进位减法器逻辑电路图

图2 四位串行进位减法器的符号

图1、图2分别是一个四位的串行进位减法器逻辑电路图和符号,其中 a i 、bi和 Bi是输入位,D i 、Bi+1是输出位,且 Bi+1作为更高位的输入位。

串行进位减法器电路的主要优点是:结构简单、便于连接和 IC 版图设计的实现;但其缺点是:执行运算速度较慢。这是因为串行进位减法器电路每一位的相减必须等到它前一位的计算结果,最高位相减必须要等到它前面的所有位都完成相减才能进行。

由于全减器只有在它的输入位有效时它的输出结果才是有效的,最左端的电路是最后响应的,这样全减器的输出结果才是正确的。

因此,串行进位减法器电路总的延时取决于每一个全减器电路的信号传输延时,而信号的传输延时又与逻辑门的工艺有关,所以串行进位减法器电路的时间延时和电路中逻辑门的工艺相关。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

高速低功耗的利器:MC10H180双2位加法器/减法器2026-04-11 233

-

减法器电路与原理 减法器电路图分享2024-02-19 12794

-

基于OP07的减法器设计2023-05-15 941

-

数字电路中加法器和减法器逻辑图分析2020-09-01 24987

-

减法器电路设计方案汇总(五款模拟电路设计原理图详解)2018-01-17 95817

-

哪一个是减法器?负反馈在减法器电路中的原理?2017-08-31 6354

-

减法器设计异常2017-02-14 5994

-

8位减法器求解?2013-10-08 13591

-

8位加法器和减法器设计实习报告2013-09-04 2738

-

带输入缓冲的减法器电路2010-09-04 3265

-

减法器电路2010-04-24 10209

-

本的二进制加法/减法器,本的二进制加法/减法器原理2010-04-13 5523

-

串行进位加法器2009-04-07 17473

全部0条评论

快来发表一下你的评论吧 !