自动化构建环境在FPGA设计中的应用

可编程逻辑

描述

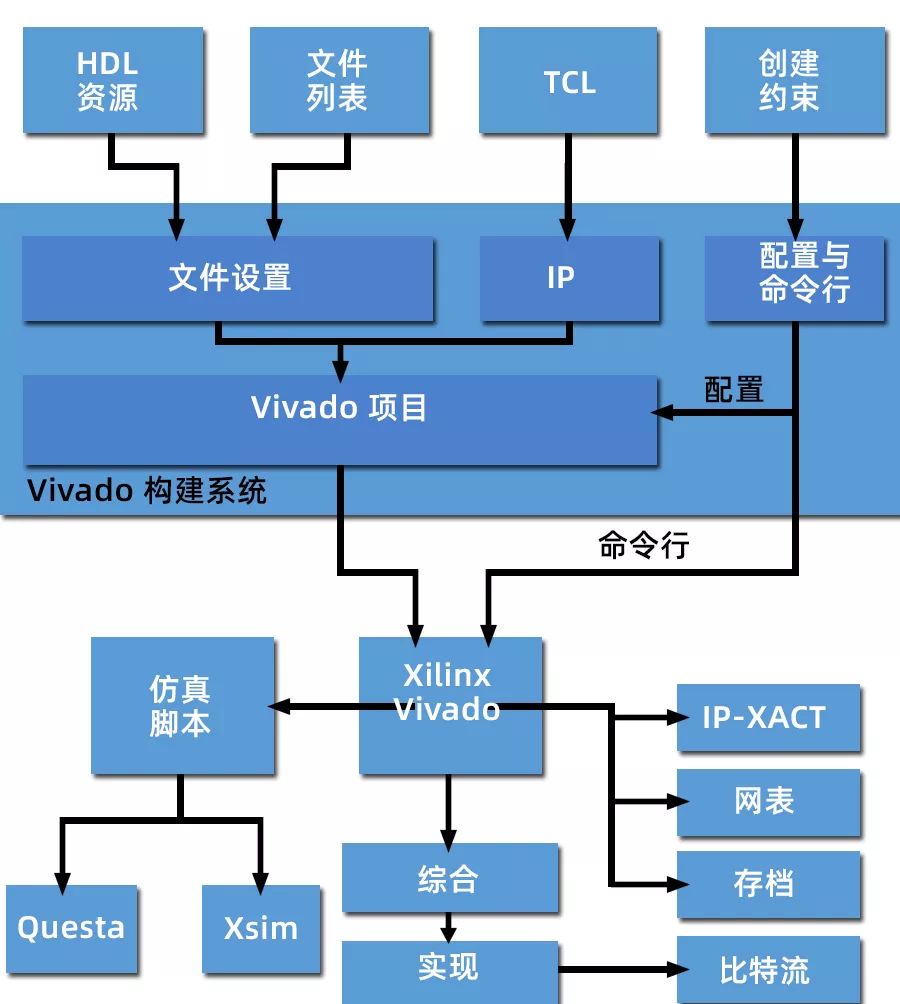

创建 FPGA 设计和维护 Vivado 设计套件项目时,版本控制系统对于团队合作可能是一项具有挑战性的任务。工程师必须能跟踪设计变更,完整地从 HDL 或 TCL 源代码再现项目并交付特定的项目状态。Vivado 工具非常适用于这类工作,因为该工具能够为项目生成存档文件或创建 TCL 文件,从而再现项目状态。

然而,上述机制需要一定数量的手动操作,而且在 Vivado 设计套件项目外对设计的参数进行设置,也存在不够灵活的问题。因此,为了简化上述操作,我们已经开发出对应脚本。其思路是在提供项目的 HDL 和 TCL 源文件的同时,提供从头创建 Vivado 设计套件项目所需的其他配置文件。设计构建脚本的目的是帮助用户在单独的 Vivado 设计套件项目下开发独立的项目组成部分(特色),且能够以其他配置方式对项目不同组成部分的源文件进行组合。此外,构建脚本也可用于创建目标构建工件,例如 IP XACTIPXACT 封装、仿真、综合、实现和比特流生成。

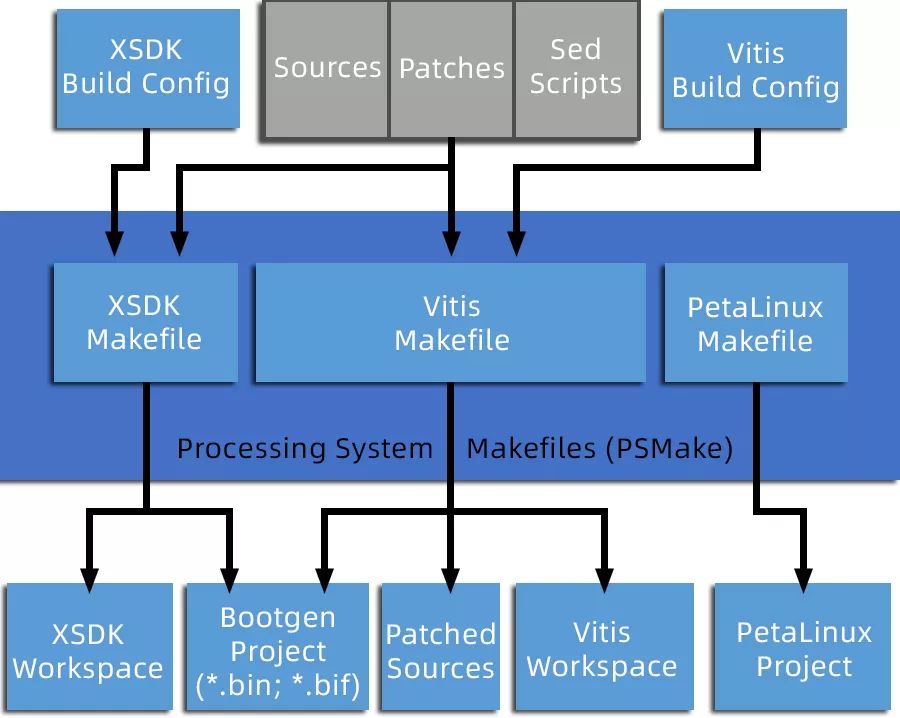

与此同时,MLE 也面向 PetaLinux 和赛灵思软件开发套件 (XSDK) 发布了一套易用型 Makefiles,并将为 Vitis 统一软件平台提供后续支持。这些处理系统 Makefiles(或简称为 PSMake)还提供在 GitHub 上。

为了加快实现 FPGA 构建环境的自动化(如用于持续集成 (CI)),并确保在开发与生命周期后期阶段完整重现设计结果,Missing Link Electronics 团队已整合出一套脚本。目前,这套脚本化 FPGA 构建环境主要面向赛灵思 Vivado 工具(版本 2016.4 或更新版本),并在 Ubuntu Linux 16.04 LTS 和 18.04 LTS 下通过测试,已通过 Apache 2.0 开源许可证提供在 GitHub 上。

作者:Andreas Braun & Stefan Wiehler

设计工程师,MLE 公司

审核编辑:黄飞

-

自动化2012-05-24 5561

-

基于PXI构建先进自动化测试系统2012-10-18 7462

-

FPGA设计之自动化2014-12-16 3443

-

汽车制造中的机械自动化技术应用2018-02-28 6856

-

自动化行业中的全厂自动化中的以太网/IP2018-10-22 2283

-

看线材测径仪在高线自动化产线中的作用2019-04-03 1184

-

自动化测试框架思想和构建2019-07-18 2577

-

如何搭建DotNet Core 21自动化构建和部署环境2020-04-23 1345

-

自动化技术在自动旋转货架中的应用是什么2021-09-14 1585

-

构建一个自动化控制系统2022-07-25 1748

-

利用LabVIEW优化多核处理器环境中的自动化测试应用2010-03-23 2361

-

FPGA构建环境的自动化怎么实现2020-03-15 2258

-

如何构建蓝牙控制的家庭自动化2023-06-27 778

-

家庭自动化系统开源构建2023-07-10 923

-

自动化迷你温室的构建2023-07-13 568

全部0条评论

快来发表一下你的评论吧 !