时序电路为什么在FPGA上综合成了latch?

电子说

1.4w人已加入

描述

有群友提问,下面的代码为什么在DC里可以综合成DFF,而在FPGA上却综合成了latch。

always@(posedge clk, negedge rstn, negedge setn)

if(!rstn)

a <= 1'b0;

else if(!setn)

a <= 1'b1;

else

a <= a;

我们可以看到这段代码有两个特别之处:

同时有异步复位和异步置位

除了复位和置位,数据要保持

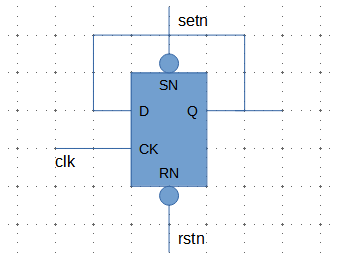

我们可以画出这段代码的逻辑图,如下图。这图也就是DC综合出来的结果。

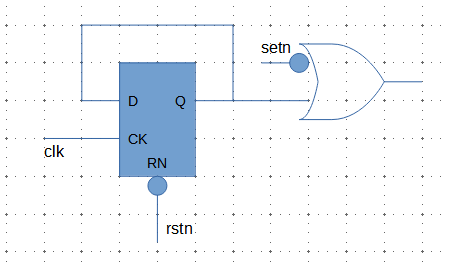

那在FPGA上为什么会变成latch呢?有人说FPGA平台没有latch,但quartus里确实报了生成latch的warning。我们来试着把电路等价变换,先把setn端简化掉:

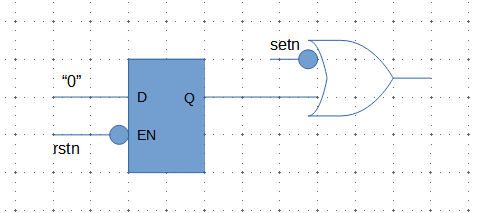

我们看到上图左边dff的逻辑,当rstn==0时,dff输出0,否则就保持。这不就是latch的逻辑吗?整理出下图:

由此可见FPGA平台综合成latch也是有可能的。

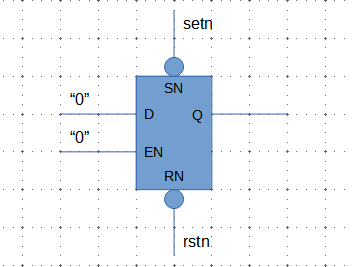

后来让群友直接看看FPGA平台综合出来的电路图,看看究竟是什么样的电路。群友回复如下:

哎,真是神奇!时钟都优化没了,直接用了一个带复位和置位的latch。看了这个电路的逻辑,确实与一开头的RTL等价的,并且还不需要数据loop了,挺简洁的。

所以得出结论,FPGA平台之所以与DC有差异,只是综合策略或者说是综合引擎优化算法的问题。综合结果都是可以用的。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

时序电路包括两种类型 时序电路必然存在状态循环对不对2024-02-06 3141

-

什么是同步时序电路和异步时序电路,同步和异步电路的区别?2023-03-25 30034

-

时序电路基本介绍2022-09-12 11017

-

什么是时序电路?2021-03-04 1913

-

时序电路基本组件及时序逻辑电路应用实例2020-09-08 8126

-

组合电路和时序电路的讲解2018-09-25 26199

-

时序电路的分析与设计方法2018-08-23 3705

-

FPGA的设计主要是以时序电路为主吗?2018-07-21 5393

-

基于FPGA技术的RS232接口时序电路设计方案2017-01-26 1325

-

数字电路之时序电路2016-08-01 19814

-

什么是时序电路2010-01-12 9053

全部0条评论

快来发表一下你的评论吧 !