锗化硅(SiGe)和硅(Si)之间的各向同性和选择性蚀刻机制

电子说

描述

引言

目前,硅的电气和热性能在微电子技术领域中应用广泛。锗化硅(SiGe)合金的使用频率越来越高,在互补金属氧化物半导体技术中,英思特通过使用SON结构以及进行各向同性刻蚀,将该工艺扩展到对Si进行Si选择性刻蚀。

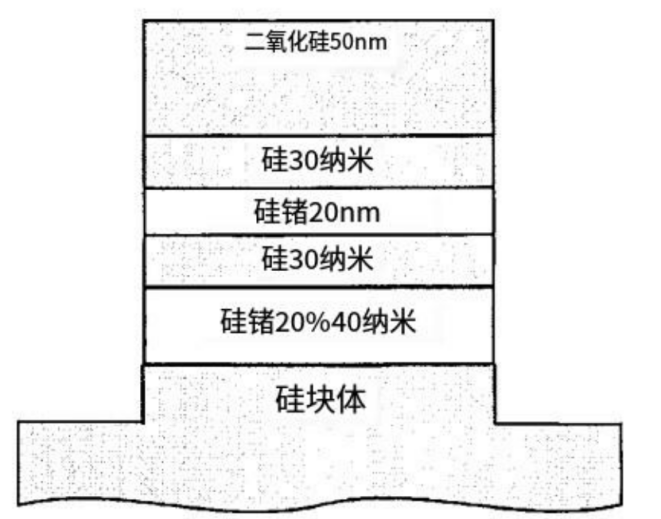

为了提高晶体管性能,基于SiGe中的传导沟道的技术目前已经在开发中。这种蚀刻是基于四氟化碳/N2/O2的气体混合物中的过程,其特征具有选择性,即Si隧道深度与SiGe层消耗之间的比值(图1)。

图1:样品用于研究该过程的选择性

图1:样品用于研究该过程的选择性

实验与讨论

该工艺在减压化学气相沉积设备中进行,其用于表征各向同性蚀刻的样品是由多层Si和SiGe层组成的。当在单晶硅衬底上通过外延生长SiGe时,只要厚度低于塑性临界厚度,SiGe层就会在压缩中产生应变。我们通过光学光刻连接0.4微米厚的光刻胶层,然后使用各向异性蚀刻工艺转移多层中的图案,从而使掩埋的Si和SiGe层可接触到蚀刻物质。

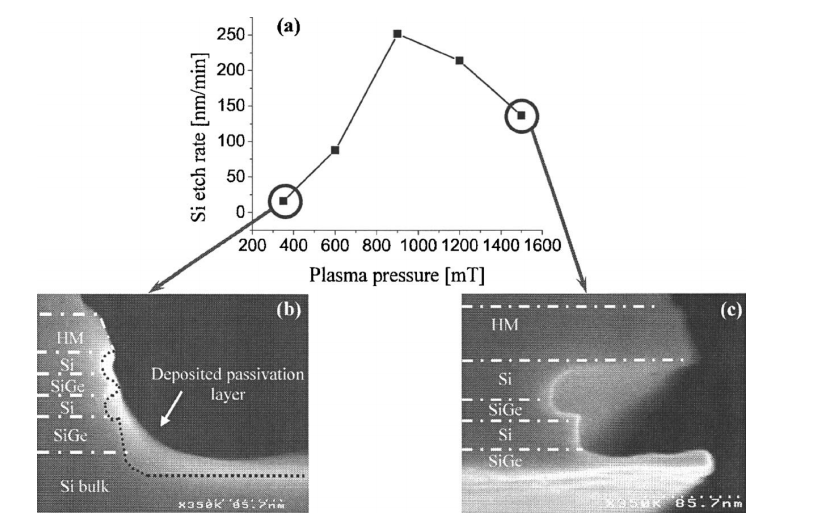

图2:一个蚀刻速率作为总压的函数的演变

图2:一个蚀刻速率作为总压的函数的演变

从700W的300SCCM CF4/200SCCM N2/500SCCM O2/100SCCM CH2F2工艺开始,蚀刻室的总压力范围为350~1500mT。图2a显示了蚀刻速率随压力的函数的演变。在低压的区域中,可以看到图2b沉积,硅层的蚀刻已经开始。这证明了蚀刻对SiGe仍然具有选择性,但蚀刻和沉积同时发生。

我们认为该沉积物是蚀刻副产物氧化的结果:在此过程中,形成了暴露于富氧等离子体中的SiFx挥发性物质。SiFx分子与这些原子发生反应,形成非挥发性分子,如SiFxOy,它可以在图案的壁上重新沉积,然后停止这一过程。

结论

通过形态表征和表面分析,英思特优化了硅选择性各向同性蚀刻,并提出了一种机理。它已经有可能获得高选择性和250nm/min的蚀刻速率,可以兼容基于SON技术的先进器件的尺寸和对小32nm的技术节点的要求。

审核编辑 黄宇

-

雷尼绍测头为什么具有各向同性2024-06-01 15313

-

碳化硅和二氧化硅之间稳定性的刻蚀选择性2022-02-15 4328

-

各向同性和各向异性工艺如何用于改善硅湿蚀刻2022-03-09 3610

-

常见的各向同性湿法刻蚀的实际应用2022-10-08 7754

-

高速硅湿式各向异性蚀刻技术在批量微加工中的应用2023-05-18 2903

-

浅谈蚀刻工艺开发的三个阶段2023-05-30 3246

-

一种新型的锗化硅(SiGe)干式选择性各向同性原子层蚀刻技术2023-06-16 2731

-

【虹科EMC测试系列】如何测量各向同性场?2022-09-08 1964

-

锗、硅、SiNx薄膜的各向同性等离子体蚀刻2023-06-26 2522

-

使用各向同性湿蚀刻和低损耗线波导制造与蚀刻材料对非晶硅进行纳米级厚度控制2023-08-22 1385

-

Si/SiGe多层堆叠的干法蚀刻2023-12-28 1894

-

SiGe与Si选择性刻蚀技术2024-12-17 2306

-

什么是高选择性蚀刻2025-03-12 1161

-

各向异性导电胶与各向同性导电胶的区别2026-02-04 377

全部0条评论

快来发表一下你的评论吧 !