MSI中断简介和生成方法

描述

MSI中断简介

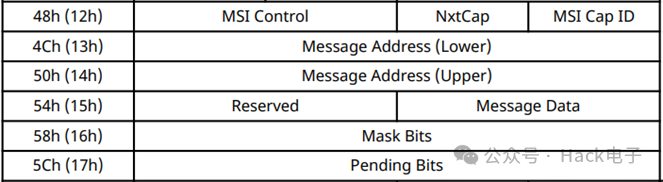

Xilinx PCIE IP中MSI中断相关的地址如下图1所示,如果想要成功产生中断,MSI Control, Message Address (Lower), Message Address (Upper)和Message Data这四个字段是必须要进行配置的,此四个字段均可通过主机的软件或者Xilinx的RP(root port)IP进行配置。

图1

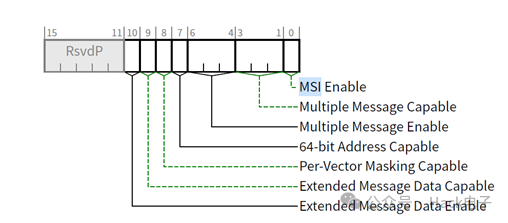

PCIE的协议对MSI Control字段的定义如图2所示,其中的MSI Enable必须使能,否则EP(endpoint)无法发送中断。Message Address (Lower), Message Address(Upper)和Message Data分别指的是memory write的TLP包的地址和数据。

图2

MSI中断的生成

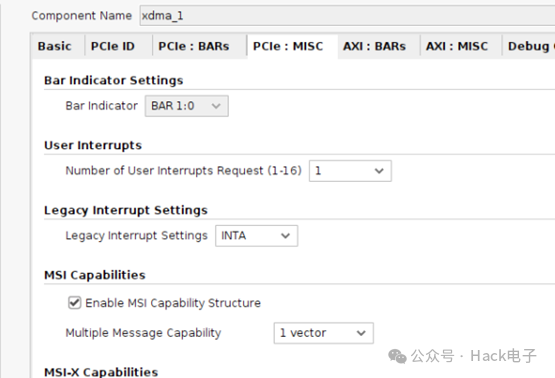

在生成MSI中断时,首先需要打开IP的MSI功能,以AXI Bridege IP为例,如图3所示勾选Enable MSI Capability Structure。

图3

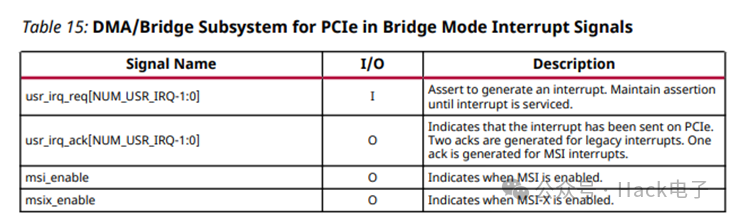

用于产生中断的信号如下图4所示,要发送MSI中断之前需要确定msi_enable是否被拉高,如果msi_enable没有被拉高,IP是无法发送中断的。Usr_irq_req需要一直保持为高直到确认中断已被成功处理,这里需要设置一个·机制,需要软件配合进行实现,如软件在处理完中断后要向FPGA内与逻辑约定好的寄存器写1,逻辑在检查到此寄存器被写1后,再将usr_irq_req置低。

图4

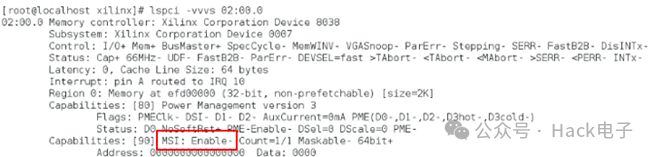

通常逻辑在发送MSI中断时不会检测msi_enable信号,此信号一般不会由EP端进行控制,使能MSI功能通常在软件侧进行操作,在linux系统中使用lspci -vvvs 指令即可查看MSI功能是否被使能,若打印信息如下图5所示,显示MSI:Enable-,则表示MSI功能未被使能,此时逻辑即使拉高usr_irq_req信号,主机也不会接收到中断。用户可以通过使用setpci指令来使能MSI功能。从图1和图2可得,Xilinx Pcie EP的MSI Enable在4a的第一位,可以使用setpci –s 24:00.0 4a.w=1 指令来使能MSI功能。使用上述指令写完4a寄存器后,图5的MSI:Enable-会变至MSI:Enable+,表示MSI功能使能成功。

图5

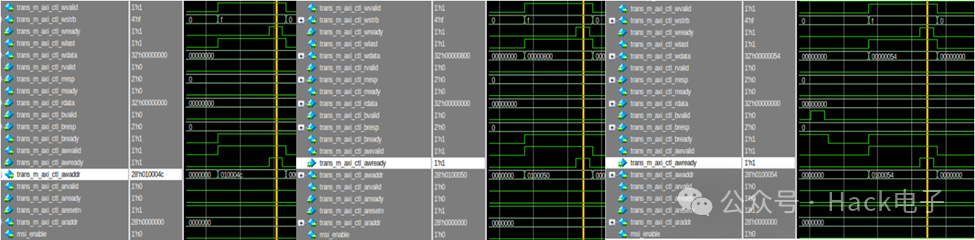

在Pcie链路稳定后,RP端将会发送配置写对EP端进行配置,图6为RP侧对EP侧中Pcie MSI的message address和message data字段的配置,RP首先对EP的4C寄存器全写0,表示Message Address(Lower)为全0,随后RP对EP的50寄存器写32‘h800,即Message Address(Upper)的值为32’h800,写完这两个寄存器后,RP也需要写对应的寄存器来进行记录,当随后接收到地址为64’h800_0000_0000 memory write TLP包后,会将此包解析为中断请求。RP在配置EP的message字段时,只需要将所要的message data写入到54寄存器,如图6所示,RP将32’h54写入到了EP的message data字段中,完成了EP侧的message address和message data的配置。

图6

图7

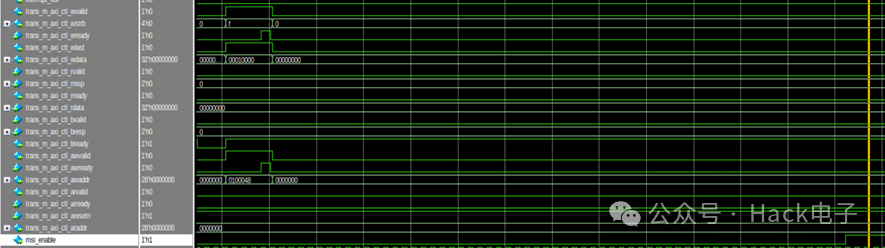

RP对EP的MSI功能的使能,可通过对EP的48寄存器写32’h10000即可,本篇文章参考的是PG213中Register(Type0:Enpoint)表格,不同厂商的MSI寄存器所在的位置通常不同,在配置时需要参考对应厂商的IP手册。如图7所示,RP侧在配置完EP的MSI control寄存器后,EP的msi_enable会变为高,至此RP完成了EP侧 MSI功能的必要配置。

在完成上述配置后,用户逻辑在拉高usr_irq_req后,会发现usr_irq_ack随后被拉高,这表示IP已完成中断的发送,如果在拉高usr_irq_req后,usr_irq_ack没有被拉高,又或者usr_irq_fail拉高,这种情况大概率是EP msi_enable没有被成功使能。在EP端拉高usr_irq_req信号一段时间后,会发现RP侧的interrupt_out信号拉高,如图8所示,表RP侧接收并识别了EP发送的中断信号。

图8

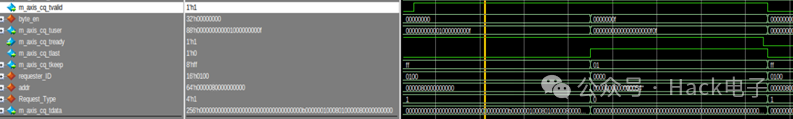

图9为在Pcie RP IP接口截取的TLP包,EP发送MSI中断即为发送memory write的TLP包到RP,RP在接收到此特定地址和数据的TLP包后,会将其解析为中断,Pcie的CQ接口接收到的包为对端发送的request 包,即EP侧发送的memory write TLP包可在此接口截取到。

图9

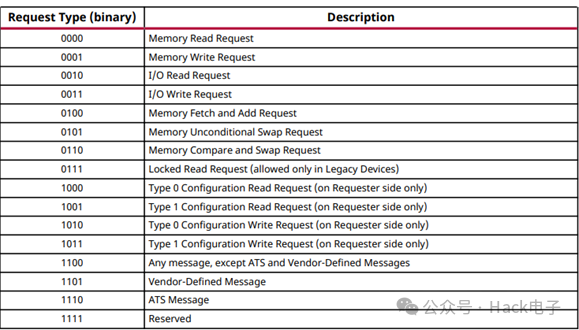

在EP发送中断后,RP的m_axis_cq_tvalid会拉高,此时会收到TLP包,经过解析后发现此包的Request_Type为4’h1,在图10中查找,可发现此包为memory write类型的包,此包的地址在m_axis_cq_tdata的前64bit,地址为64’h800_0000_0000,与PR写入至EP配置空间的4C(Message Address (Lower))和50(Message Address (Upper))寄存器的数值一致。RP收到的第一拍数据byte_en为0,表示第一拍中不存在数据载荷,在第二拍中可以看到byte_en的数值为32’hf,表示此拍存在数据,m_axis_cq_tdata的前64bit即图中addr字段的显示的数值为64’h54,表示memory write的数据为54,与RP写入到EP配置空间的54(Message Data)寄存器的内容一致。

图10

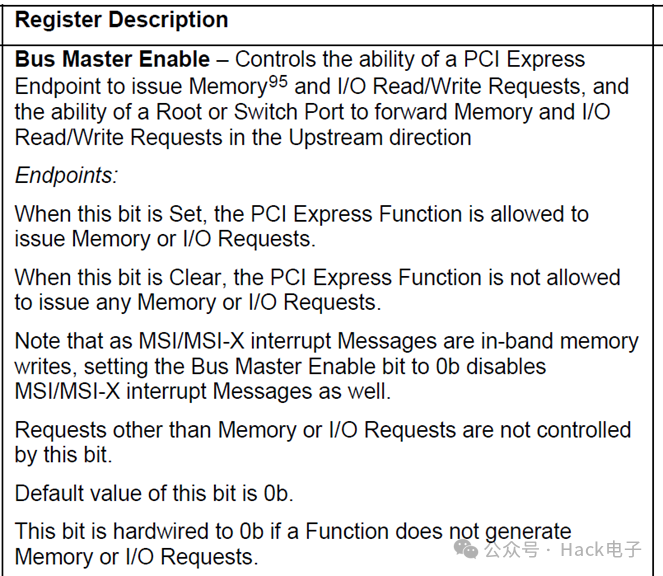

MSI和MSI-X中断都是EP端向RP端发送memory write的TLP包,所以bus master的功能也需要打开,在bus master打开后EP才可以主动发送request到RP端。

图11

审核编辑:汤梓红

-

PCIE MSI中断的配置2018-06-21 4060

-

PWM生成方法2021-08-09 1478

-

OTA完整包与差异包的生成方法分别是什么2022-02-10 2134

-

PCIe设备发出MSI-X中断请求的方法2022-02-16 1105

-

基于混沌序列的种子密钥表生成方法2009-09-02 774

-

两种空间矢量脉宽调制生成方法的分析与比较2016-03-30 936

-

一种多尺度多视点特性视图生成方法的研究和应用_谢冰2017-03-15 827

-

一种新颖的自动化攻击图生成方法_武健2017-03-19 919

-

一种新的DEA公共权重生成方法2018-01-13 1206

-

PCIe中断机制介绍(MSI)2018-08-31 21962

-

教大家如何处理x86处理器中MSI-X中断请求2021-08-12 8355

-

简述MSI和MSI-X中断机制2021-08-10 7061

-

基于Python-casacore的射电测量集文件生成方法2021-09-15 926

-

x86处理器如何处理MSI-X中断请求2021-12-17 1100

-

PWM信号生成方法 PWM调制原理讲解2024-11-28 7353

全部0条评论

快来发表一下你的评论吧 !