Arm发布Neoverse V3和N3 CPU内核

描述

在计算市场持续迎来变革的背景下,Arm公司发布了其最新一代Neoverse CPU内核设计,分别为Neoverse V3(代号Poseidon)和N3(代号Hermes),两款内核将为服务器、云计算和基础设施领域带来更大规模和更快速度的计算能力。

Part 1

Neoverse计划的背景

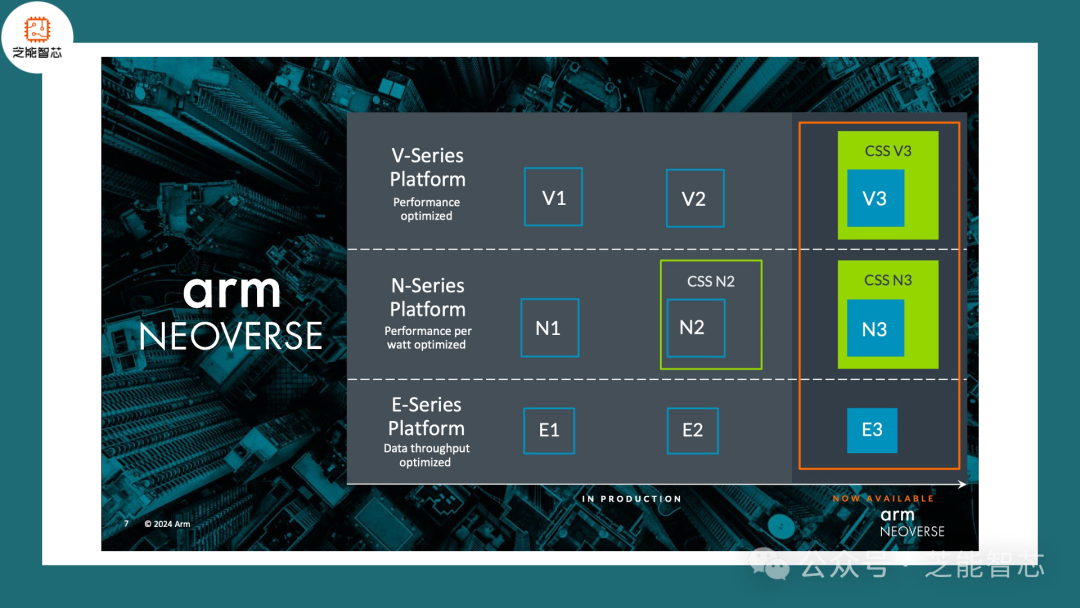

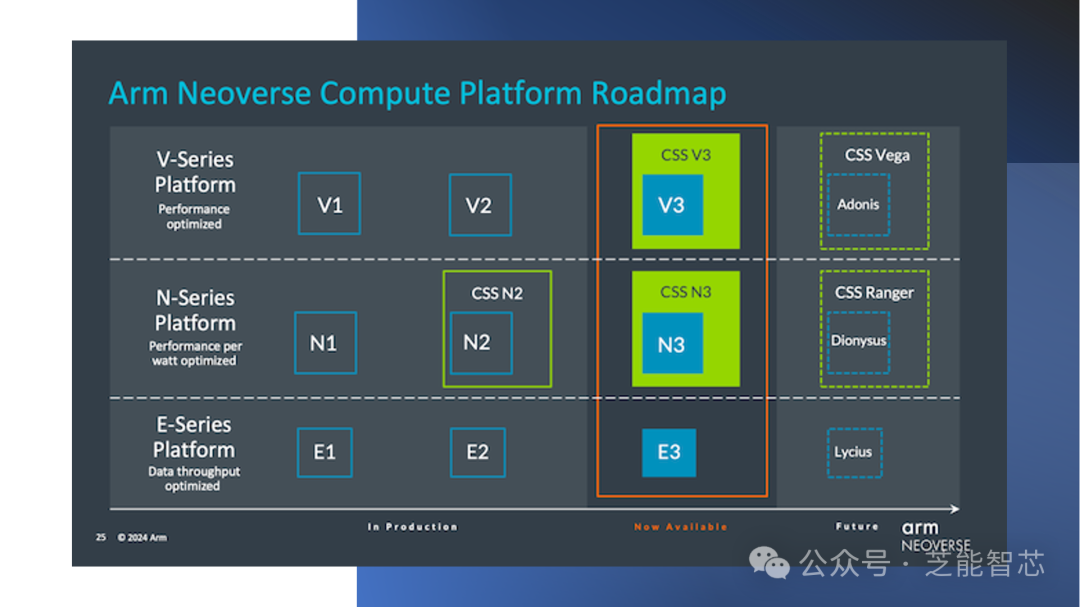

五年前,Arm宣布了Neoverse计划,旨在推动服务器、云计算和基础设施CPU核心的发展。该计划包括三个系列:V系列针对高性能应用,E系列针对高效能应用,以及N系列则着重于能效比。Neoverse系列已经在市场上取得了巨大成功,受到云服务提供商和基础设施市场的广泛认可。

Part 2

Neoverse V3 CPU内核

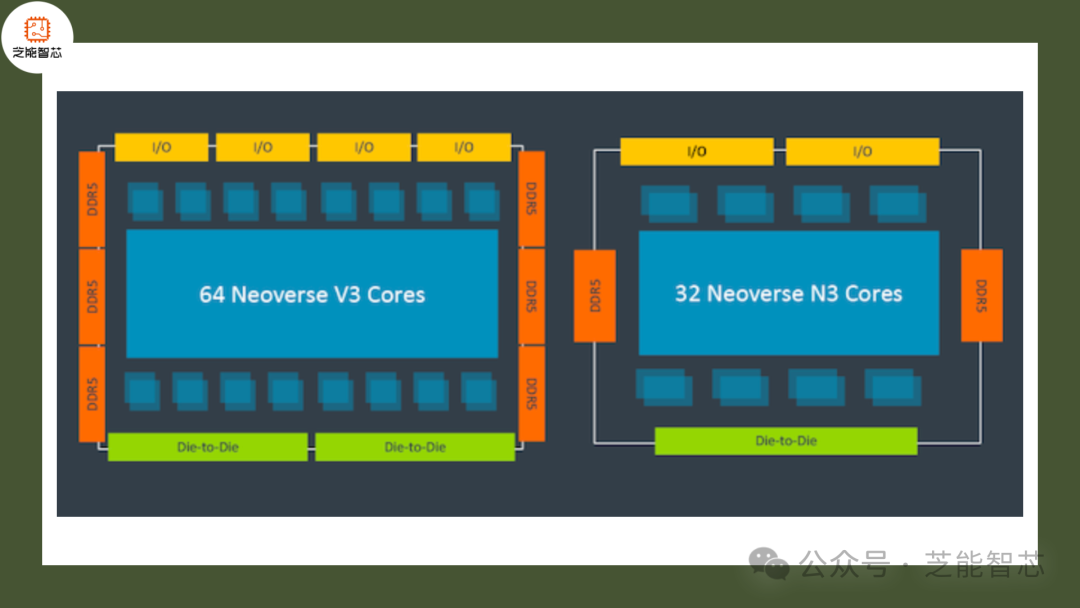

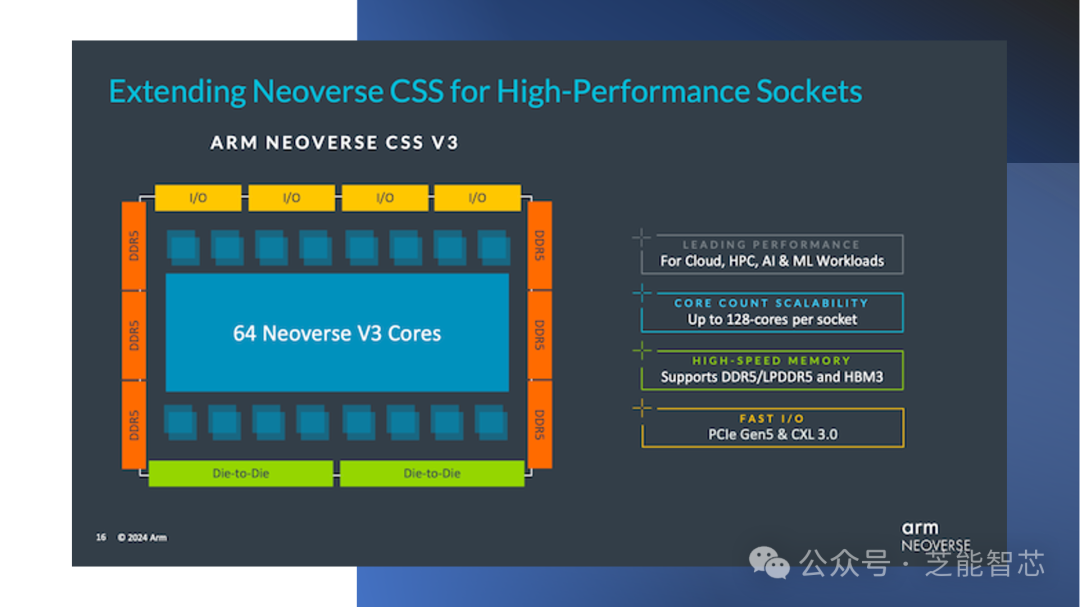

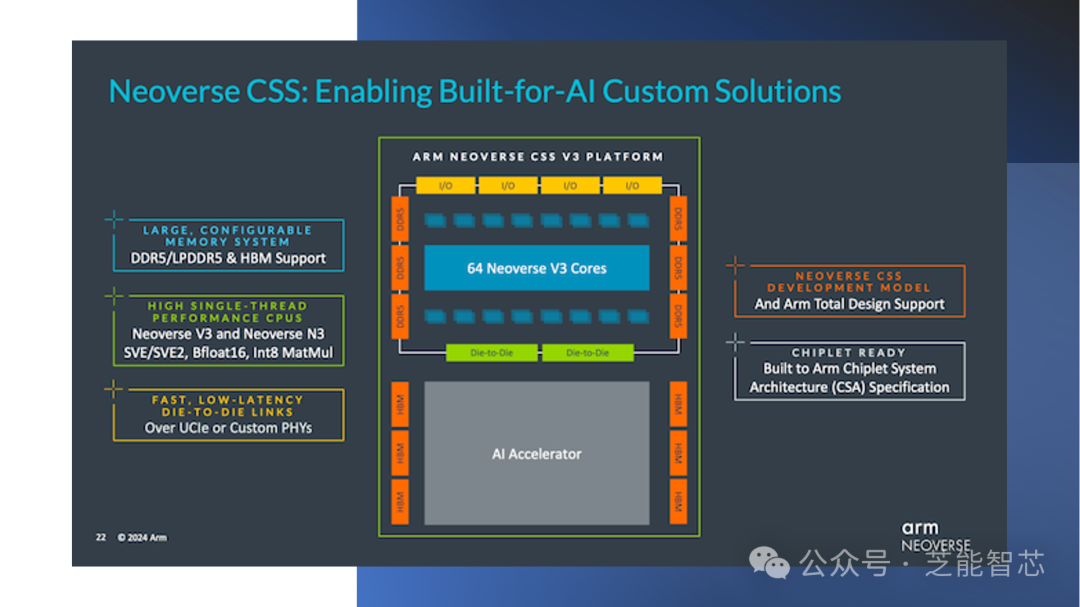

Neoverse V3是针对高性能系统的设计,最多可配置128个核心。这一设计引入了CXL 3.0和HBM3技术,同时提供了更大、更快的计算子系统(CSS)。V3的单线程性能和内存支持得到了显著提升,为高端应用提供了更强大的计算能力。

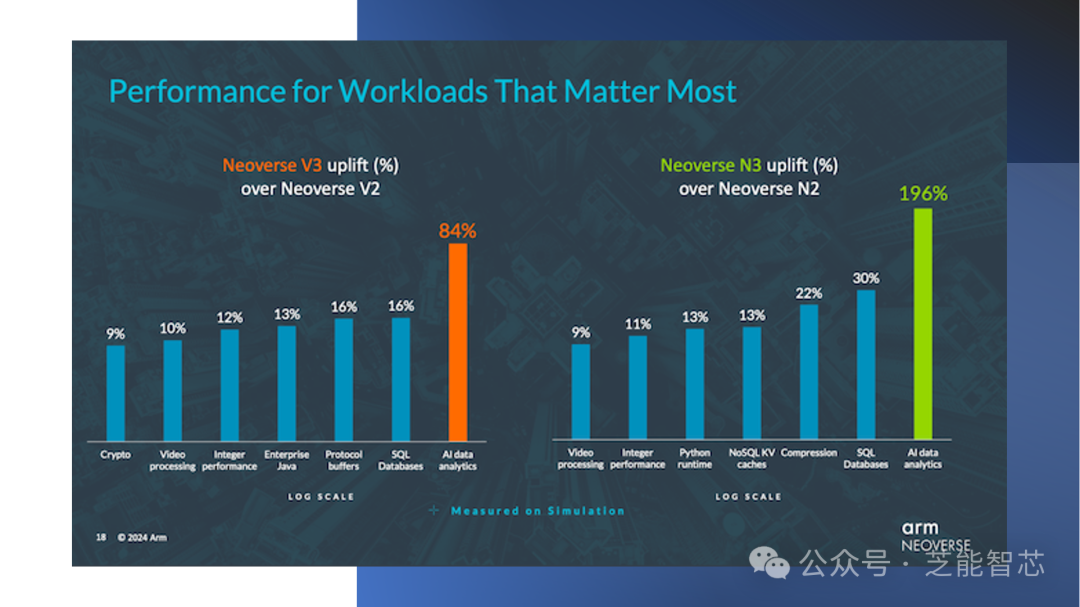

在性能上具备很大的提升,V3旨在提供最高单线程性能,在模拟测试中性能提升在10%到20%之间。

同时,V3对多个方面进行了优化,特别是在网状互连方面,以提升整体性能和系统效率。V3支持最新的内存和I/O标准,包括LPDDR5、DDR5和HBM3,并将CXL支持从2.0升级到3.0,使得计算能力更加灵活和高效。

这款V3提供了现成的CSS设计,以便客户更快速地集成到自己的芯片设计中,同时支持芯片间互连,为系统架构提供更多选择。

Part 3

Neoverse N3 CPU内核

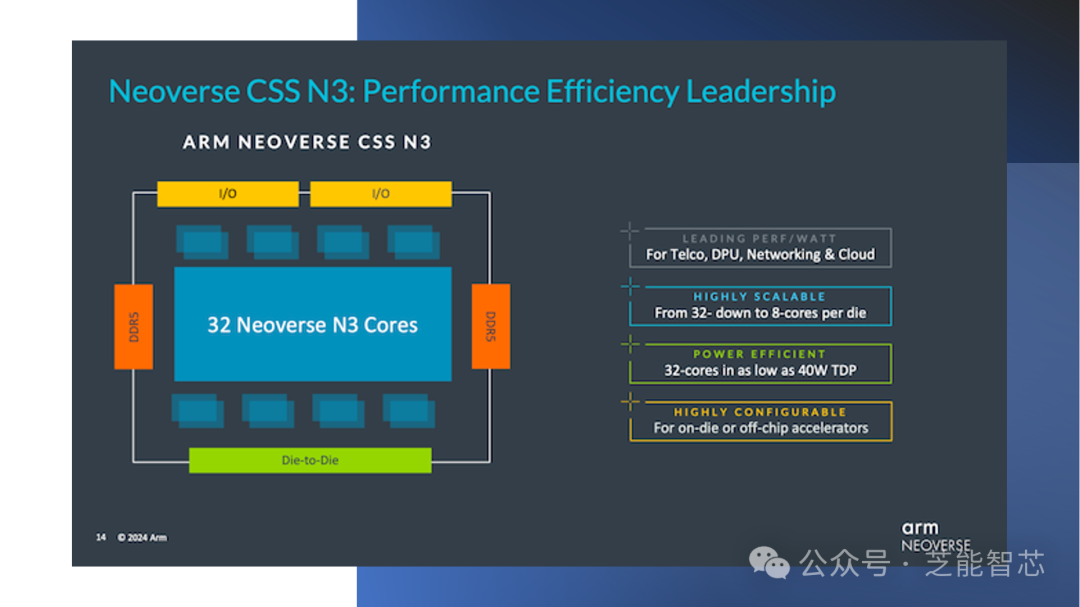

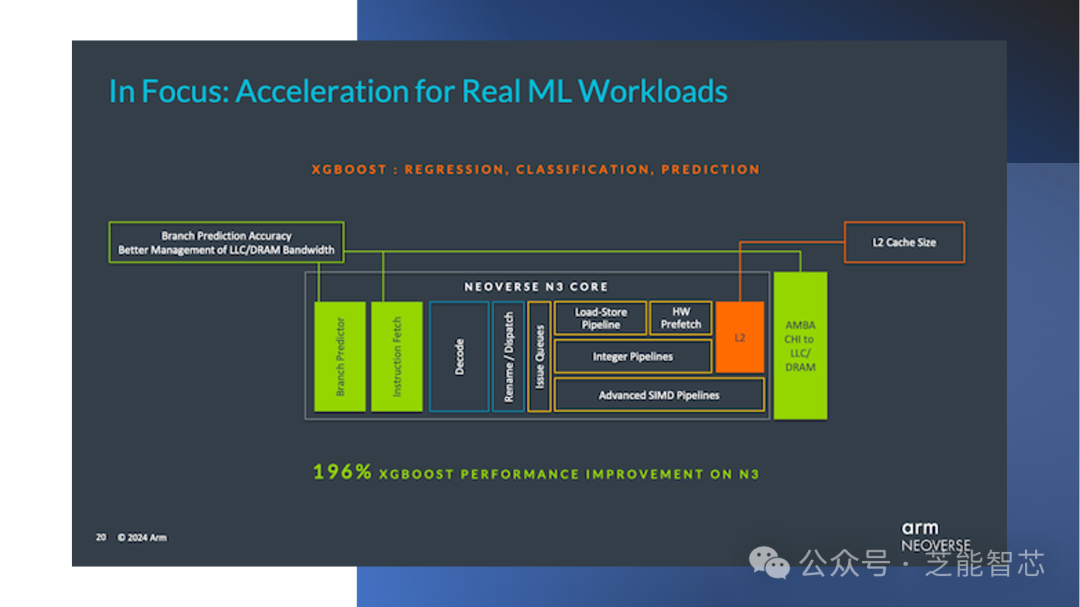

Neoverse N3是一款高能效的平衡型CPU内核,最多可配置32个核心。N3的每瓦性能提升了20%,在40W TDP下每个CPU核心的功耗略高于1瓦,为能效比提供了显著改进。N3的性能提升在10%到30%之间,具体取决于不同的工作负载。内部结构方面进行了一些优化,特别是在缓存和内存子系统上,以提高整体性能和数据处理效率。

N3同样支持最新的PCIe和CXL标准,并提供了芯片间互连功能,为系统设计提供更多灵活性和可扩展性。

小结

Arm还公布了未来CPU核心版本的代号,包括Lycius、Dionysus和Adonis。这些核心将进一步推动Arm在计算市场的发展,并为客户提供更多选择和更好的性能,Arm对未来的发展充满信心,将持续为客户提供领先的处理器技术和解决方案。

审核编辑:刘清

-

Arm新Arm Neoverse计算子系统(CSS):Arm Neoverse CSS V3和Arm Neoverse CSS N32024-04-24 3106

-

Arm Neoverse CSS N3 助力快速实现出色能效2024-03-26 1151

-

Neoverse CSS V3助力云计算实现TCO优化的机密计算2024-03-14 1388

-

Arm 更新 Neoverse 产品路线图,实现基于 Arm 平台的人工智能基础设施2024-02-22 990

-

ARM Neoverse™N1核心技术参考手册2023-08-29 969

-

Arm Neoverse™ N1 PMU指南2023-08-12 884

-

ARM Neoverse系列服务器CPU研究分析2023-06-12 5776

-

Arm Neoverse V1的AWS Graviton3在深度学习推理工作负载方面的作用2022-08-31 3907

-

互联网巨头纷纷启用Arm CPU架构,Arm最新Neoverse V1和N2平台加速云服务器芯片自研2020-09-30 1750

-

努比亚N3惊艳发布 续航表现非常出色2018-03-09 2895

-

2014 OPPO N3 新品发布会2014-10-28 4162

-

TDA9381PS/N3/32012-12-14 2923

全部0条评论

快来发表一下你的评论吧 !