深入解析TC3xx芯片中的SMU模块应用

电子说

描述

SMU模块是Aurix芯片自带的一个功能安全硬件模块,它能够收集其他模块(PMS, MTU, SCU, CCU, e.g.)由于硬件功能安全机制产生的报警(Alarm),然后,SMU模块通过用户配置能够产生内部或者外部的动作/响应,也可以不产生任何动作。本文将详细介绍SMU模块。

01

SMU功能概述

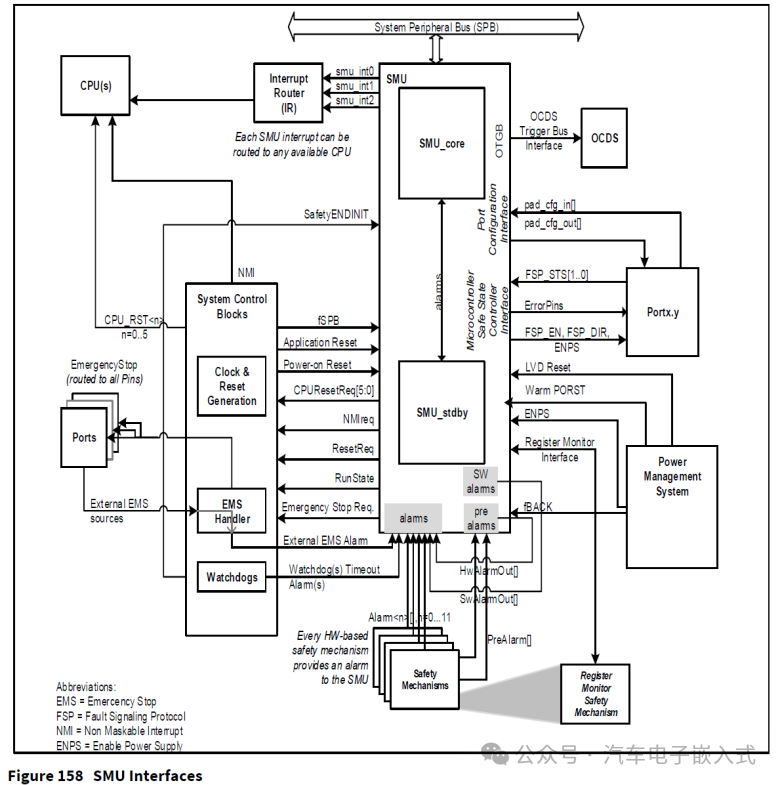

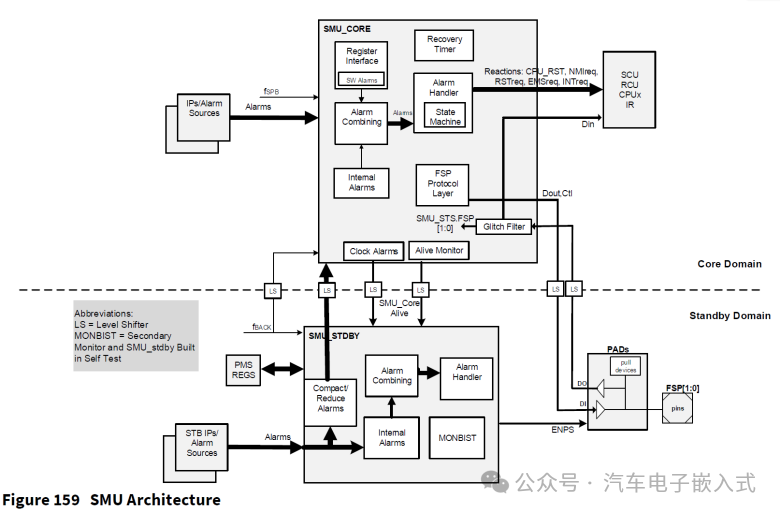

SMU 是安全架构的核心组件,提供通用接口,用于管理存在故障的微控制器的行为。SMU 集中所有与不同的硬件和软件安全机制相关的警报信号。每个警报都可以单独配置为触发内部操作和 / 或通过故障信号协议(FSP, Fault Signaling Protocol)向外部通知存在故障。 每一报警的严重程度应根据安全应用的需要进行配置:默认情况下,除看门狗超时报警外,每一报警反应都被禁用。 为了进行调试和诊断,报警信号设置了一个粘滞位(sticky bit),该粘滞位可适应应用程序或系统重置。SMU 还实施了一些与专用安全机制的管理和测试相关的内务管理(housekeeping functions)功能。 可以使用特殊测试模式测试 SMU 本身,以检测潜在故障。除了寄存器访问保护外, SMU 还实施了配置锁定机制(configuration locking mechanism)。 此外,为了缓解(mitigate)潜在的常见原因故障, SMU 分为两部分:

SMU_core: 位于core domain.

SMU_stdby: 位于stand-by domain.

SMU_CORE 和 SMU_Stdby 的设计方式和时间安排各不相同。SMU 的两个部分之间存在物理隔离。它们位于不同的时钟和电源域中。这允许 SMU 处理任何传入的报警,而不管用于生成此报警的时钟频率如何。此外,在 fSPB (或衍生产品) 上生成的报警事件将由 SMU_CORE 处理,而在 fBACK 上生成的报警事件将由 SMU_Stdby 处理。这样,所有时钟活动监视器警报都将在生成时钟域中处理。此外,与功率和温度有关的报警也以不同的方式处理,因为它们由 SMU_CORE 和 SMU_Stdby 处理。可以在 SMU_CORE 或 SMU_Stdby 中配置对这些报警的一个或多个反应(Actions)。

此外,为了检测 SMU_CORE 中的错误,将从 SMU_core 向 SMU_Stdby 发送警报 SMU_core_alive。对这些警报的反应(Actions)可在两个域中配置。 但是,对于 SMU_Stdby ,只有无反应(no reaction)或将 Errorpins 配置为高阻抗状态作为报警反应。

SMU 与嵌入式安全机制相结合,可以在容错时间间隔内检测并报告超过 99% 的微控制器严重故障模式。可在 SMU 中配置容错时间间隔的计时特性。

1.1 SMU架构

1.2 SMU_core

核心域 SMU (也称为 SMU_core) 从安全概念定义的硬件监视器(hardware monitors)的安全机制收集大多数警报信号。 报警映射(Alarm Mapping)部分(后面的章节)指定报警接口(alarm interface)并将其分类为报警组(alarm group)。 报警组定义逻辑映射,用于将报警信号映射到内部状态寄存器。 “报警处理”部分描述了配置选项。配置选项指定检测到报警事件时 SMU_core的行为。警报事件可以触发内部操作和 / 或激活错误针脚,以指示外部环境存在故障。SMU_CORE Control Interface 部分指定了软件如何控制 SMU_CORE 以及硬件操作的相关性。故障信号协议 (FSP) 部分描述了外部故障信号协议的属性,这些属性定义了错误针脚(ErrorPin)的计时和逻辑属性。

1.3 SMU_stdby

备用域 SMU (也称为 SMU_Stdby) 从检测时钟 (无时钟) ,电源 (电压过低 / 过高) 和温度故障 (温度过低 / 过高) 的模块收集警报。SMU_Stdby 还会收集 SMU_Alive 报警信号,当 SMU_CORE 在报警升高后未触发反应时,该信号会发出通知。此外, SMU_Stdby 实现了内置自检功能,允许用户测试 SMU_Stdby 对报警信号的反应以及从次级电压监视器到 SMU_Stdby 的完整报警路径。有关辅助监视器和 SMU_Stdby 内置自检的详细信息,请参阅电源管理系统一章。

“报警映射”部分指定报警接口,并将它们分为两个报警组。“报警处理”部分描述了可以指定的配置选项。配置选项指定检测到报警事件时 SMU_Stdby 的行为。警报事件可以触发启动 ErrorPins (错误针脚) ,该 ErrorPins (错误针脚) 表示外部环境存在故障。

02

SMU功能详述

2.1 SMU_core

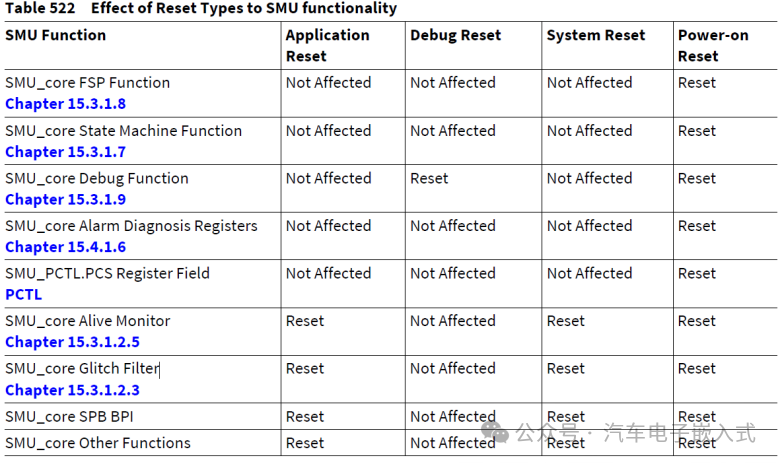

2.1.1 Reset类型

SMU_CORE 需要多种Reset类型。Reset类型在系统控制单元中完全指定。SMU_CORE 要求的重置类型为:

Power-on Reset

System Reset

Debug Reset

Application Reset

下表指定了每个重置(Reset)类型的范围,这些重置类型的配置和逻辑是SMU_core 控的。

2.1.2 接口(Interfaces)概述

这一章描述SMU_core和其他模块之间的接口信号。

2.1.2.1 SMU_core到SCU的接口

与系统控制单元连接的警报事件所导致的内部操作。 接口信号为:

Emergency Stop Request

Reset Request

NMI Request

CPU Reset Request

2.1.2.2 SMU_core到IR的接口

与中断路由模块相连的报警事件导致的内部操作。 接口信号为:

SMU Interrupt Service Request 0

SMU Interrupt Service Request 1

SMU Interrupt Service Request 2

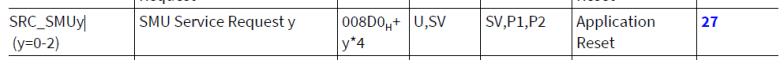

SMU 中断服务请求到中断路由 (IR) 中断节点的映射可在中断路由器一章 (SRC_SMUy, y=0.2) 中找到。

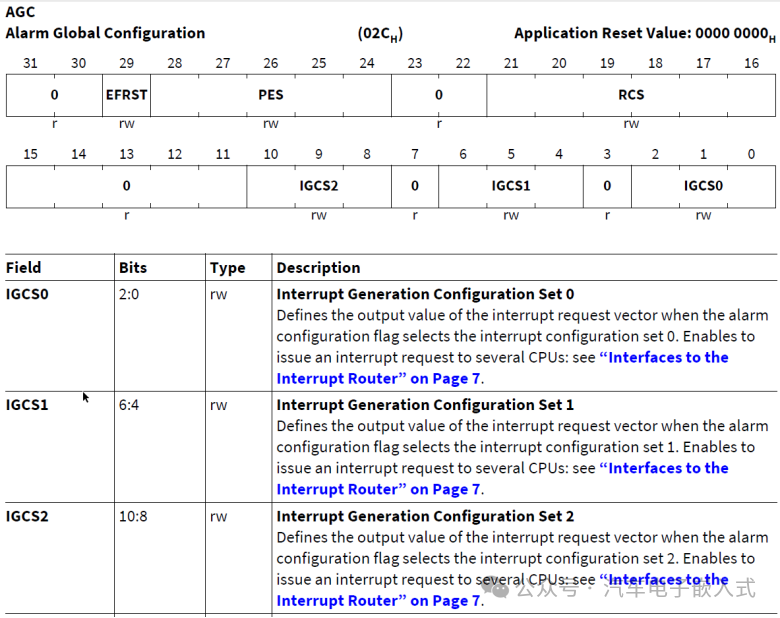

AGC.IGCSx , x= { 0 , 1 , 2 } 寄存器字段提供了软件接口来控制 SMU 如何触发中断路由器的中断请求。

每个AGC.IGCSx是一个3-bits的位域信号:

AGC.IGCSx[0] shall be set to ‘1’ to trigger SMU Interrupt Service Request 0

AGC.IGCSx[1] shall be set to ‘1’ to trigger SMU Interrupt Service Request 1

AGC.IGCSx[2] shall be set to ‘1’ to trigger SMU Interrupt Service Request 2

AGC.IGCSx的使用在Alarm Configuration章节描述。

2.1.2.3 SMU_core到Ports(ErrorPin)的接口

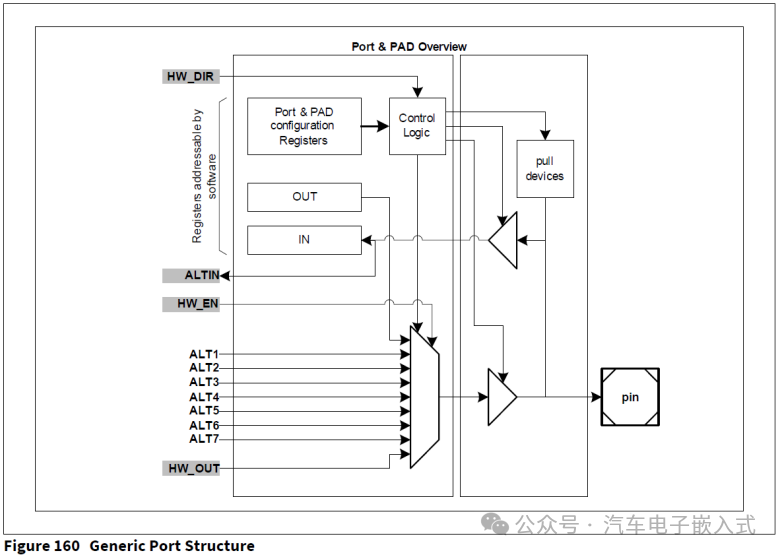

通用端口结构如下图所示。

端口引脚(Port Pin)可以通过 ALTx 输出线路连接到外围设备。这是开机重置后端口的默认状态 。SMU_CORE 使用 HW_DIR , AlTIN , HW_EN , HW_OUT 信号连接到端口。当 HW_EN 端口输入由 SMU_CORE 驱动时, SMU_CORE 将完全控制该端口,绕过与 ALTx 输入使用相关的任何其他软件配置。

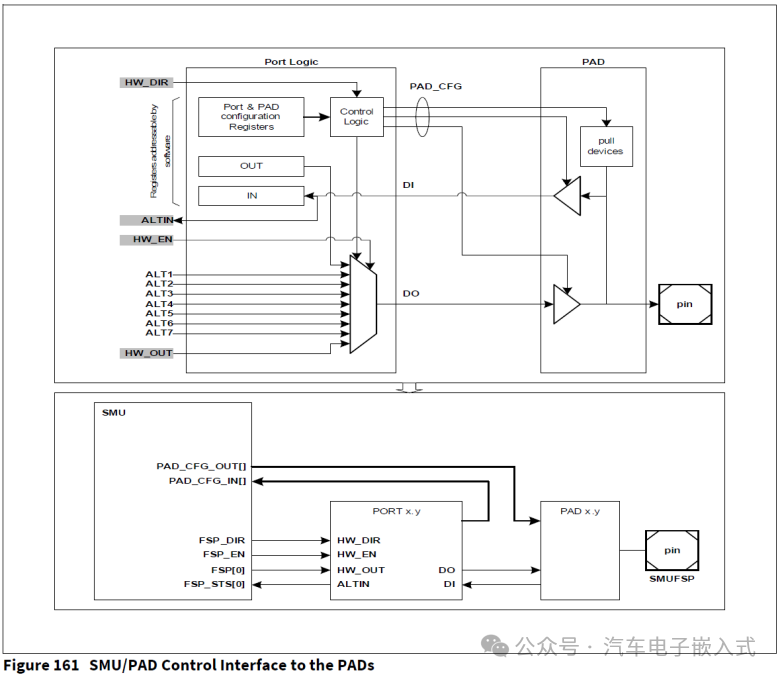

下图 提供了端口结构的更详细概述,并突出显示了 SMU_CORE 连接中涉及的信号。

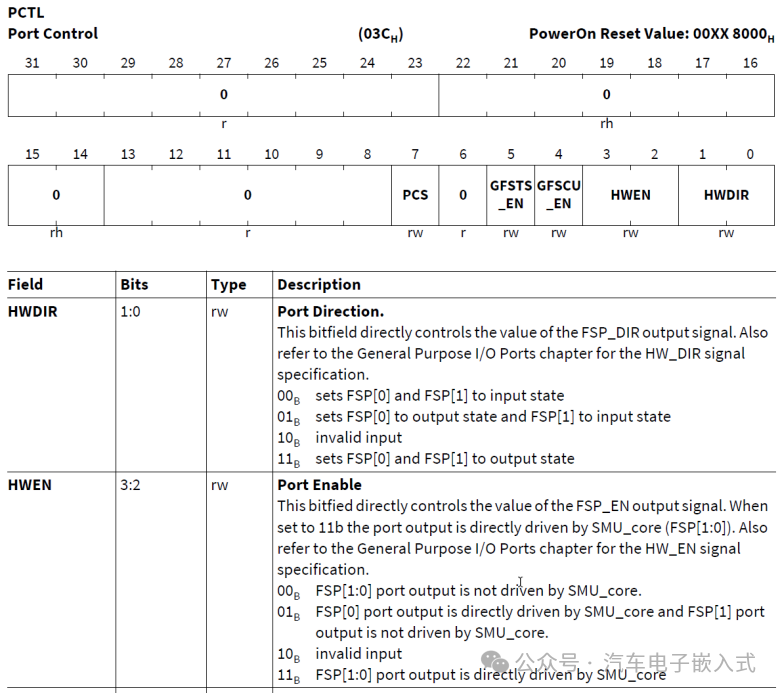

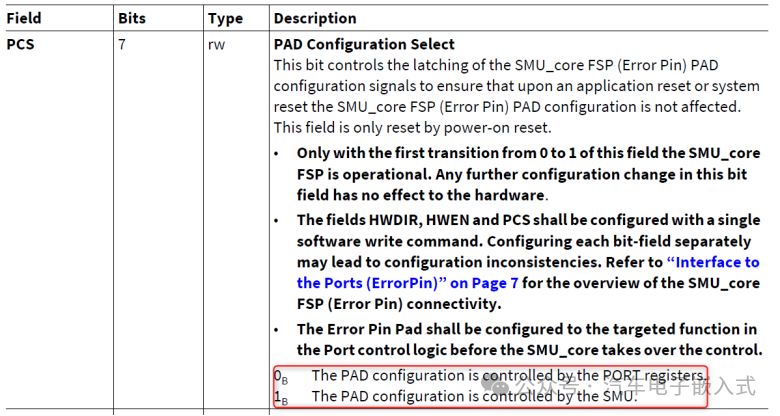

SMU_FSP0(也就是上图中的FSP [0]) 由硬件控制。FSP_DIR和FSP_EN由软件控制,控制寄存器如下:

PCTL.HWDIR直接驱动FSP_DIR输出。

PCTL.HWEN直接驱动FSP_EN输出。

PCTL.HWDIR 和PCTL.HWEN同时也会控制SMU_FSP1.

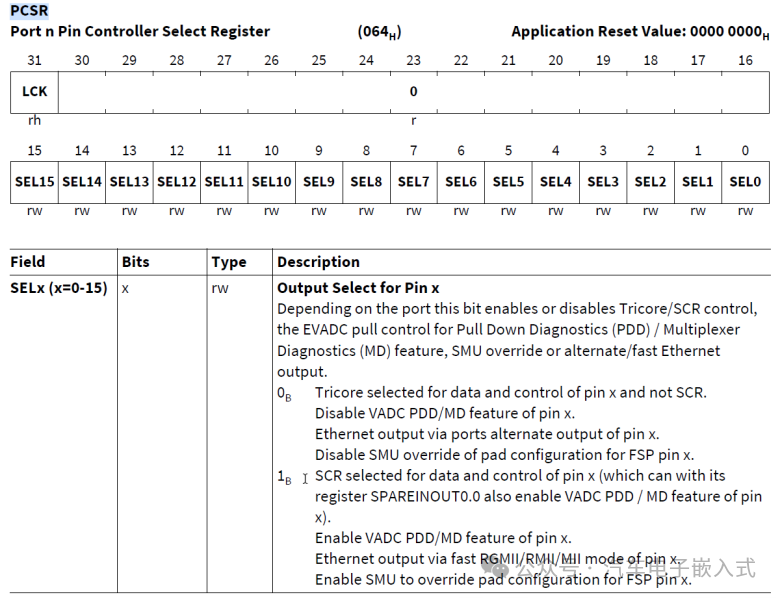

PCTL. PCS 位域 ,与 P33_PCSR.SEL 位字段配合使用,使软件能够更改 FSP [0] 的 PAD 控制。借助 P33_PCSR. SEL , PCTL HWDIR , HWEN 和 PCS 字段,软件可以控制 FPSP [0] PAD 所有权从 GPIO 过渡到 SMU 硬件完全控制。

SMU_FSP1 PAD 不在 SMU_CORE 的控制下。通过软件配置PCTL PCS 字段,不能更改 SMU_FSP1 的 PAD 控制。但是, PCTL HWDIR 和 HWEN 字段可用于超控(overrule) PAD 配置。

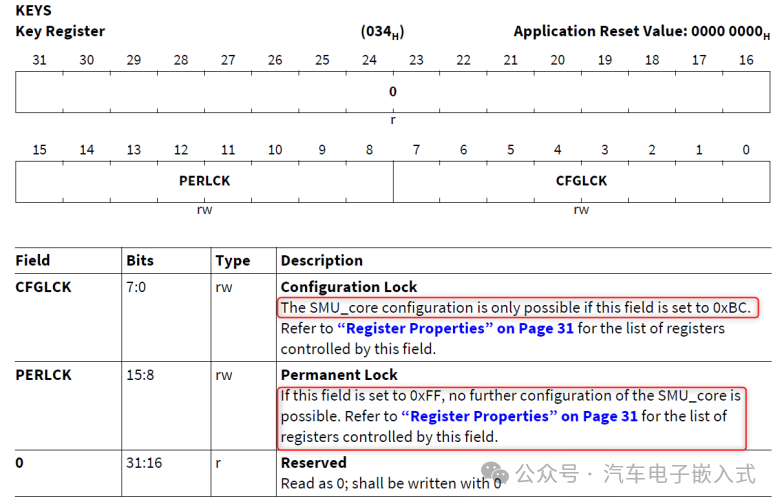

PCTL 寄存器的内容被KEYS寄存器锁定,并且只能通过开机重置(power-on reset)进行重置,因此即使存在应用程序或系统重置, PAD 配置也将保持不变。此外, PCTL 寄存器使用安全触发器安全机制实施,该机制在运行时检测随机硬件故障引起的任何位变化。

参考SMU_core Integration Guidelines章节,描述了使用ErrorPin时的SMU和PORT模块的配置步骤。

2.1.2.4 SMU_core到寄存器监控的接口

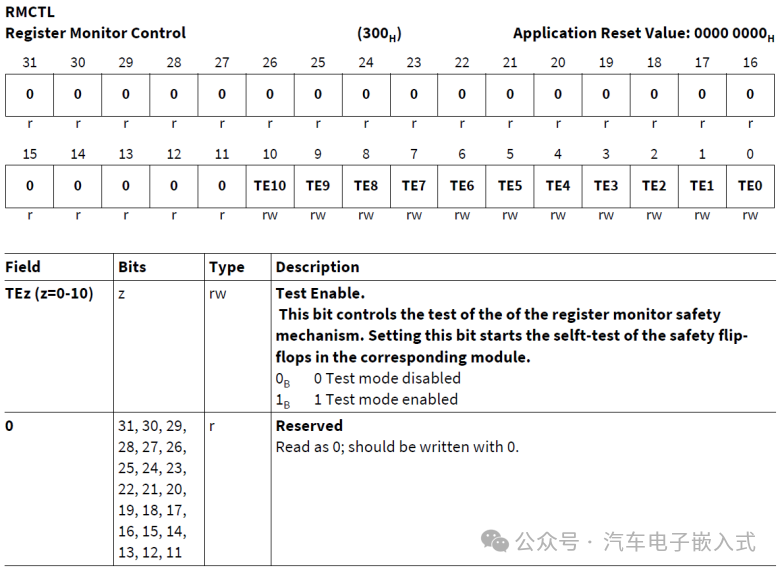

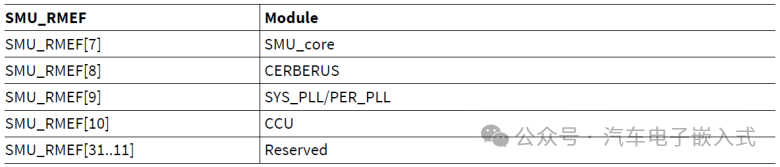

寄存器监视器控制 (RMCTL) ,寄存器监视器错误标志寄存器 (RMEF) 和寄存器监视器自检状态寄存器 (RMSTS) 之间的接口指定如下:

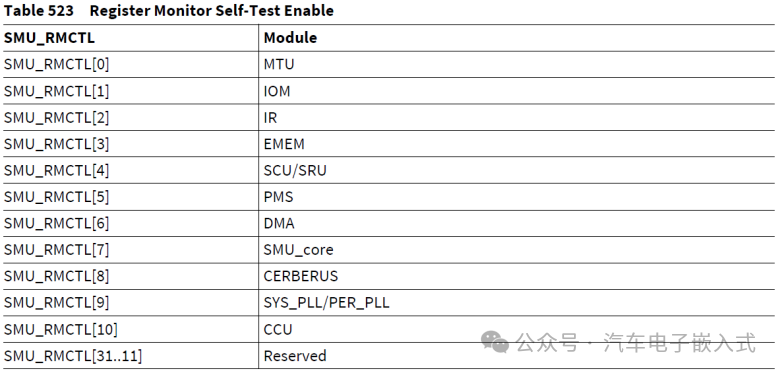

RMCTL.TE[31:0]

-将 RMCTL.TE[i] 设置为 1 将对给定模块的安全触发保护寄存器启动自检 (请参阅表 523) 。

-在自检结束时,必须将这些位设置回 0。

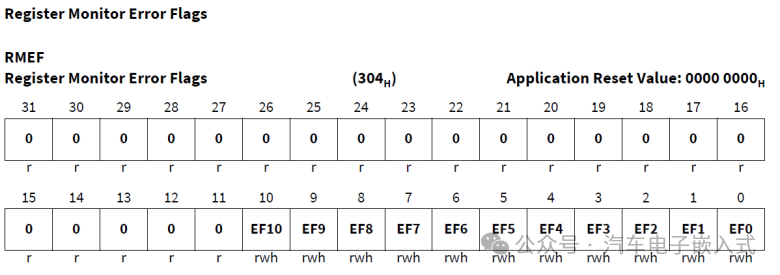

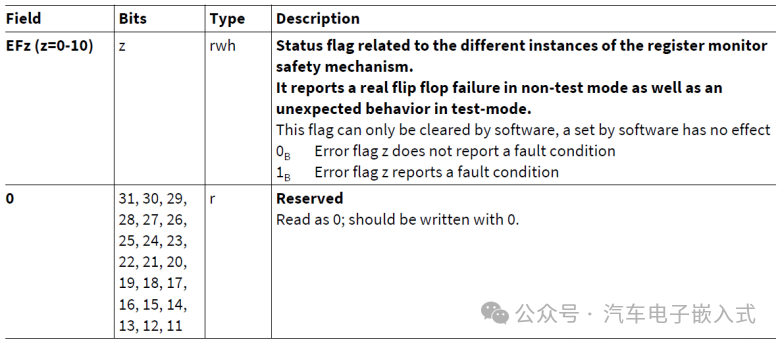

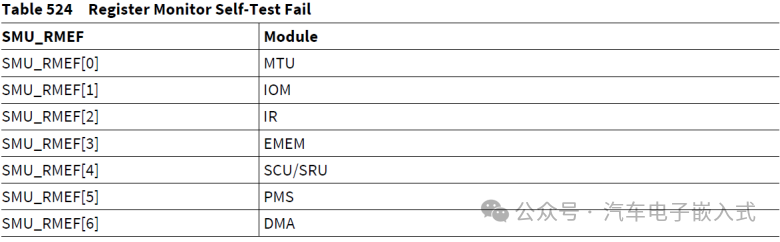

RMEF.EF [31:0]

-无论 RMTL.TE[i] 的状态如何,只要在给定模块的安全触发保护寄存器中检测到故障, RMEF.EF[i] 就会设置为 1 (参见表 524) 。

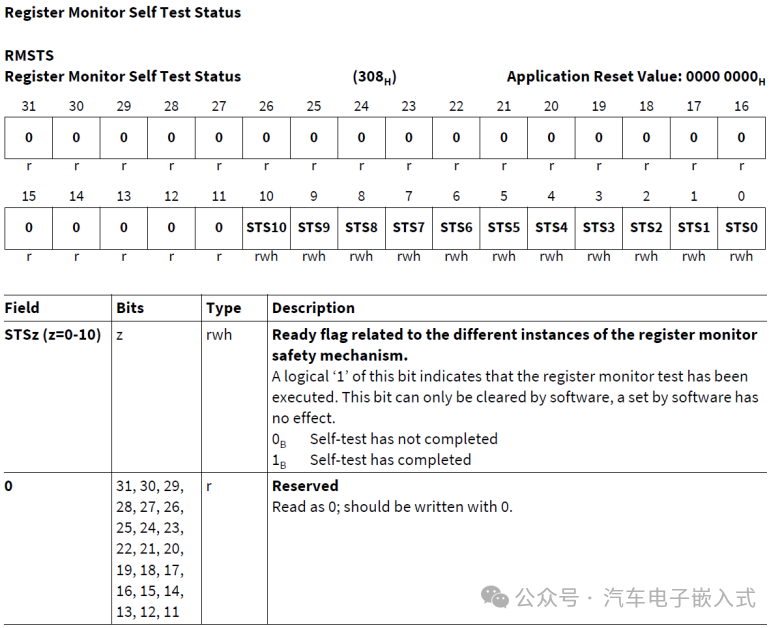

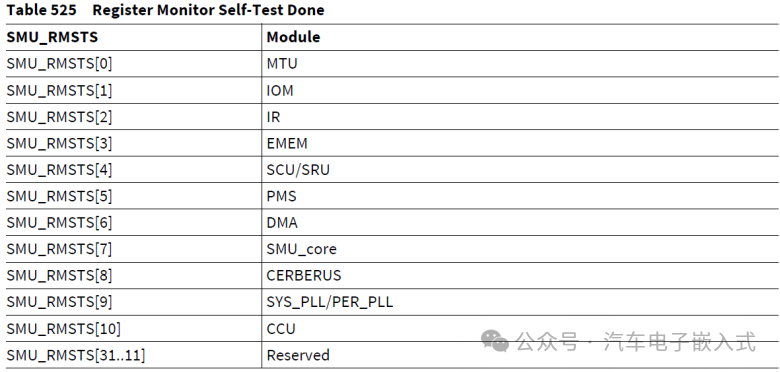

RMSTS.STS [31:0]

-RMSTS.STS[i] 在安全触发自检序列结束时设置为 1 (参见表 525)

安全触发器自检条件

为了防止自检期间出现意外行为,应满足以下条件:

必须启用要测试的模块的时钟

自检期间不得修改自检所涉及模块的时钟和时钟比率

自检序列中所涉及模块的时钟比率应以特定方式设置。有关更多详细信息,请参阅安全触发相关章节

执行自检时,微控制器不应设置为重置,休眠或调试状态

2.1.2.5 SMU_core到SMU_stdby的接口

如果发生故障, SMU_CORE 会向 SMU_Stdby 生成信号 SMU_core_alive。

如果满足以下条件之一,将生成 SMU_core_alive 信号:

当 SMU_CORE 处于运行(RUN)或故障(FAULT)状态,且 SMU_CORE 活动监视器 (SCAM) 检测到 SMU_CORE 未生成反应时,会发生警报事件。

当 SMU_CORE 处于启动(START)状态,且SCAM检测到 SMU_CORE 未生成响应时,会发生监视程序或恢复计时器警报事件。

发送 SMU_ActivateFSP 或 SMU_ActivatePES 命令,但 SMU_CORE 不会生成相应的响应

在处理此报警时,报警的配置会发生变化

SMU_core_alive 信号可以通过发送 SMU_AliveTest 命令来测试。

事实上,发送 SMU_AliveTest 命令将触发SCAM引发故障并将 SMU_core_alive 警报转发给 SMU_Stdby。无论是否启用 SMU_Stdby (请参阅Interdependency Between SMU_core and SMU_stdby) ,都可以在 AG2i_STDBY (i=1) 中读取 SMU_core_Alive 报警标志。可以通过使用不同的参数发送 SMU_AliveTest 命令来禁用SCAM错误注入 (请参阅表 531)。但是,当真正的故障生成 SMU_core_alive 报警时, SMU_AliveTest 命令无法清除该报警。要清除 SMU_core_alive 警报,至少需要重置应用程序。

对于 TC39xB 和 TC38x ,当 SMU_CORE 处于启动(START)状态时,在处理“恢复计时器 1 ”超时警报时发生故障将不会生成 SMU_core_alive 警报。

2.1.3 SMU_core集成指导

本章通过提供有关错误针脚 (故障信号协议 (FSP)) 与微控制器的其他输入 / 输出 (GPIO) 功能以及故障信号协议 (FSP) 配置的更多信息,扩展了接口概述部分。

在power-on reset期间, ErrorPin 处于高阻态:the pull devices are disabled.

power-on reset后, ErrorPin 连接到的端口(PORT)的默认模式为 GPIO.

在将 PAD 的所有权更改为 SMU 之前,软件应配置端口寄存器,包括:

如果未使用 GPIO ,请disable the pull devices.

通过软件编程GPIO 寄存器,将 ErrorPin强驱动输出低电平.

设置P33_PCSR.SEL8为1

设置P33_PCSR.SEL10为0.

要使 SMU 能够控制 ErrorPin PAD ,软件应激活 PAD 配置保护处理(configuration safeguarding process)。

-保护处理需要一个软件操作,包括在 PCTL.PCS 字段中写入 1。只有从 0 到 1 的第一个上升沿会使得保护处理生效。新的端口配置以及从 0 到 1 的 PCTL.PCS 的新转换对硬件没有影响。

此外,需要按照以下步骤重新配置故障信号协议 (FSP) 设置:

-当处于无故障状态(Fault Free State)且正在使用时间切换(Time Switching)或Dual Rail协议(时:

通过将 FSP 设置为Bi-stable协议模式 (FSP.MODE = 00B) 来禁用时间切换(Time Switching)或Dual Rail协议

等待Bi-stable协议模式激活 (读取FSP寄存器 两次)

写入想写入的值到PRE1, PRE2或者TFSP_HIGH.

切换FSP.MODE到想要的协议

当处于无故障状态且正在使用Bi-stable协议时:

写入想写入的值到PRE1, PRE2或者TFSP_HIGH.

切换FSP.MODE到想要的协议

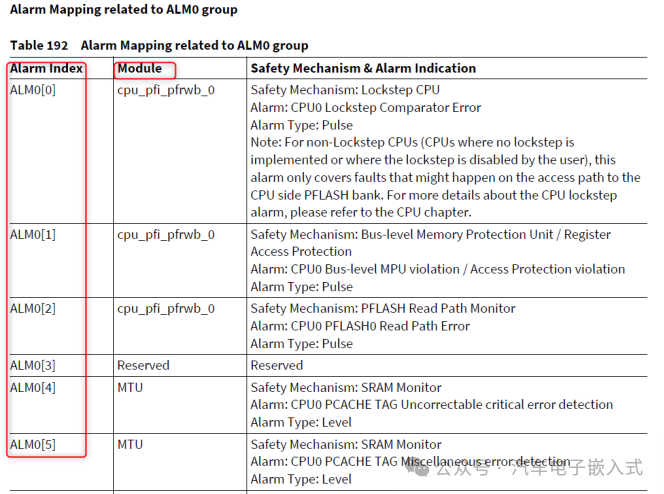

2.1.4 报警映射(Alarm Mapping)

其他外设模块产生的Alarm都几种映射到SMU模块。为此,定义了报警组。报警组索引 ALM< n >[index] 信号与报警配置和状态寄存器 (AG< n >[index]) 之间存在一对一关系。一个组由多达 32 个警报组成。

TC37x模块拥有Alarm Group 0-11, Group 20, Group 21共14组Alarm, 每组Group有32个Alarm.

2.1.4.1 SMU_core内部Alarms

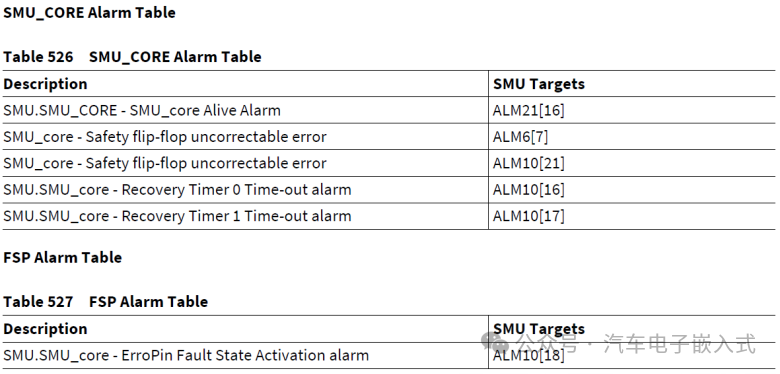

下表描述了 SMU_CORE 生成的警报。

2.1.5 Alarm处理

2.1.5.1 Alarm协议

每个安全机制都应使用预定义的协议与 SMU_CORE 连接。该协议允许以可靠的方式跨越时钟域。协议的操作对软件层没有影响。

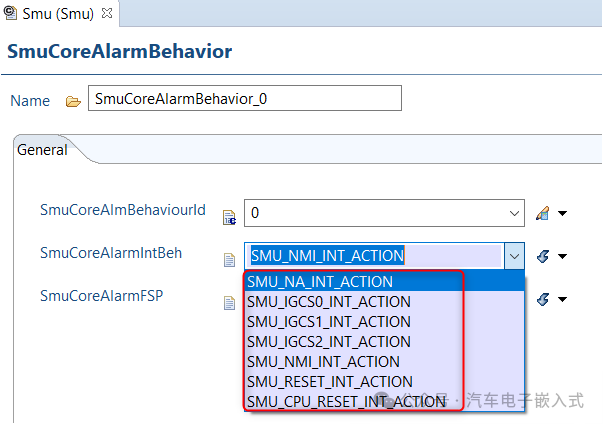

2.1.5.2 Alarm配置

收到报警事件后, SMU_CORE 会对要执行的操作进行解码。该操作可以分为内部行为和外部行为。可以为每个报警配置内部和外部行为。

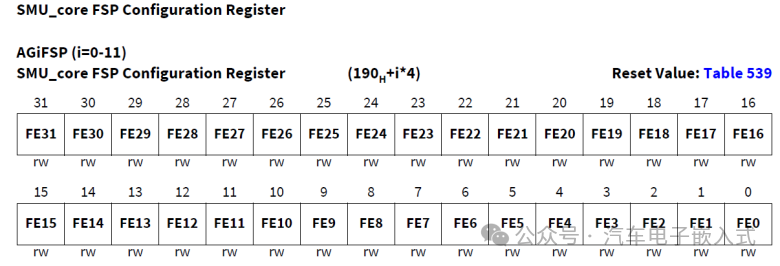

外部行为与故障信号协议相关 (请参阅故障信号协议 (FSP))。外部行为通过以下寄存器配置:

AGiFSP (i=0-11)

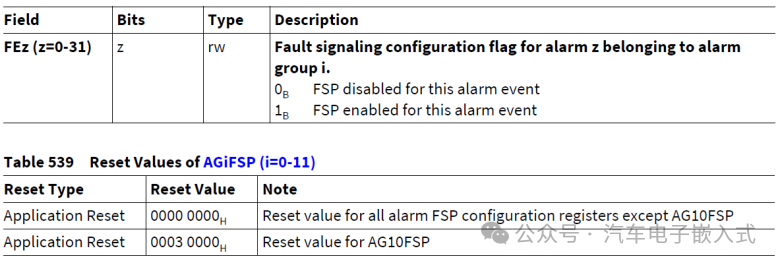

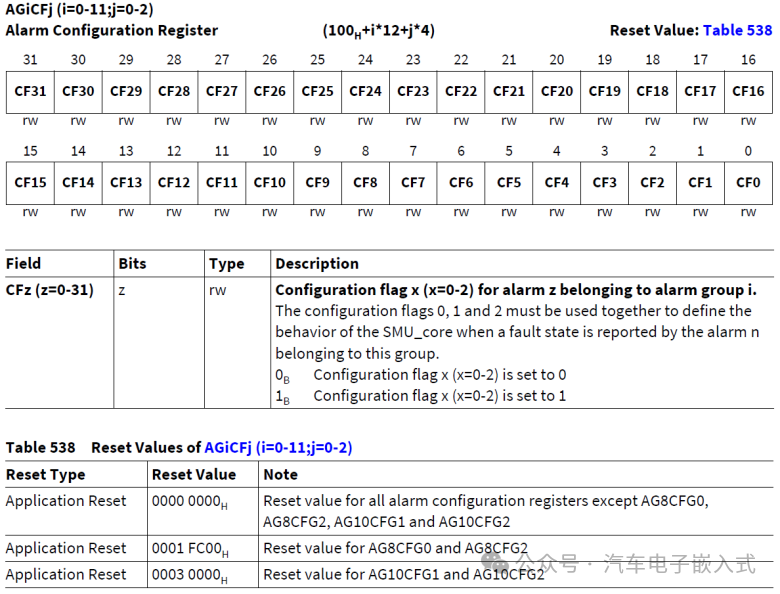

SMU 在出现报警时的内部行为通过以下寄存器进行控制:

AGiCFj (i=0-11;j=0-2)

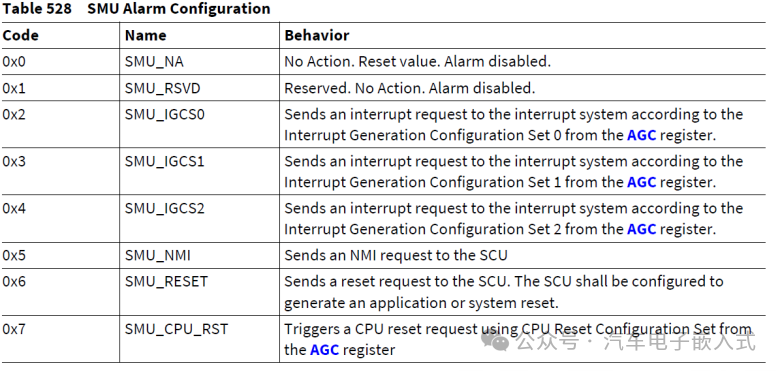

内部行为由 3 位代码指定,如下所示:

Code = SMU_AGCF2. SMU_AGCF1. SMU_AGCF0, n=0...11

三个bit组成0x0 – 0x7共8种组合。

2.1.5.3 Alarm操作

每当检测到输入报警事件且 SMU_CORE 状态机器处于运行(RUN)或故障(FAULT)状态时, SMU 会同时检查要为内部操作和 FSP 执行的相应操作。如果检测到输入报警事件,但未指定报警的操作,则相应的状态位也应设置为 1 ,但不会发生任何操作。

传入报警事件的处理过程如下所示:

同时扫描所有报警组(Alarm Group)和每个报警。

挂起的报警(Alarm)的执行是同时进行的。

报警组内的报警处理可能需要几个 fSPB 周期。

如果完成了故障处理,则会在 SMU_AEX 寄存器中设置相应的位。只要设置了位,相应的故障处理就会被阻止。故障处理完成后,此位需要由 SW 重置。

如果SMU_AEX寄存器中与挂起报警相关的报警执行位已设置,则报警事件被忽略,但状态位和相应的报警错过事件位已设置。

如果与报警事件相关的状态标志已设置为1,则报警事件将被忽略。

无论何时处理报警事件,AG寄存器中的硬件都会将相应的状态位设置为1。如果配置并执行了内部SMU_core动作,则AFCNT寄存器中的动作计数器(ACNT)递增。

2.1.5.4 Alarm状态寄存器

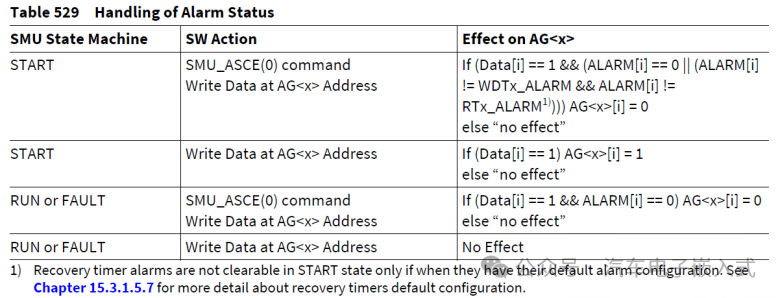

表529规定了根据SMU_core状态机状态在AG报警组状态寄存器上可能的软件操作。

在START状态下,软件可以通过在AG地址写入来“模拟”输入报警事件的发生。如有必要,软件应读回AG寄存器,以确保操作完成。此外,在清除警报后,软件应重新检查警报状态位(针对清除时间窗口期间发生的警报)。

要清除各个报警标志,请仅使用32位写入。

2.1.5.5 Alarm诊断寄存器

报警诊断寄存器使应用程序能够改进对导致故障的根本原因的诊断。在这种情况下,如果应用程序允许,它们可能有助于实施恢复策略。当出现以下情况时,SMU_ADx诊断寄存器应生成SMU_AGx寄存器的快照:

当SMU处于RUN(运行)或FAULT(故障)状态时,SMU要执行的动作是复位

发生将SMU_core状态机(SSMSSM)切换到FAULT状态(RUN->FAULT,FAULT->FAULT)的条件,由SMU硬件或软件命令控制

SMU_ADx寄存器只有在power-on reset后才会被清除。

注:在触发SMU对SMU_AGx寄存器进行快照的每个条件之后,SMU_ADx诊断寄存器将被当前SMU_AGx寄存器值覆盖。如果SMU已经处于FAULT(故障)状态,并且FSP再次激活,则这也是有效的。

2.1.5.6 Port紧急停止

Port紧急停止功能可强制Pad进入通用输入模式(General Purpose Input Mode)。SCU的端口紧急停止请求可通过以下任何情况激活:

SMU_ActivatePES()软件命令。

SMU_AG< x >FSP 启用且 FSP 启用的报警事件。

在 SMU_AGCFX 寄存器中配置了内部操作且为该操作启用了 SMU_AGC.PES 的警报事件。

2.1.5.7 Recovery Timer

恢复计时器 (RT) 可用于监控通过警报, NMI 或中断操作激活的持续时间或内部错误处理程序。 在当前 SMU_CORE 实现中有两个独立实例 (RT0 和 RT1) 可用。恢复计时器持续时间 (所有实例相同) 在寄存器 RTC 中配置。可以启用或禁用每个实例,但默认情况下,这两个实例都已启用,因为操作 CPU 监视程序时需要使用它们 (另请参阅Watchdog Alarms)。除了 RTC 之外,每个恢复计时器实例还可以使用附加配置寄存器 (RTC00 , RTC01 , RTC10 和 RTC11) 来配置警报映射。

警报映射由一对参数 {GIDi, ALIDi} (i = 0..3) 组成,其中 GIDi 是组标识符,而 ALIDi 是属于组的警报标识符。每个恢复计时器实例可以配置四个 { GIDi , ALIDi } 对。可以多次配置相同的组标识符。如果需要将少于四个报警映射到恢复计时器,则应多次配置相同的 {GIDi, ALIDi}。

注:只有当内部操作是中断或 NMI 时,才可以使用恢复计时器。然而,没有进行硬件检查,而是由软件以适当的方式配置SMU_core.

如果已启用恢复计时器,并且任何 { GIDi , ALIDi } 对都将发生警报事件,并且配置了内部操作导致内部操作 (警报状态应清除) ,则恢复计时器将由硬件自动启动。这种情况称为恢复计时器事件。无内部操作的报警不应启动恢复计时器。

一旦发生恢复计时器事件,恢复计时器将启动并计数,直到软件使用 SMU_RTStop() 停止它。如果计时器超时,将发出内部 SMU 报警 (恢复计时器超时)。在恢复计时器运行期间,请求恢复计时器的任何其他操作都将被忽略。如果发生此类事件, STS 寄存器中的硬件将位 RTME (恢复计时器未接来电事件) 设置为 ‘1 ’。RTME bit 只能通过软件清除。在恢复计时器运行期间, STS 寄存器中的硬件将 RTS bit (恢复计时器状态) 设置为 ‘1 ’:从计时器激活到收到 SMU_RTStop() 或计时器过期。收到 SMU_RTStop() 或计时器到期时,硬件将清除该位 RTS。

如果在恢复计时器未处于活动状态时收到 SMU_RTStop() 命令,该命令将返回错误响应。

注:如果应写入 RTC.RTD ,请确保没有运行恢复计时器 (恢复计时器状态由 STS 寄存器中的 BITS RTS0 和 RTS1 指示)。

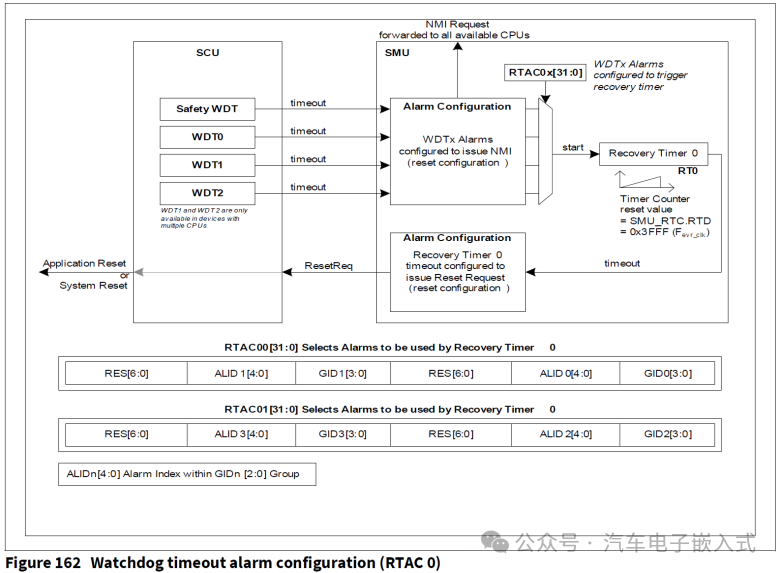

2.1.5.8 看门狗Alarms

如果看门狗 (WDT) 不是由软件或固件提供服务,则需要对监视狗 (WDT) 超时警报进行特殊处理,以确保微控制器行为正确。应确保微控制器在预警阶段后重置,在此阶段,软件仍可以执行一些关键操作。

每个超时警报都应激活 NMI

恢复计时器 0 应配置为为安全 WDT , CPU0 WDT , CPU1 WDT 和 CPU2 WDT 的 WDT 超时警报提供服务

恢复计时器 1 应配置为为维修 CPU3 WDT 的 WDT 超时警报, CPU4 WDT 和 CPU5 WDT

应将恢复计时器 0 和恢复计时器 1 超时警报配置为发出重置请求并激活故障信号协议。

上述属性作为监视程序超时警报以及恢复计时器 0 和 1 的重置值实现。

图中仅显示 RTAC 0 和相关的四个 WDT 的示例。同样, RTAC 1 与相关 WDT3 , WDT4 和 WDT5 的设置方式也是如此。

由于也需要从 CPU 执行的第一个指令中检测看门狗超时, SMU 应在启动状态期间处理任何看门狗超时警报。

注:如果所有 WDT 警报都需要相同的行为,建议使用实施逻辑或所有 WDT 超时警报的全局 WDT 超时警报,从而释放 RTC00 , RTC01 , RTC10 和 RTC11 中的某些 {GIDi , ALIDi } 配置对,以用于其他用途。

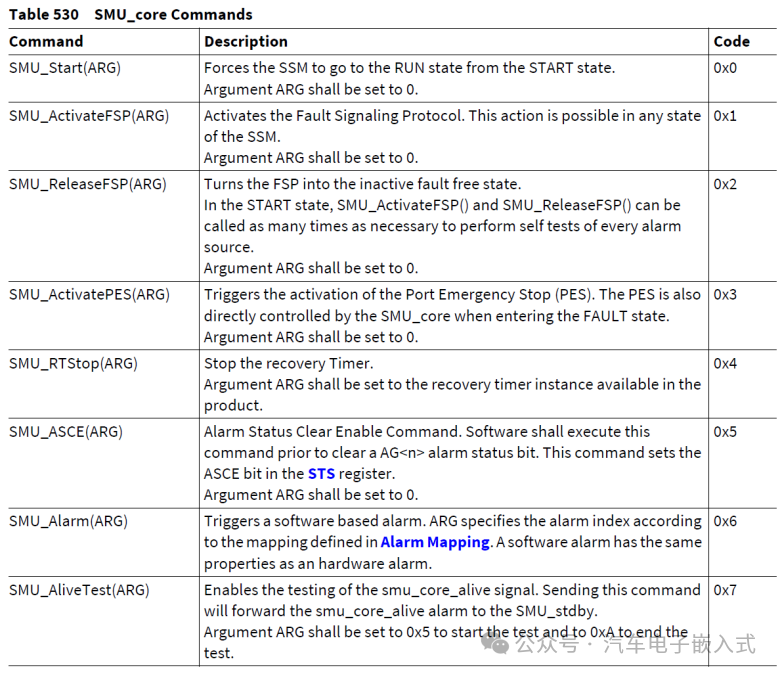

2.1.6 SMU_core控制接口

通过控制接口引入SMU_CORE 的核心功能。控制接口定义了软件如何控制 SMU_CORE ,如表 530 所示。控制接口直接连接到 SMU_CORE 状态机 (SSM) 中所述的 SMU_CORE 状态机 (SSM) 操作和故障信号协议 (FSP) 中所述的故障信号协议 (FSP)。控制接口由 CMD 寄存器使用 CMD 和 ARG 字段实现。命令完成状态可通过 STS 寄存器获取。

注:如果参数不符合命令规范,则该命令将被忽略并返回错误代码。

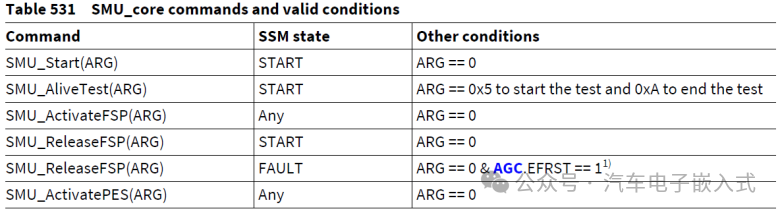

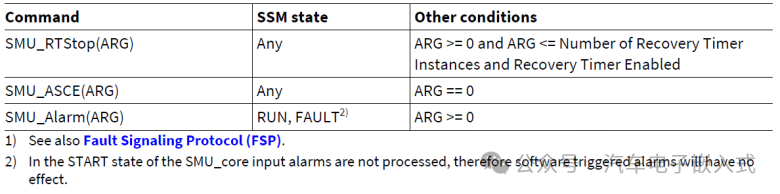

下表提供了执行命令的合法条件。 条件取决于 SMU_CORE 状态机器 (SSM) 状态 (参见 SMU_CORE 状态机器)。任何未指定的情况都会导致错误代码。

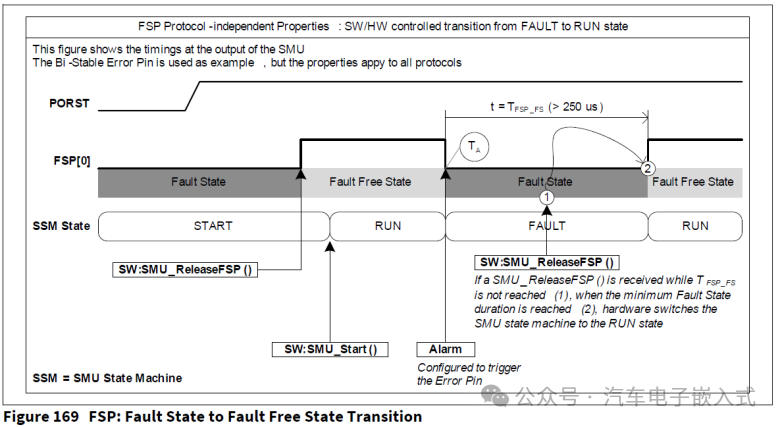

2.1.7 SMU_core 状态机

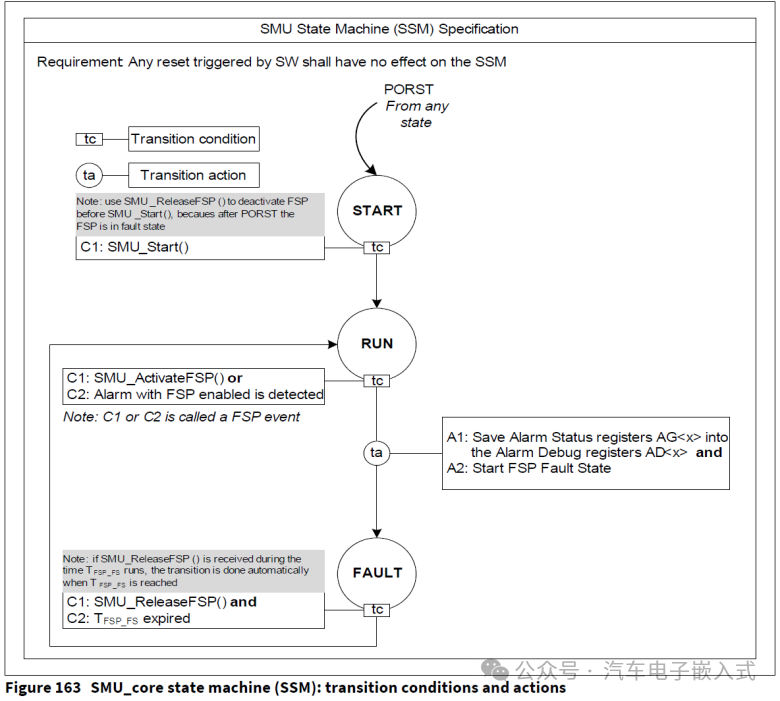

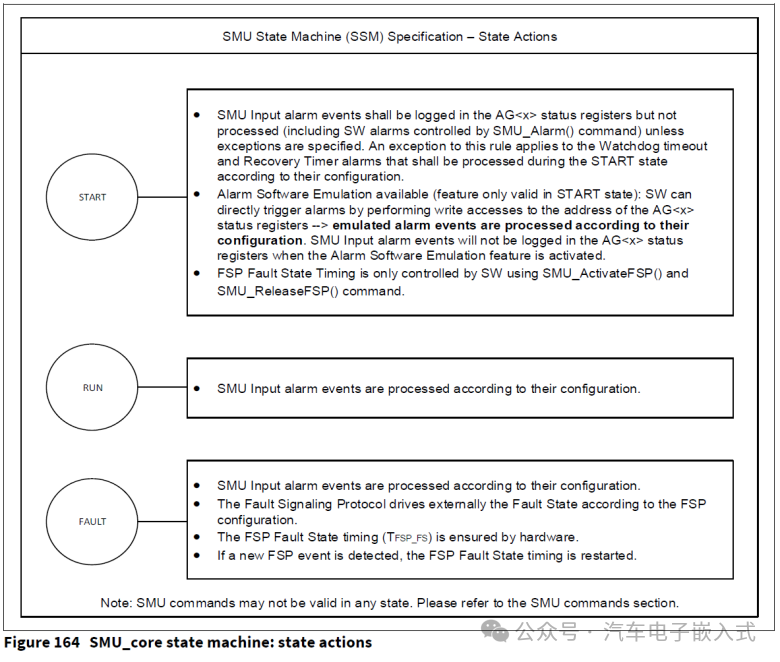

图 163 和图 164 描述了 SMU_CORE 状态机 (SSM) 的行为。

Fault Counter

SMU 实现了一个故障计数器 (AFCNT) ,该计数计数了从运行状态到故障状态的转换次数。故障计数器寄存器只能通过热启动重置来重置。

2.1.8 故障信号协议 (Fault Signaling Protocol, FSP)

故障信号协议使微控制器能够向外部安全控制器设备报告紧急情况,以控制安全系统的安全状态。

2.1.8.1 简介

故障信号协议通过 FSP 命令寄存器进行配置。FSP 状态由 STS 寄存器中的 FSP 标志指示。FSP有三种状态:

开机重置状态。在热启动重置(warm power-on reset)后, SMU 与端口断开连接 (请参阅 SMU_CORE Integration Guidelines)。在热启动重置后, SMU FSP 输出应为故障状态。

无故障状态。无故障状态由一个定时器控制,定时器被称为 TFSP_FFS ,并由 FSP 寄存器控制。

故障状态。故障状态的时间由 FSP 寄存器控制。最小活动故障状态时间称为 TFSP_FS。

无故障和故障状态行为可以使用以下协议进行配置:

Bi-stable protocol (default)

Dynamic dual-rail protocol

Time-switching protocol

FSP 可通过以下方式控制:

软件方式,通过CMD寄存器使用SMU_ActivateFSP()和SMU_ReleaseFSP()命令。

硬件方式,通过AGiFSP(I = 0-11)配置寄存器。

为避免意外报警,仅当 SMU 未处于故障状态且 FSP 处于双稳定协议模式 (FSP 模式 = 00B) 时,才可执行 PRE1 , PRE2 或 TFSP_HIGH 字段的配置。模式切换和配置不应使用相同的写入访问权限来注册 FSP。如果应写入 FSP.PRE1字段,请确保没有运行恢复计时器 (恢复计时器状态由 STS 寄存器中的 BITS RTS0 和 RTS1 指示)。

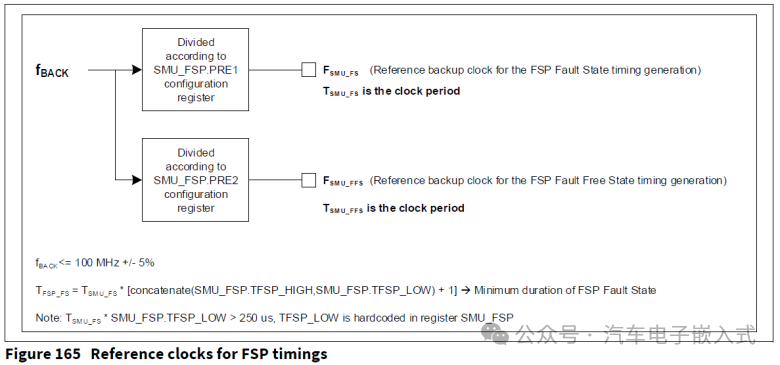

图 165 指定了生成 TFSP_FFS 和 TFSP_FS 计时的中间时钟。

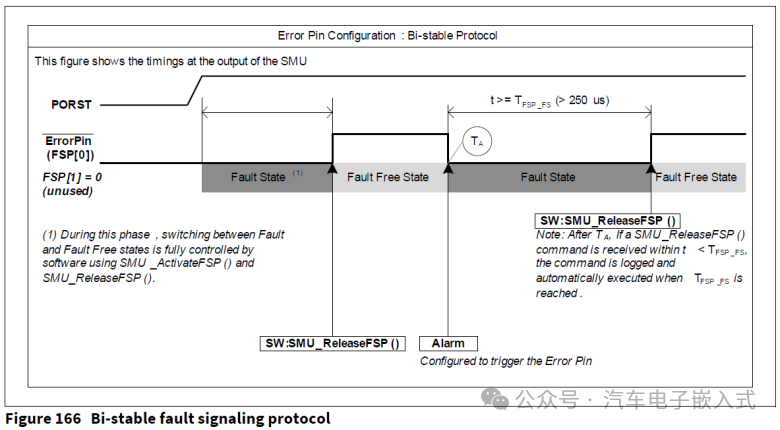

2.1.8.2 Bi-stable fault signaling protocol

操作

在通电重置过程中, FSP[0] =0 (故障状态)。

通电后重置 FSP[0] 保持故障状态。

FSP[0] 必须设置为每个软件的无故障状态 (SMU_ReleaseFSP ())。

在检测到配置为激活 FSP 的报警事件时, FSP [0] 会进入故障状态并保持此状态,直到收到 SMU_ReleaseFSP () 命令,并且满足 TFS_FS 或发生开机重置。

在故障状态下,如果收到配置为激活 FSP 的新警报事件,但尚未达到 TFSP_FS ,则应重新启动 TFSP_FS 计时。

在故障状态下,如果收到配置为激活 FSP 的新报警事件,并且已经达到 TFSP_FS ,则应启动 TFSP_FS 计时。

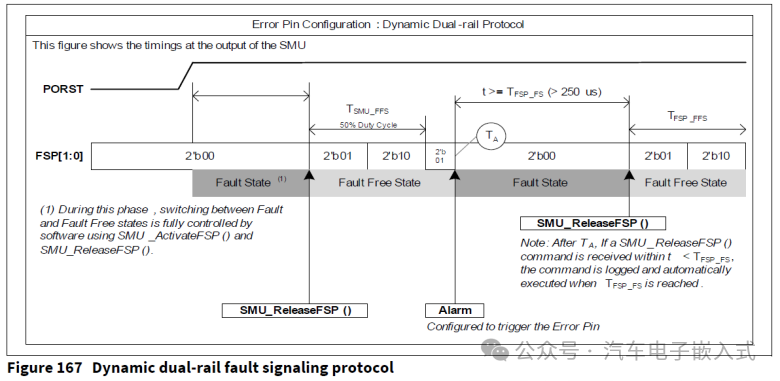

2.1.8.3 Timed dual rail

操作

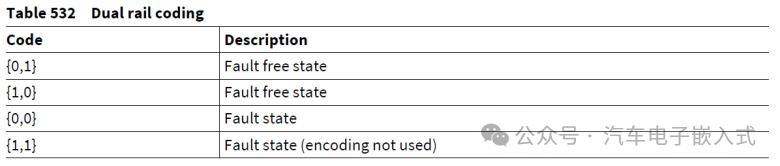

双轨编码是对位进行编码的另一种方法。 双轨代码使用两个信号来定义逻辑状态。

在通电重置过程中, FSP[1:0]=2'B00 (故障状态) •通电重置后, FSP[1:0] 保持故障状态。

FSP[1:0] 必须设置为每个软件的无故障状态 (SMU_ReleaseFSP ())。

故障无状态由 FSP[1:0] 在 2'B01 和 2'B10 之间振荡定义,其定义频率通过 FSP 寄存器配置,占空比为 50% (参见图 167)。

在检测到配置为激活 FSP 的报警事件时, FSP [1:0] 会立即进入故障状态,并保持此状态,直到收到 SMU_ReleaseFSP () 命令且 TFS_FS 满足或启动

重置发生。

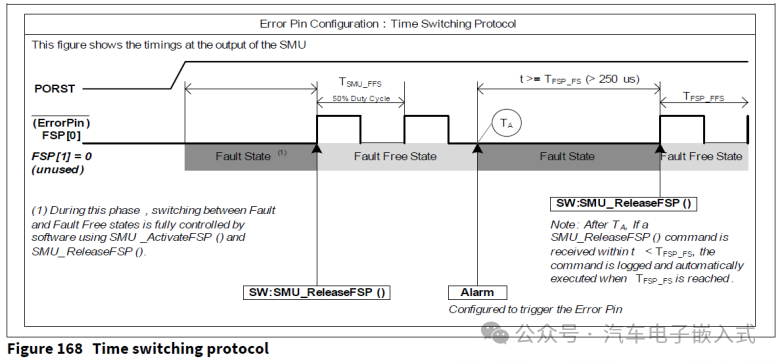

2.1.8.4 Time switching protocol

使用定义的频率在逻辑级别 0 和逻辑级别 1 之间切换 FP[0]。当 SMU_CORE 进入故障状态时,将违反此频率调制协议。

在通电重置过程中, FSP[0] =0 (故障状态)。

加电后重置 FSP[0] 保持故障状态。

FSP[0] 必须设置为每个软件的无故障状态 (SMU_ReleaseFSP ())。

在无故障状态下,使用通过 FSP 寄存器配置的频率, FSP[0] 在逻辑级别 0 和逻辑级别 1 之间振荡 (参见图 168)。

在检测到配置为激活 FSP 的报警事件时, FSP [0] 会立即进入故障状态,并保持此状态,直到收到 SMU_ReleaseFSP () 命令且 TFS_FS 满足或启动要求重置发生。

2.1.8.5 FSP Fault State

当警报配置为激活 FSP 时, SMU_CORE 会自动切换到故障状态。在此期间,安全相关软件还可以尝试分析根本原因 (当微控制器仍在运行时) ,并确定错误的严重程度。由于 FSP 至少对 TFSP_FS 处于活动状态,因此可以确保通过独立于微控制器的外部机制 (除了 FSP 本身) 输入系统的安全状态。在 TFSP_FS FSP 处于故障状态期间,软件可能已断定故障不严重,并决定发SMU_ReleaseFSP () 命令,通知 SMU_CORE 它可以返回到运行状态 (软件错误处理程序的运行时间与 TFSP_FS 的持续时间没有直接关联,在实践中应该要短得多)。

应谨慎使用此功能,当 SMU 报告的故障被评估为不严重时,强烈建议重置微控制器以重新启动安全功能的操作。因此,默认情况下,此功能处于禁用状态,应使用 AGC 寄存器中的 EFRST (启用故障到运行状态转换) 字段进行配置。

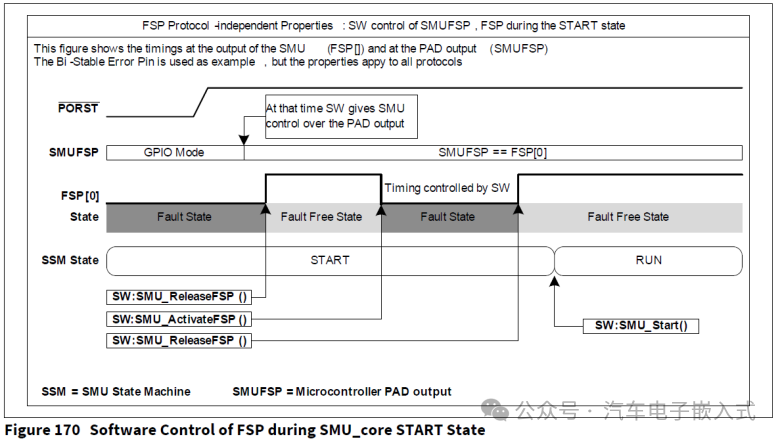

2.1.8.6 FSP and SMU_core START State

图 170 显示了一个典型的使用案例,其中 FSP 在故障状态和无故障状态之间的转换由软件使用 SMU_ReleaseFSP() 和 SMU_ActivateFSP() 命令进行控制。

使用条件:

软件应确保 FSP 处于无故障状态,然后使用 SMU_Start() 命令输入运行状态。

2.2 SMU_stdby

概念和SMU_core基本一样,参考芯片手册。

03

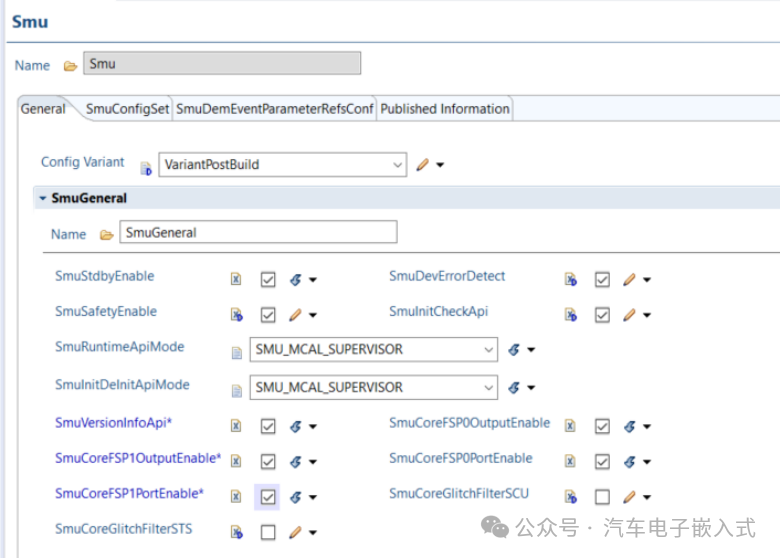

SMU配置

和其他硬件模块一样,理解了模块的原理和基本概念后,模块配置就是按照项目的需求配置模块相关的寄存器,只不过提供了图形化的配置工具。

3.1 SMU General配置

SMU General主要配置一些全局的属性,以及是否使能一些SMU的功能,是否要使能一些API.

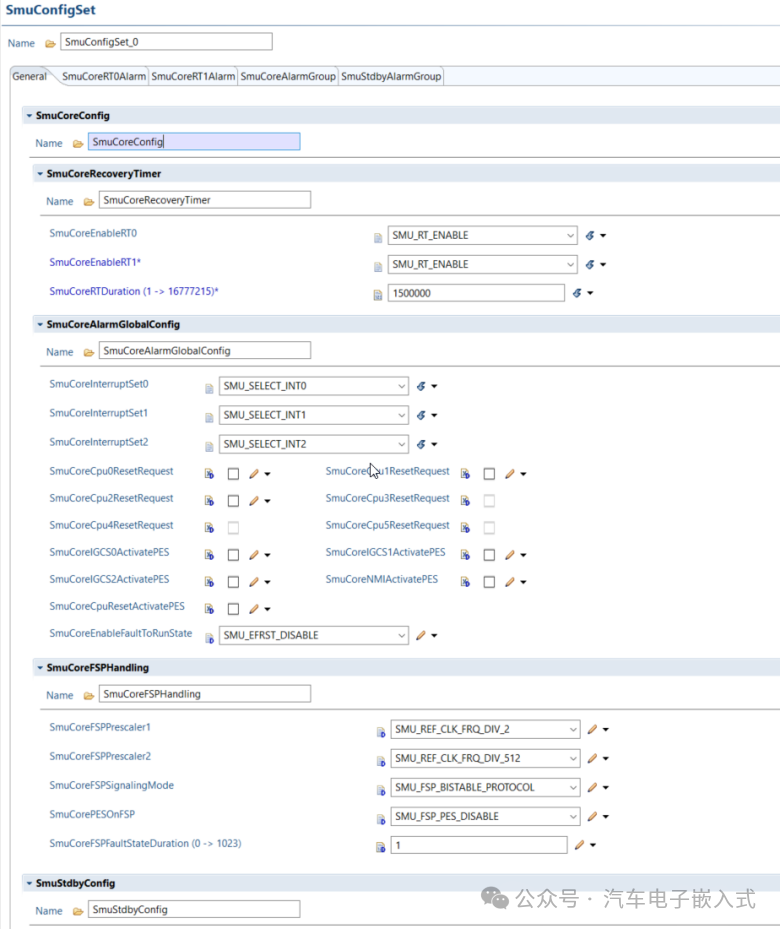

3.2 SmuConfigSet配置

3.2.1 General

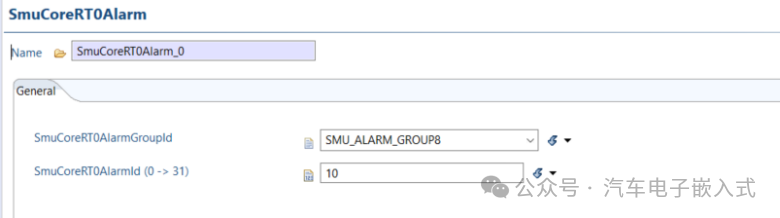

3.2.2 SmuCoreRT0Alarm

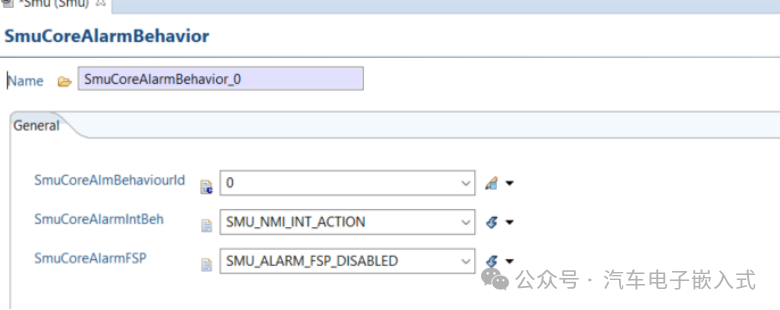

3.2.3 SmuCoreAlarmGroup

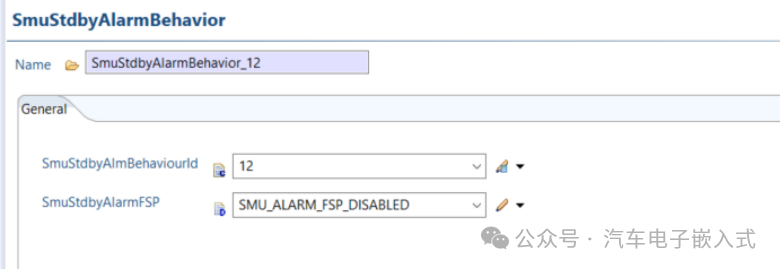

3.2.3 SmuStdbyAlarmGroup

04

总结

SMU模块是Aurix芯片自带的一个功能安全硬件模块,它能够收集其他模块(PMS, MTU, SCU, CCU, e.g.)由于硬件功能安全机制产生的报警(Alarm),然后,SMU模块通过用户配置能够产生内部或者外部的动作/响应,也可以不产生任何动作。对于使用SMU的用户而言,外部响应一般都很少使用,主要就是查对应芯片手册,知道哪一个硬件模块可以产生一个对应SMU的Alarm,然后配置该Alarm产生后需要执行的动作即可。

审核编辑:黄飞

-

AURIX™ TC3xx 电机控制电源板:设计解析与特性洞察2025-12-21 736

-

英飞凌AURIX™ TC3xx安全应用套件快速上手2025-12-19 819

-

两片TC3XX芯片之间的时钟同步可以实现吗?2025-08-04 1611

-

请问tc3xx如何配置多个dedicatedRxBuffersNumber?2025-04-21 2554

-

TC3XX系列IOM模块ECMSELR寄存器中的CTS和CES有什么区别?2024-05-29 624

-

深入解析TC3xx芯片中的SMU模块应用2024-03-01 3942

-

TC3xx系列是否支持RTC功能?2024-02-02 557

-

英飞凌TC3xx系列安全管理单元的使用2023-12-07 4827

-

TC3xx芯片时钟系统的锁相环PLL详解2023-12-01 5152

-

TC3xx芯片的Endinit功能详解2023-11-27 4552

-

英飞凌TC3XX系列多核MCU学习笔记(1)2023-09-19 4964

-

TC3xx芯片DMU介绍2023-08-31 4014

-

AURIX™ TC3xx NVM是非易失性存储器学习笔记2023-06-19 12971

-

AUTOSAR MCAL-基于Infineon TC3xx芯片的ADC模块2023-01-29 12410

全部0条评论

快来发表一下你的评论吧 !