基于嵌入式RISC-V处理器核轻松实现DSP扩展设计

描述

→ Codasip Studio and RISC-V 处理器核

从标准处理器核开始,无需“冷启动”

• 基于已开发的嵌入式或应用处理器核 (如L31等)

• 高质量水准,达量产标准

• 完全符合RISC-V规范

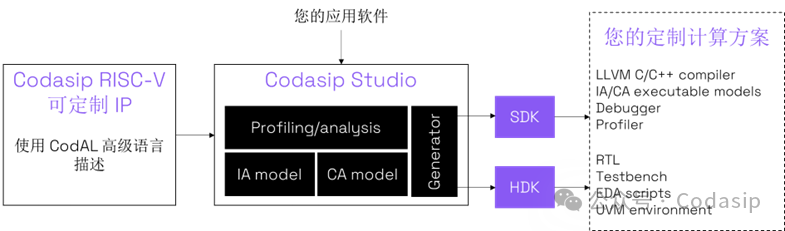

通过Codasip Studio实现您需要的差异化

• 可配置/可定制

• 使用CodAL体系结构描述语言(类C高级语言)

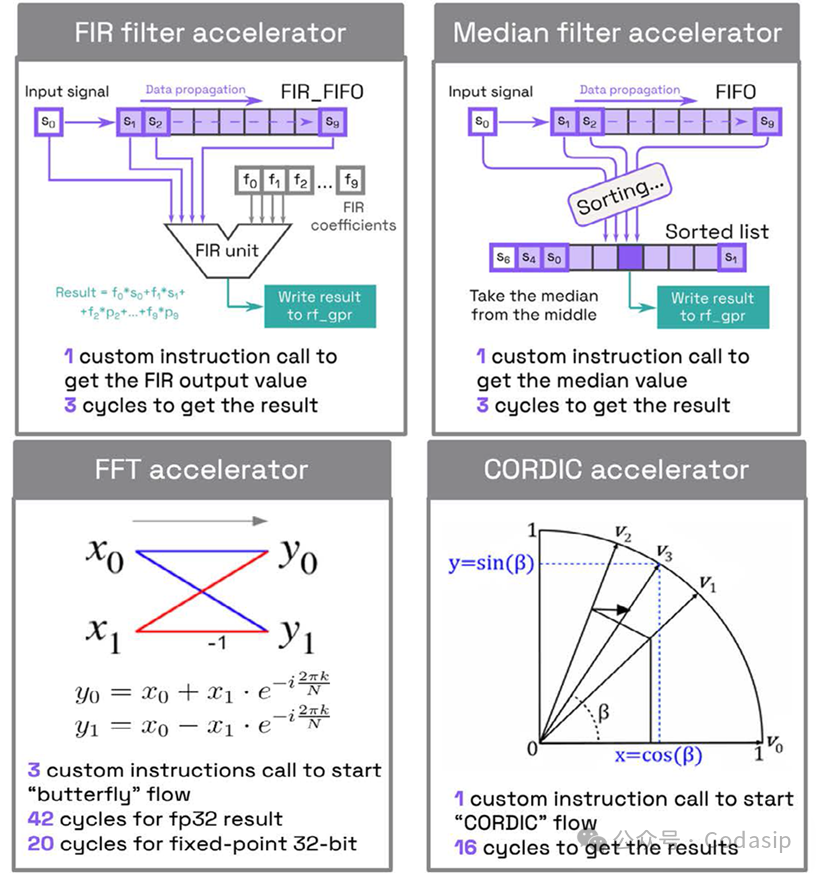

→ 用CodAL实现DSP加速器

→ DSP定制如何影响PPA

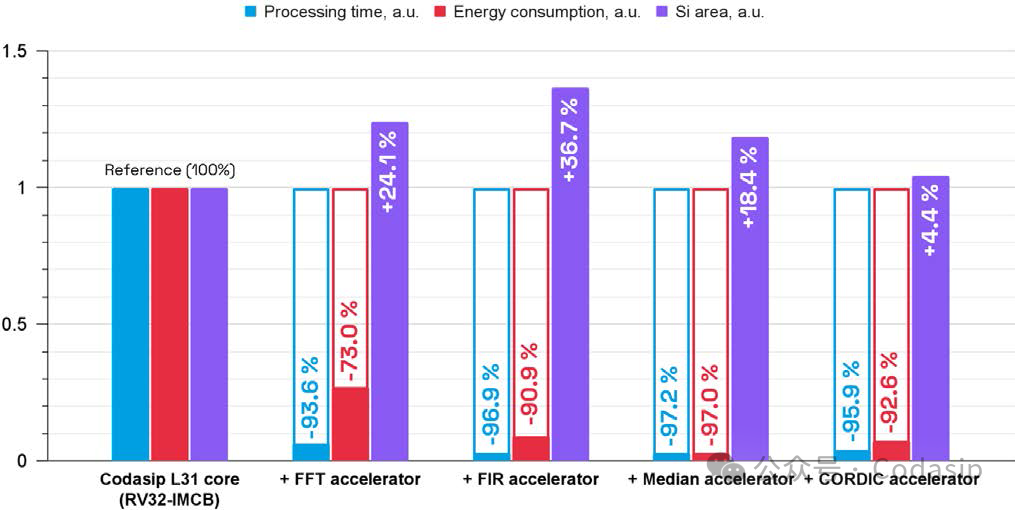

基于嵌入式RISC-V核定制专用DSP,以处理如上四种代表性的DSP算法为例。性能和能耗分别提升和缩减为14.4倍和0.27倍(FFT),14.4倍和0.1倍(FIR)、30倍和0.03倍(Median filtering)和24.3倍和0.08倍(Cordic),通过增加有限的面积即得到了此效果。

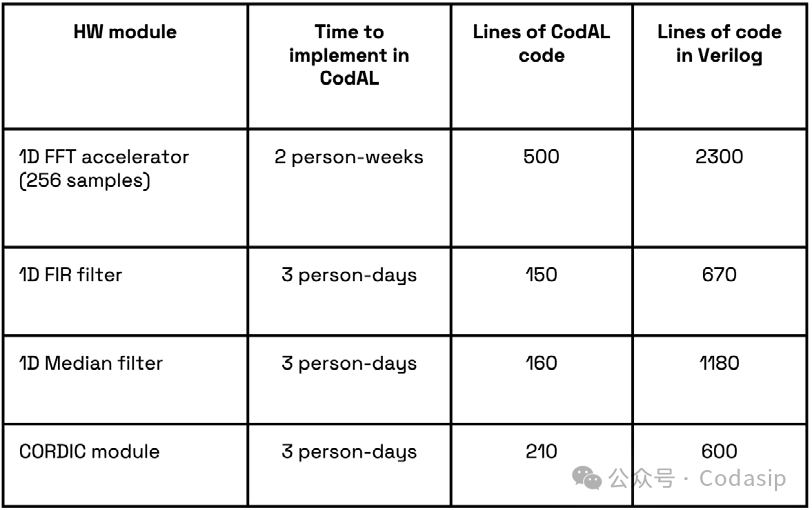

使用CodAL和Codasip Studio,通过“开箱即用”的SDK和HDK等自动生成工具,结合精练的内核描述,轻松实现RISC-V的定制,缩短产品开发周期。下表列出了实现上述的DSP定制的预估代码量和工作量。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

risc-v与esp32架构对比分析2024-09-26 1529

-

重磅合作!Quintauris 联手 SiFive,加速 RISC-V 在嵌入式与 AI 领域落地2025-12-18 839

-

学习RISC-V入门 基于RISC-V架构的开源处理器及SoC研究2020-07-27 4366

-

RISC-V开源处理器核介绍2021-07-23 2414

-

RISC-V嵌入式开发的特点有哪些2021-11-08 2363

-

如何入门RISC-V嵌入式2022-01-07 1259

-

嵌入式RISC微处理器核设计研究2012-05-04 729

-

UltraSoC宣布提供业界首款RISC-V嵌入式处理器产品2019-12-05 1282

-

RISC-V嵌入式开发2021-11-03 1699

-

如何保护RISC-V上的嵌入式处理器2022-05-06 2991

-

如何构建RISC-V嵌入式2022-11-23 816

-

专家力荐|《嵌入式系统原理与开发——基于RISC-V和Linux系统》新书发售2024-07-24 2590

-

如何使用 RISC-V 进行嵌入式开发2024-12-11 3822

-

PIC64GX1000 RISC-V MPU:一款面向嵌入式计算的高性能64位多核处理器2025-09-30 1198

-

为什么RISC-V是嵌入式应用的最佳选择2025-11-07 1816

全部0条评论

快来发表一下你的评论吧 !