7系列FPGA中的POST_CRC错误检测与恢复策略

可编程逻辑

描述

注意:本博文介绍了利用 POST_CRC 试错的方法,但总体而言,赛灵思推荐在所有架构上使用 Soft Error Mitigation (SEM) IP。SEM IP 提供了一种可用于测试 SEU 检测与纠正能力的机制并提供了更强大的调试能力。

本博文中讨论的功能仅支持 7 系列器件。

| 功能 | 7系列FPGA | Kintex UltraScale 和 Virtex UltraScale | Kintex UltraScale+ 和 Virtex UltraScale+ |

| Readback CRC/POST_CRC | 是 | 否,使用 SEM IP 替代 | 否,使用 SEM IP 替代 |

赛灵思 FPGA 中循环冗余校验 (CRC) 的不同类型:

1) 一般 CRC 校验

在一般比特流加载过程中,CRC 校验利用 CRC 寄存器进行。该“CRC 寄存器”的描述详见《7 系列 FPGA 配置用户指南》(官网搜索 UG470)。

FPGA 在比特流被加载时计算 CRC 值,然后该值与在比特流加载结束时预期的 CRC 值进行比较。如果两个值匹配,则FPGA 成功加载。

一般情况下默认启用 CRC 校验。比特流属性为 BITSTREAM.GENERAL.CRC,其中有效选项包括“ENABLE”(启用)或“DISABLE”(禁用)。

2) 回读 CRC/POST CRC 校验

POST_CRC 校验在配置 FPGA 之后,设计运行过程进行。

一般情况下,比特流 CRC 校验是一种独立功能,具有其自己的 CRC 校验寄存器。POST_ CRC 校验具有用于存储校验值的不同以上比特流 CRC 的寄存器。

启用 POST_CRC 校验的目的

启用 POST_CRC 校验的目的是检测单粒子翻转 (SEU)。SEU 导致配置存储器中的数位翻转。POST_CRC 可与 FRAME_ECCE2 原语配合使用,以便提供针对此等错误的额外功能和更好的可见性。我们可利用 FRAME_ECCE2 的输出监控错误检查和纠正 (ECC) 和回读 CRC 电路的状态。

如需了解更多有关 FRAME_ECCE2 原语的详细信息,请参阅《Vivado Design Suite 7 系列 FPGA 和 Zynq-7000 SoC 库指南》(官网搜索 UG953)。

用户通常想要测试这种崩溃发生时的实例,以便确保此等错误被成功检测到。测试插入错误的一种方法是编辑 PRE_COMPUTED CRC 值。

测试插入错误的步骤

将以下设置放置在设计 XDC 中:

set_property POST_CRC ENABLE [current_design]

#Enables the Post CRC checking

set_property POST_CRC_SOURCE PRE_COMPUTED [current_design]

#Determines an expected CRC value from the bitstream

set_property POST_CRC_ACTION CONTINUE [current_design]

#Even if a CRC error is detected, continue CRC checking.

#Other options include HALT, CORRECT_AND_CONTINUE and CORRECT_AND_HALT

set_property POST_CRC_INIT_FLAG ENABLE [current_design]

#Leaves the INIT_B pin enabled as a source of the CRC error signal. Useful especially if FRAME_ECC is not used

如需了解更多有关这些设置的详细信息,请参阅《Vivado Design Suite 属性参考指南》(官网搜索 UG912)。

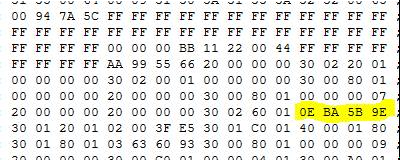

运行设计流程并生成比特流。在生成了比特流之后,PRE_COMPUTED CRC 的值可在 .bit 文件中校验。该值会是非零值。

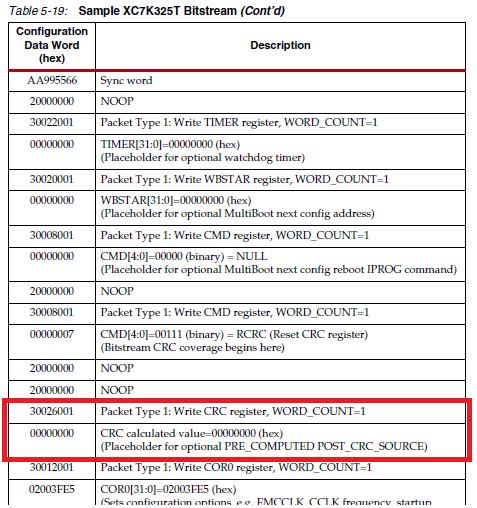

若要确定 PRE_COMPUTED CRC 值在比特流中的哪个位置,可查阅《7 系列 FPGA 配置用户指南》(UG470) 中的示例 7 系列比特流。

若要测试插入错误,您就要禁用一般 CRC 校验,以便让比特流成功载入。切记,如果对位于正常 CRC 覆盖范围内的比特流进行了任何编辑,即会标注 CRC 错误并阻止比特流加载。

若要禁用一般 CRC 校验,您应使用以下设置:

set_property BITSTREAM.GENERAL.CRC DISABLE [current_design]

#Disables the general CRC checking

set_property POST_CRC ENABLE [current_design]

#Enables the Post CRC checking

set_property POST_CRC_SOURCE PRE_COMPUTED [current_design]

#Determines an expected CRC value from the bitstream

set_property POST_CRC_ACTION CONTINUE [current_design]

#Even if a CRC error is detected, continue CRC checking.

#Other options include HALT, CORRECT_AND_CONTINUE and CORRECT_AND_HALT

set_property POST_CRC_INIT_FLAG ENABLE [current_design]

#Leaves the INIT_B pin enabled as a source of the CRC error signal.Useful especially if FRAME_ECC is not used

再次运行设计流程并生成比特流。

在生成比特流之后,您应观察 PRE_COMPUTED CRC 的值是否为零。这是禁用 GENERAL.CRC 的结果,以便进行错误测试。

由于预计有前面的非零值,要配置器件并观察其行为。

INIT_B 引脚的监控应显示 CRC 错误。

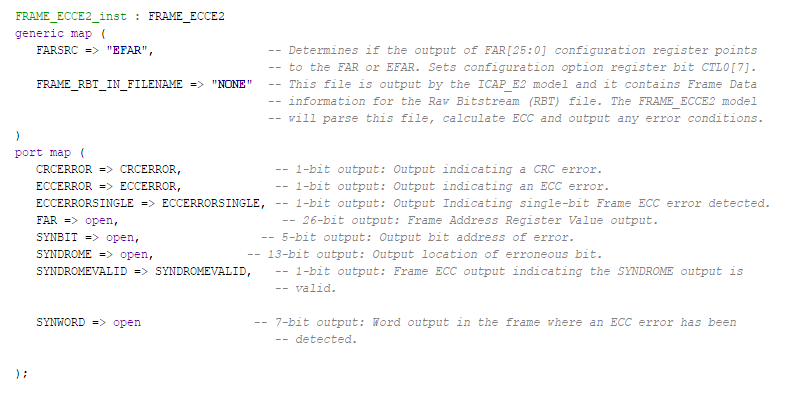

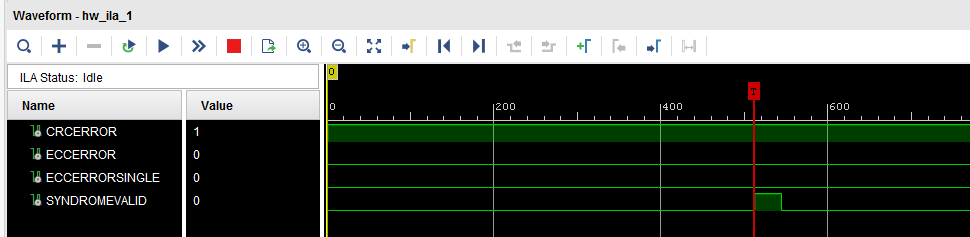

FRAME_ECCE2 也可被用于接收连接到 ILA 上的 FRAME_ECCE2 发出的输出信号。然后它将有可能观察到 CRCERROR。

下文的例化可被用于 FRAME_ECCE2 原语的连接:

然后输出可被传输给 ILA。

当器件被编程后,通过校验 ILA 上的信号,它应有可能查看类似于以下示例的输出。例如,由于未找到预期的非零 PRE_COMPUTED 值,标注了 CRCERROR 错误。

可以理解的是,大部分用户都想要测试错误检测,以确定在此等错误被检测到时,将会以某种形式予以报告。该测试可让用户坚信,在真实的情景中,错误会被正确检测并报告。

如上文所述,由于 SEM IP 所提供的能力,赛灵思推荐使用 SEM IP,而不是 POST_CRC。POST_CRC 的功能在较新的架构中不受支持。

审核编辑:黄飞

-

7 系列 FPGA 帧 ECC 逻辑如何检查配置帧数据的单位或双位错误2017-09-28 8668

-

Micrium全家桶之uC-CRC: 0x02 CRC2023-06-08 2753

-

FPGA中循环冗余校验的不同类型2019-07-29 4958

-

恢复引导加载程序时出现 CRC 错误怎么解决?2026-02-04 308

-

FPGA配置CRC错误2019-05-09 7284

-

POST约束是否意味着回读CRC启用2020-06-10 1087

-

INIT_B与Virtex-5上的POST_CRC启用约束不符合预期的原因?2020-06-16 1182

-

什么是POST上电自检?POST自检是按什么顺序进行检测的?2021-11-02 7304

-

并行CRC在FPGA上的实现研究2011-08-15 625

-

在FPGA上实现CRC算法的程序2016-06-07 1114

-

如何在CAN总线通信过程中进行CRC错误检测2019-07-15 11563

-

CRC算法原理和CRC编码的实现方式与使用Verilog对CRC编码进行描述2019-08-06 2357

-

Xilinx 7 系列FPGA中的Serdes总结2020-12-31 1890

-

fpga报告crc故障是什么意思2024-01-04 3188

-

SRAM中的错误检测2024-09-20 559

全部0条评论

快来发表一下你的评论吧 !