一个高速电路设计中不可忽略的重要因素—趋肤效应

描述

编者注:抛砖引玉:在高速电路设计中,我们常常关注的是芯片的驱动能力、PCB介质的介电常数、介质损耗角、连接器、线缆等等,其实导体(铜)的表面粗糙度的影响也很大,特别是当信号的速率越来越高的时候。所以在高速电路设计中,每一个与电路相关的因素都很重要。

在高速电路设计中,链路中的每一个参数都有可能导致传递的信号出问题。今天就和大家分享一个平常大家不太注意的参数。

先回顾下在中学的时候,咱们学习的一个概念,趋肤效应:当信号的频率越来越高时,信号都会趋向于导体的表面传递。这样就会导致信号流过导体的相对有效面积变小,从电阻的角度来分析,这就会导致电阻增加,导致传递能量的损失。

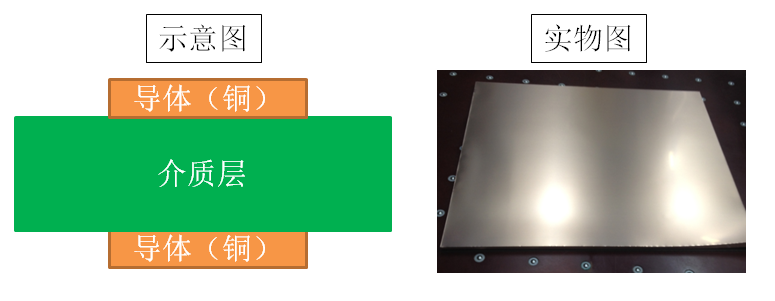

在电子产品使用的PCB,基本都是由铜箔和有机材料组成的,如下图所示:

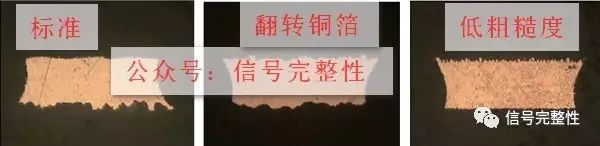

我们平时看到的铜箔,表面上看起来都是非常光滑的,实际上并不如你肉眼所见的那样,铜箔并不是完全光滑的,其在金相显微镜下如下图所示:

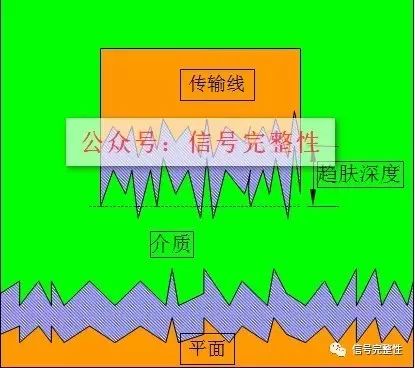

为了更加地容易理解,给大家一个示意图:

铜箔的表面都是有很多铜牙存在的。目前小编没有发现非常官方的数据说明普通的铜牙到底有多长(与厂商有关系),据小编看到的普通的铜箔,没有经过处理的铜牙(铜箔粗糙度)一般都是在20~30um左右。当然,常规的根据铜箔粗糙度的厚度(系数)不同,目前有标准铜箔、反转铜箔、低粗糙度铜箔和超低粗糙度铜箔之分。

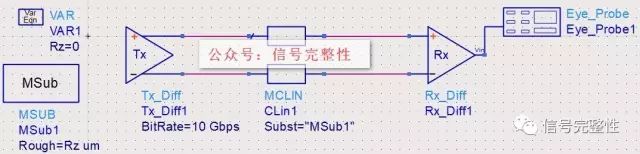

前面说到,铜箔的粗糙度会影响到信号完整性,那么我们就来做一个实验看看。原理图如下所示,把铜箔粗糙度的设置为一个变量,初始值为0,仿真的速率为10Gbps:

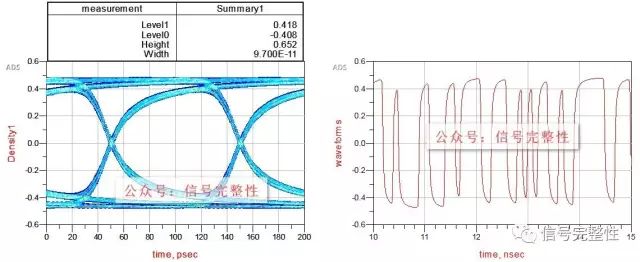

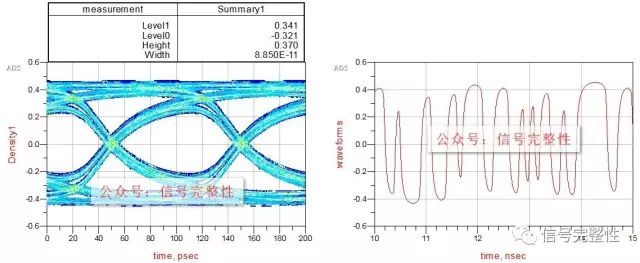

分别查看其眼图和波形,如下所示:

从结果可以看到:眼图的宽度为97ps,高度为0.652V,信号的峰值为0.479V。

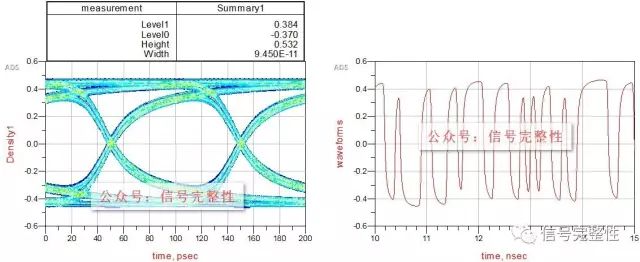

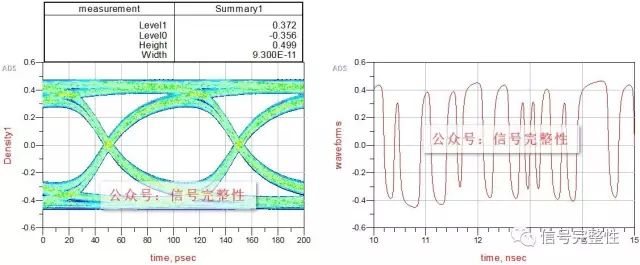

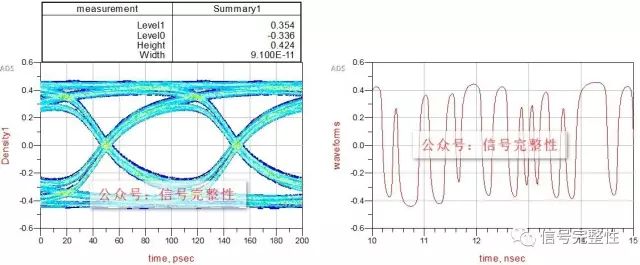

那么,接下来,逐步改变铜箔粗糙度的厚度,观察眼图的变化,分别仿真铜箔粗糙度为5um、10um、15um和20um的情况,眼图和波形分别如下所示:

当粗糙度为5um的时候,眼图的宽度为94.5ps,高度为0.532V。

当粗糙度为10um的时候,眼图的宽度为93ps,高度为0.499V。

当粗糙度为15um的时候,眼图的宽度为91ps,高度为0.424V。

当粗糙度为20um的时候,眼图的宽度为88.5ps,高度为0.370V。

从以上的结果,咱们可以看到当铜箔粗糙度的系数(厚度)增加时,眼图的的margin越来越小,抖动(Jitter)越来越大。

有的工程师经常会问到这样一个问题:当信号的速率为多少的时候,在实际项目工程中需要考虑铜箔粗糙度的影响。我的答案是,任何时候考虑都是必要的。但是综合成本和效果来考虑的话,当信号速率超过5G以上的时候,就应当适当地考虑铜箔的选择问题(如果设计要求不高,也可以不考虑)。

所以,当信号的速率越来越高的时候,我们不仅仅需要关注芯片的驱动能力、PCB介质的介电常数、介质损耗角、连接器、线缆等等,还需要考虑到导体(铜)的表面粗糙度的影响。

审核编辑:刘清

-

高速电路中过孔设计注意事项2009-08-16 20588

-

高低温试验箱的三个重要因素2016-09-12 3887

-

PCB射频电路设计有什么重要因素?2019-08-14 1500

-

设计人员在采用ADC的设计中优化功耗时应考虑到的几个重要因素2021-03-16 1509

-

可靠性是军用嵌入式系统的重要因素是什么2021-04-23 1667

-

影响电动车蓄电池循环使用寿命的重要因素2009-11-16 1795

-

探讨制约“机器人红利”的重要因素2018-08-26 3381

-

从四个方面解读PCB射频电路基础特性及重要因素2020-08-07 1384

-

采用ADC的设计中优化功耗应考虑到的重要因素资料下载2021-04-15 1176

-

影响空压机散热的重要因素2022-04-09 4441

-

浅谈影响国内MCU企业发展的重要因素2023-02-05 981

-

影响放大电路高频特性的主要因素2023-09-18 5316

-

红外温度传感器哪个牌子好,选择品牌的重要因素和方法!2023-12-15 3963

-

影响电路性能稳定性的重要因素2025-08-21 1313

-

影响示波器带宽的重要因素——低通滤波器2026-03-04 407

全部0条评论

快来发表一下你的评论吧 !