FPGA图像处理—VESA标准与视频流介绍

描述

1.1 VESA 视频标准

VESA 视频标准同步信号产生器,是从事FPGA图像领域工程师经常使用到的模块。首先,它的标准时序来自 VESA 视频标准文件。

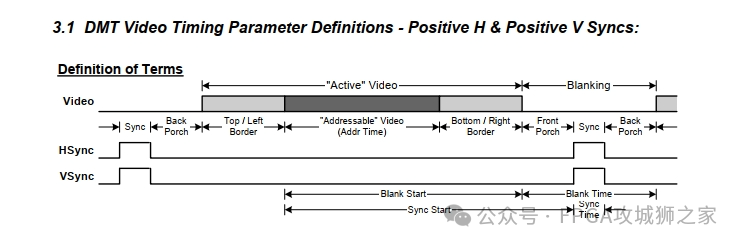

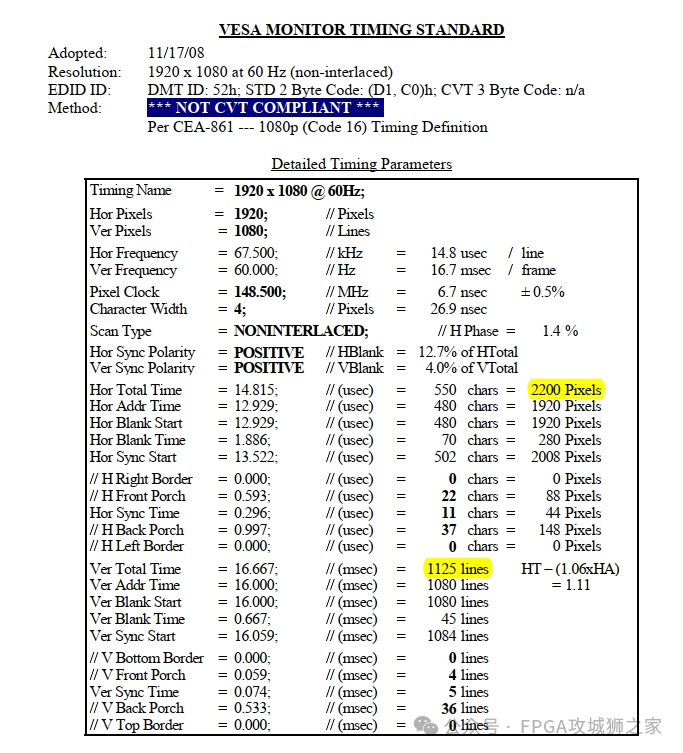

里面规定了VESA视频流同步信号的时序,以1080p为例可以查询到具体情况如下图

1.2 产生视频流同步信号

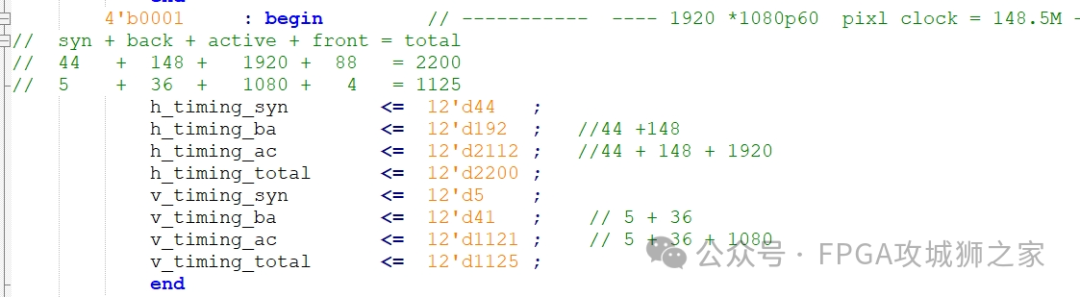

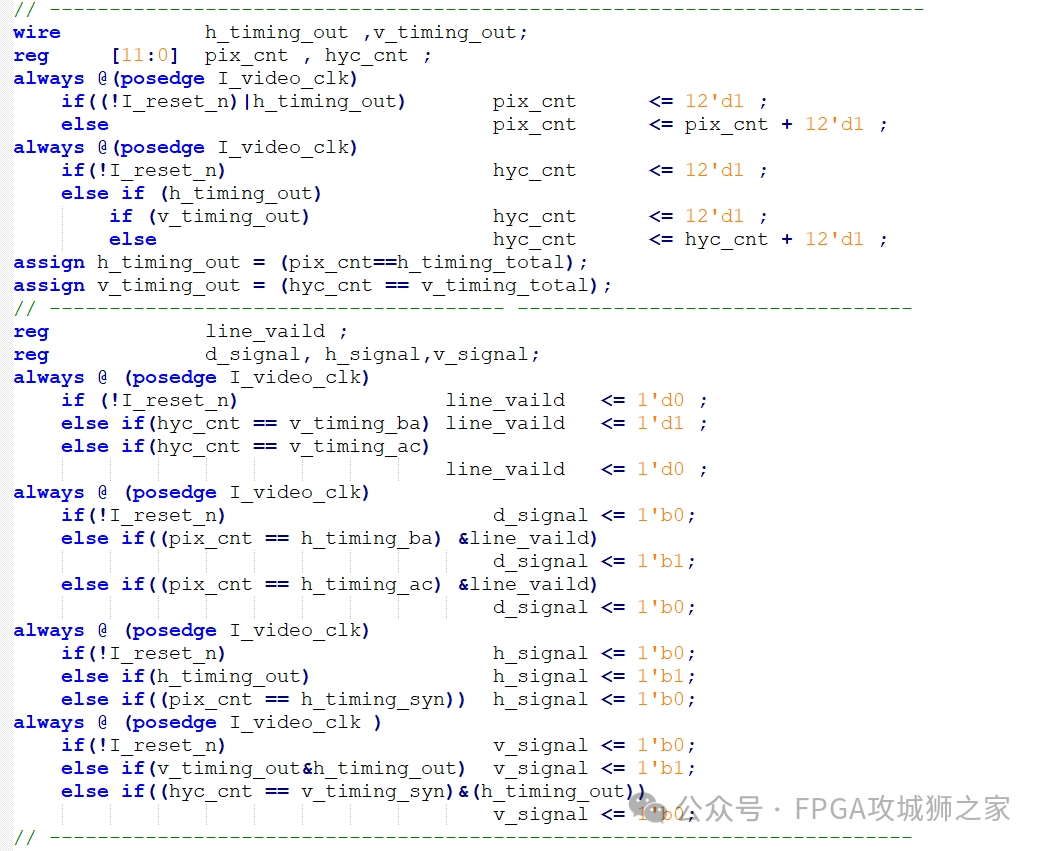

那么依照这个视频流可以在FPGA中产生标准时序,首先将这些参数添加进去,看注释中数据,就知道怎么填了。这样任意的分辨率都可以产生了。

然后利用这个参数产生同步信号,自此任意同步信号产品器就完成了。有人会说,这个东西,不就是xilinx官方的IP VTC 嘛,干嘛要重复造轮子。嘿嘿,那是因为,一,我们在做图像处理的时候要尽量的避免使用vivado这个仿真器,因为它实在是太墨迹了。二,如果是1080p以上的分辨率,比如4k,8k,的视频流,它在FPGA里面是双点,四点模式的,VTC没有这个功能,这个就要靠自己去实现了。

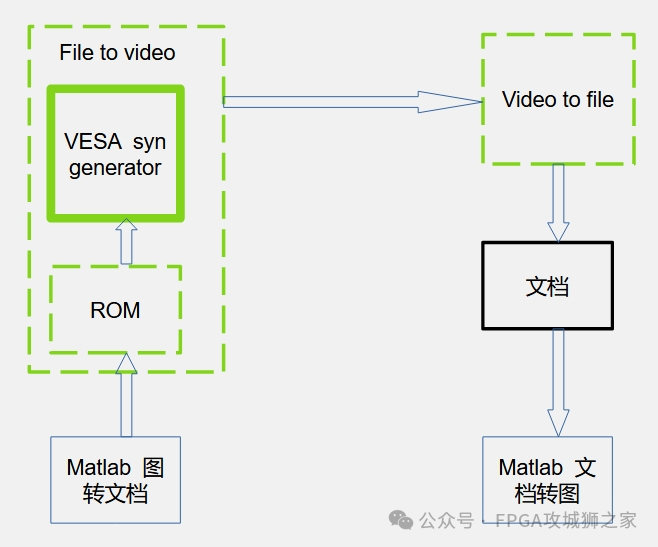

1.3 图导入FPGA

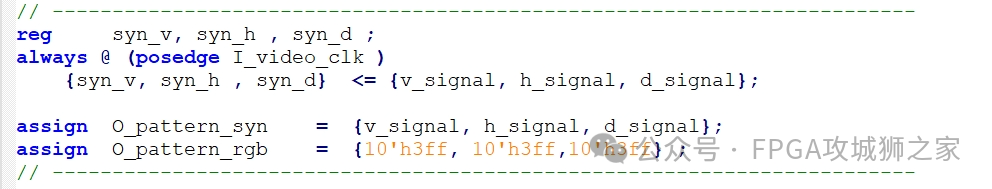

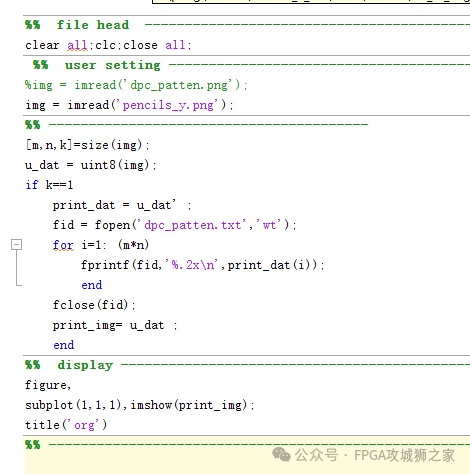

首先需要把图转换成txt,这个可以利用matlab

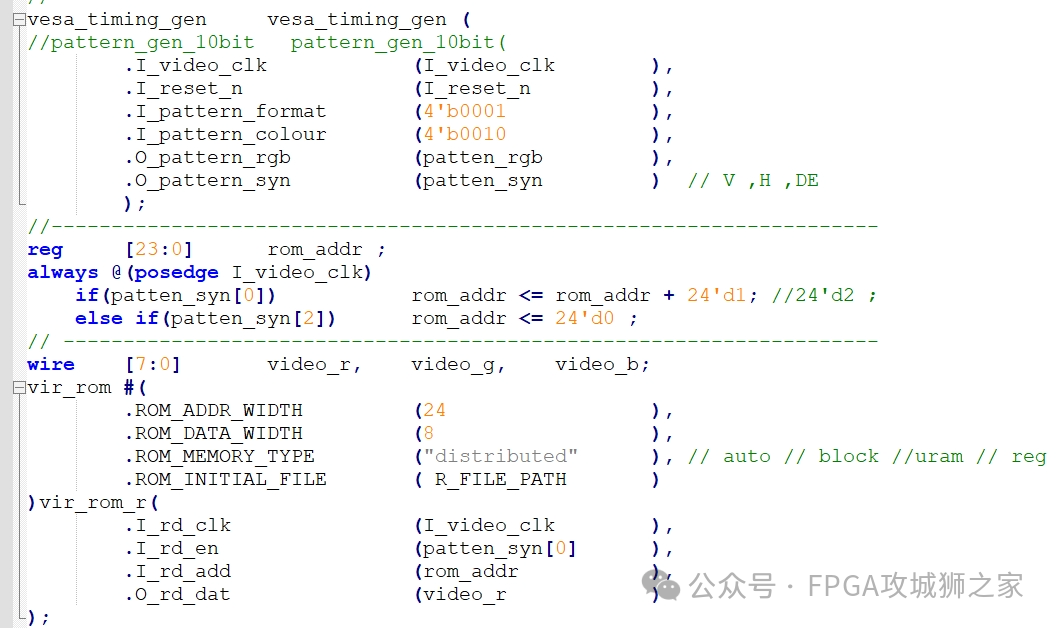

这是一张黑白图导入到matlab中,然后再保存到txt中的程序。然后在FPGA中将txt导入到rom,利用VESA视频流同步信号产生器,虚拟一条视频输入到代码中。

vir_rom 就是一个虚拟的rom。利用VESA视频流同步信号产生rom读地址,从而把rom中的图像数据导出来。

1.4 视频到文件

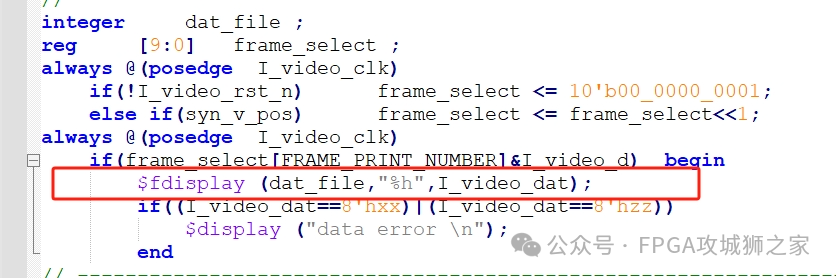

仿真的下半场,就是将视频流存入到文件中,这里需要写一个视频保存文件,选择其中一帧保存下来。此时modelsim会产生一个txt文件,保存我们所需要的数据。

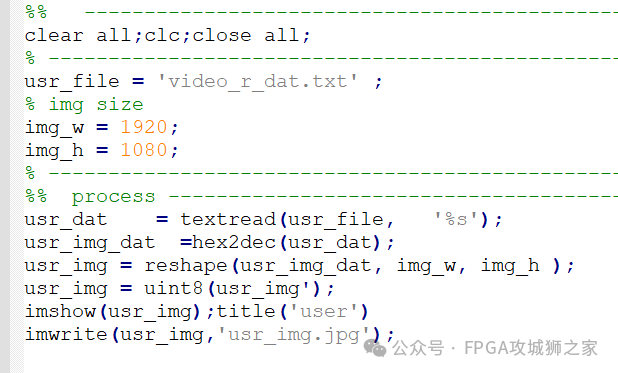

1.5 txt到图像。

当我们拿到了modelsim里面的仿真视频流一帧的文件txt,直接读入到matlab里面去就好了。几行代码就完成了华丽的转换。

自此,测试图产生器就完成了。既可以放到可综合项目中,也可以放到仿真工程中使用。自此,这个结构图里面的内容就完成了。

审核编辑:刘清

-

FPGA图像处理应用详细介绍2022-02-28 1128

-

如何在MATLAB中开发基于像素的视频和图像处理算法2019-08-29 3546

-

FPGA实时视频图像处理系统的原理是什么?2019-08-22 3420

-

一种基于FPGA的实时视频图像处理算法研究与实现2019-06-28 3979

-

FPGA视频教程之FPGA在视频图像处理领域的应用视频资料说明2019-04-04 1884

-

基于FPGA的实时视频图像采集处理系统2018-02-10 20594

-

一种基于DSP+FPGA视频图像采集处理系统的设计与实现2017-12-25 5826

-

基于FPGA的视频图像处理系统的设计2017-11-22 5486

-

基于FPGA的视频图像处理系统设计_李莲2017-03-19 1220

-

采用FPGA 实现视频和图像处理设计2015-10-26 4939

-

FPGA视频图像处理的学习2015-07-28 5330

-

基于FPGA的视频图像处理系统2015-05-23 23247

-

FPGA图像与视频处理培训2009-07-16 5997

-

基于FPGA的小型微光视频图像增强处理系统2009-01-11 627

全部0条评论

快来发表一下你的评论吧 !