FPGA时钟约束余量超差问题的解决方案

可编程逻辑

1396人已加入

描述

在设计FPGA项目的时候,对时钟进行约束,但是因为算法或者硬件的原因,都使得时钟约束出现超差现象,接下来主要就是解决时钟超差问题,主要方法有以下几点。

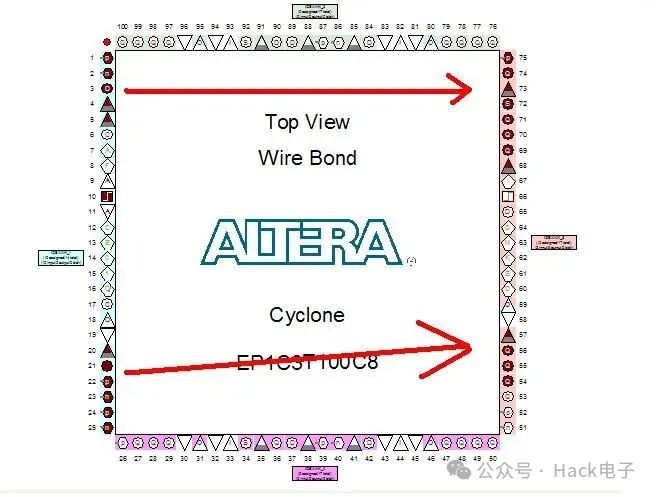

第一:换一个速度更快点的芯片,altera公司的cyclone系列FPGA,有6,7,8速度等级的,8的最慢,6的最快,或者cyclone系统4,5更快的芯片,当然了成本会增加些的。

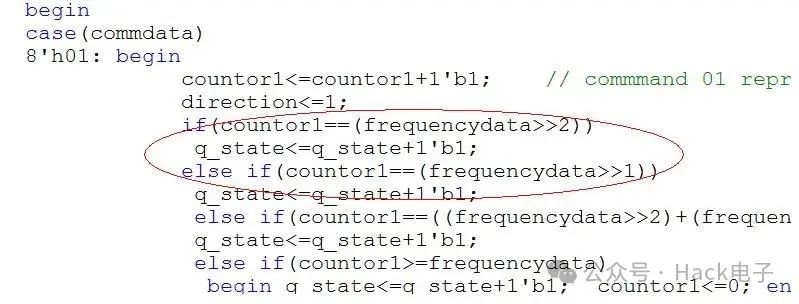

第二:尽量避免在FPGA中做乘法和除法的运算,除非这个FPGA有硬件乘法器。我使用的这个FPGA没有硬件乘法器,我就尽量利用左移或者右移来做乘法和除法运算。

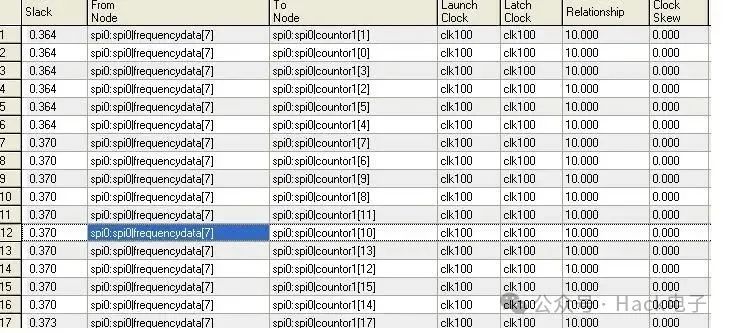

第三:重新分配一下IO管脚,这样在布局布线的时候,会提高一定程度的时钟余量。下图是调整IO分配以后,时钟余量提高了0.2ns。

第四:就是看看超差的那个线路,增加一些中间寄存器,或者使用流水线技术,就是将组合逻辑和时序逻辑分开,大的时序逻辑,尽量优化成由很多小的时序逻辑组成一个大的时序逻辑。或者更该程序代码,更该算法。到这一步就是没有办法的办法了。

第五:有些时候在程序中加入一些和项目不相关的代码,也可以提高正常程序的时钟约束余量,估计是不相关代码挤占了一些逻辑单元,使得正常程序在布局布线的时候,选择了其他路径吧。这个办法不固定,瞎猫碰死耗子的事情。

主要就是这几种方法了,首先要选好芯片,这是最重要的,不然为了省成本,最后发现芯片速度不够,很烦人的。

最后提一下有些网友提到FPGA发热厉害的现象,看看你在项目中是不是将unused pin 接地了,这样芯片会发热,最好将unused pin 微上拉,或者设置为输入即可。

审核编辑:黄飞

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA时序案例分析之时钟周期约束2020-11-19 6744

-

FPGA的IO口时序约束分析2022-09-27 2536

-

FPGA主时钟约束详解 Vivado添加时序约束方法2023-06-06 13020

-

FPGA时序约束之衍生时钟约束和时钟分组约束2023-06-12 4500

-

FPGA时钟周期约束讲解2023-08-14 1931

-

FPGA全局时钟约束(Xilinx版本)2012-02-29 9169

-

FPGA时钟约束问题2017-05-25 6598

-

如何设置差分时钟约束?2019-10-28 6510

-

差分时钟约束文件问题的解决办法?2020-08-05 3917

-

FPGA时序约束分析余量2019-11-10 5417

-

简述FPGA时钟约束时钟余量超差解决方法2021-10-11 4527

-

(30)FPGA原语设计(单端时钟转差分时钟)2021-12-29 1544

-

FPGA设计衍生时钟约束和时钟分组约束设置2023-06-26 7694

-

时序约束一主时钟与生成时钟2024-11-29 2834

-

FPGA时序约束之设置时钟组2025-04-23 1643

全部0条评论

快来发表一下你的评论吧 !