AMD MPSoC器件中启用SEM IP的策略与方法

描述

本文作者:AMD 工程师 Ivy Guo

SEM IP 的主要任务就是扫描 PL Configuration RAM, IP 自身也是在 PL 里面运行。其实 AMD MPSoC 器件同样可以运行 SEM IP。

但 SEM IP “默认”情况下在 MPSoC 上跑不起来,原因是 PCAP 和 ICAP 的控制权移交问题。ICAP 是 FPGA 控制配置相关操作的接口,SEM IP 的工作是建立在 ICAP 的基础上,它必须拥有 ICAP 的访问权限才能够正常工作。PCAP 和 ICAP 类似,它是 PS 访问配置控制端的接口。ICAP 和 PCAP 不能同时工作,否则会有冲突。在 MPSoC 刚刚 Boot 起来的时候,配置控制权的接口默认分配给了 PS 和 PCAP。此时 ICAP 不能访问,IP 也就无法工作起来。下面两个文档,以及本文介绍的简单指令,都是为了解决这个问题。

https://docs.xilinx.com/v/u/en-US/xapp1303-integrating-sem-ip-with-axi

https://docs.xilinx.com/v/u/en-US/xapp1298-integrating-sem-ip

我们先来看指令解决方法。

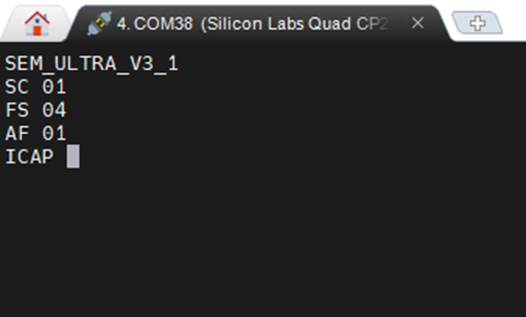

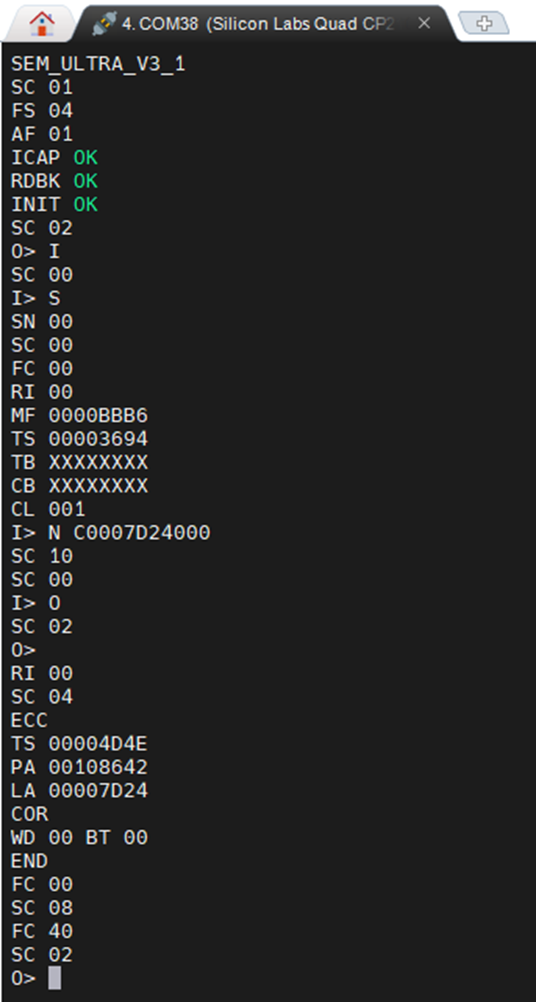

如果你在 MPSoC 上运行一个 SEM IP,观察到的 log 如下(此处以 ZCU102 为例):

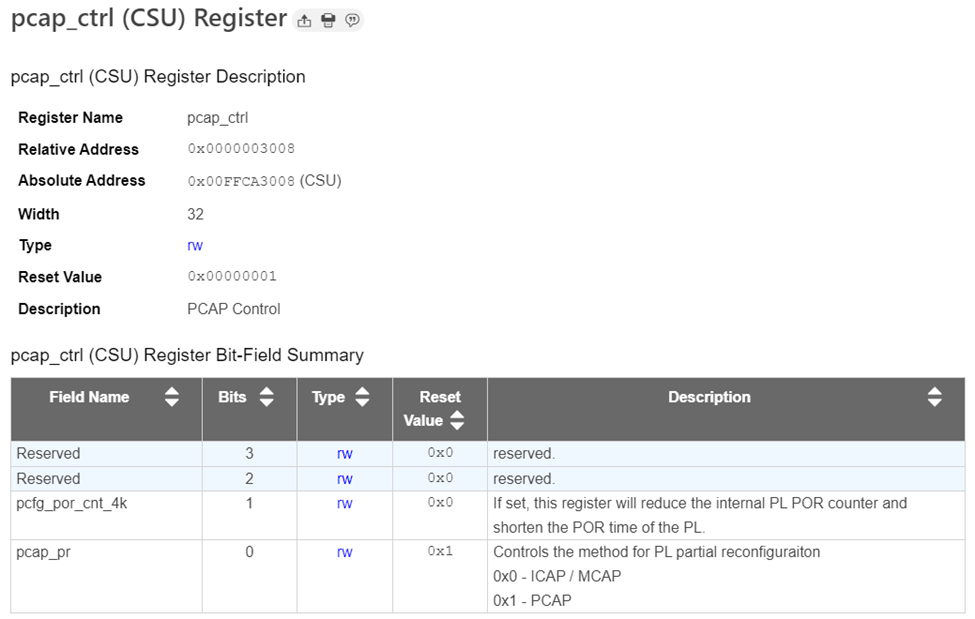

IP 在初始化阶段就卡住了。从 Uart 口的 log 看 ‘ICAP’ 后续无字符输出,这是典型的 IP 无法通过 ICAP 访问控制端的状态。此时需要把控制权从默认的 PCAP 切换到 ICAP 去。我们需要利用 pcap_ctrl 这个寄存器。UG1087 对其定义如下:

https://docs.xilinx.com/r/en-US/ug1087-zynq-ultrascale-registers/pcap_rdwr-CSU-Register

地址为 0xffca3008, Bit 0 的 pcap_pr 就是控制位。其上电默认值为 0x1。

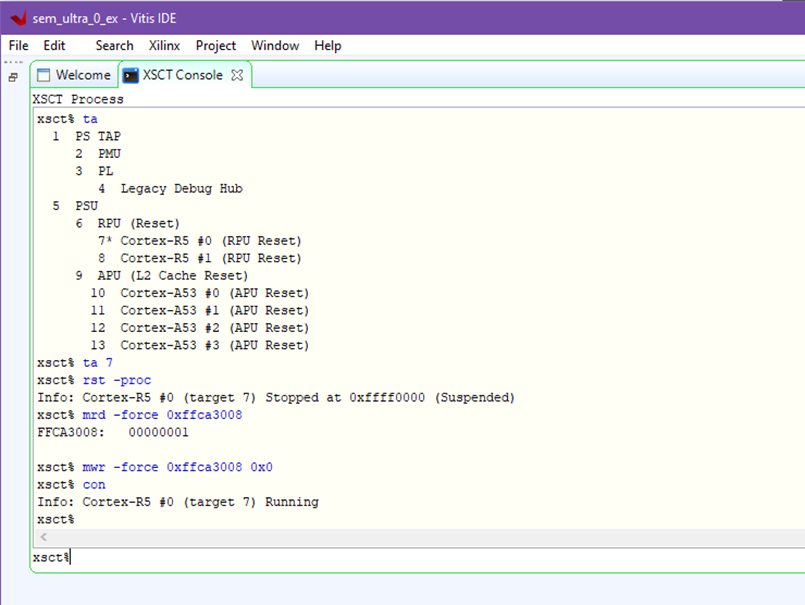

打开 XSCT,连接到 ZCU102 的器件 XCZU9。

根据地址查询一下 pcap_ctrl 寄存器的值,返回值为 0x1, 说明确实 PCAP 在控制:

xsct% mrd -force 0xffca3008

FFCA3008: 00000001

把 Bit 0 清零:

xsct% mwr -force 0xffca3008 0x0

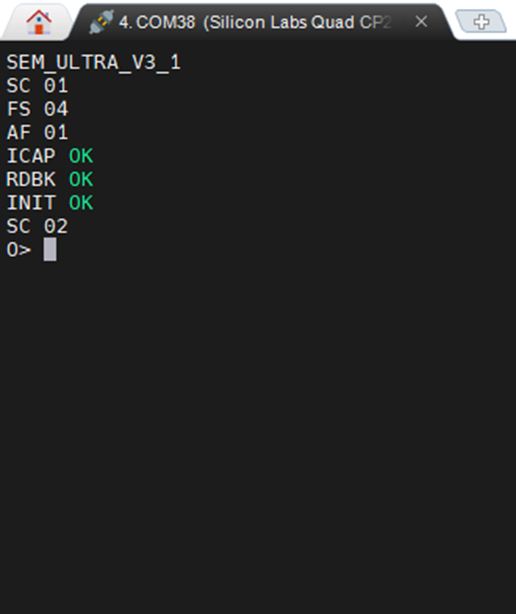

此时可以看到 Uart 窗口里 ICAP 立即变为可以访问的状态,并继续打印出了完整的 Initialization log:

随意操作一下 IP,根据 IP 的响应情况,可以看到其已经完全正常开始工作了:

如果 PCB 上有 JTAG 控制接口,那么通过上述方法,直接修改 pcap_ctrl 寄存器就可以了。但是如果 PCB 上没有 JTAG 口,或者是外场的产品应用,我们就要使用 XAPP1298 或者1303的方法,利用 PS 来做控制权的移交。后续文档中我们会解析一下其使用方法并更新一下参考文件。

AMD 自适应 SOC 及 FPGA 中文技术支持社区

审核编辑:黄飞

-

基于AMD Versal器件实现PCIe5 DMA功能2025-06-19 2001

-

SEM IP在MPSoC器件上的使用指南2025-08-13 1904

-

AMD Vivado IP integrator的基本功能特性2025-10-07 2312

-

抓取SEM IP的串口log的详细步骤2022-05-12 7109

-

参加搜索引擎营销SEM培训的好处?2011-04-11 3366

-

Zynq UltraScale + MPSoC USB 3.0 CDC器件类设计2019-01-03 7811

-

如何调试Zynq UltraScale+ MPSoC VCU DDR控制器2021-01-07 2793

-

SoC中IP核互连的不同策略2009-11-28 546

-

AMD-Xilinx MPSoC的Watchdog在Linux中使用的简明教程2023-07-07 2063

-

几种常见的关于SEM IP的冲突2023-07-10 1686

-

Zynq UltraScale+ MPSoC中的隔离方法2023-09-13 999

-

Zynq UltraScale+ MPSoC中的隔离方法应用笔记2023-09-15 585

-

SEM IP多种工作模式的区别和选择指导2023-10-13 2398

-

AMD/Xilinx Zynq® UltraScale+ ™ MPSoC ZCU102 评估套件2024-11-20 2956

-

AMD Versal自适应SoC器件Advanced Flow概览(下)2025-01-23 1806

全部0条评论

快来发表一下你的评论吧 !