自举驱动电路供电原理 为什么高压大功率应用不宜使用自举驱动?

描述

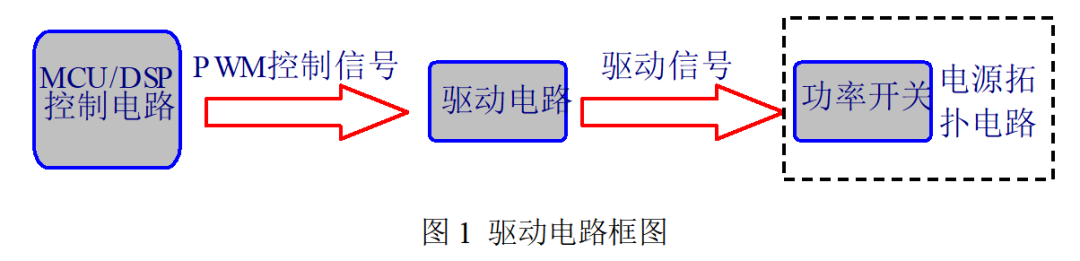

驱动电路位于控制电路与负载电路之间,其本质是将控制电路的PWM控制信号进行功率放大,为负载电路提供足够的电流或功率。

优良的驱动电路具有能够提高系统可靠性、减小开关器件应力(开/关过程中)、以及提高能量转换效率并降低EMI/EMC等优点。MOS-FET/IGBT栅极驱动的优劣对其性能的发挥和可靠工作有很大影响。

本篇结合自己以及客户以前的工程经验,较为客观务实地阐述了自举驱动和隔离供电驱动的优缺点,对搭建高可靠功率驱动器有一定的指导意义。

|

常用驱动电路有两种,分别为自举驱动电路和隔离驱动电路。

一

自举驱动电路供电原理

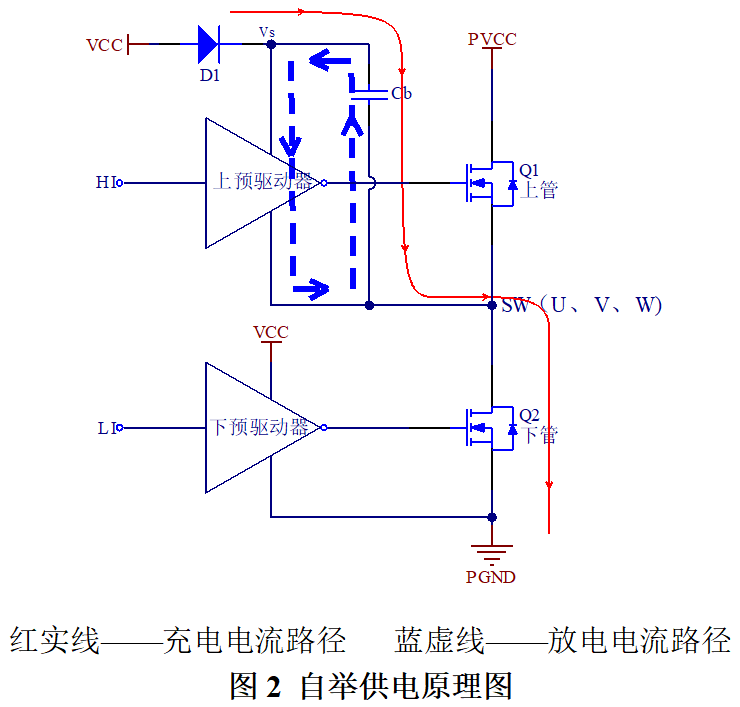

自举栅驱动因其结构简单,成本低的优点,仍然在低压中功率场合有着广泛的使用。自举栅驱动有高、低两个通道,低侧为一个简单的缓冲器,与控制输入有相同的接地点。具体工作原理如图2所示:

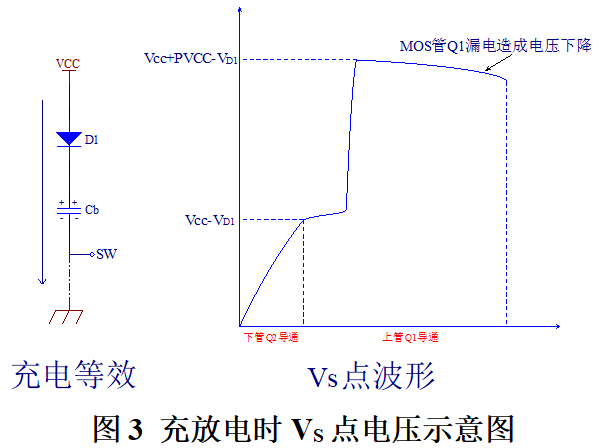

当SW点电压下降到远低于Vcc或下拉至地时,自举电容Cb才能充上电。即上管Q1关断,下管Q2开通(要完全导通),且要有足够的导通时间。因为充电是通过自举二极管D1正向导通完成的,它有导通时间和动态电阻。所以在自举二极管D1和自举电容Cb选定后,输入PWM的频率和最大最小占空比需满足一定的要求。

当上管Q1导通,下管Q2关断时,SW点通过上管Q1接Power,电容两端电压不能突变,因此VS点的电位(相对于PGND)远高于Vcc,具体如图3所示故此时上驱动器的供电单一来源就是Cb上存储的电能。因而,在PWM的频率和最大、最小占空比已知的情况下,Cb的容值选取很重要。自举二极管D1此时的作用为防止Vs点电压回灌到输入电压Vcc,反向截止。

需要注意的是,自举驱动电路在高压应用时缺点很多,具体为:

(1)当上功率管关闭而下功率管导通时,由于寄生电感效应,上、下管之间会出现负压,会给栅极驱动电路的输出端造成麻烦,会将某些内部电路下拉到地以下。同时由于栅极驱动电路的耐压很弱,该负电压会对栅极驱动造成损伤。另外则是该负电压的转换会使自举电容处于过压状态。

(2)自举驱动电路内部需要使用高电压电平转换器,高电平转换到低电平时会带来噪声,为消除噪声通常会在电平转换器中加入滤波器,增加传输延迟,而下管驱动器为了匹配上管驱动器,需加额外滤波器,增加整体延长。

(3)自举驱动电路与控制芯片共地,不够灵活。不能满足复杂拓扑电路要求,如在三相PFC电路中,要求多个输出能够转换至控制公共端电平以上或以下。

二

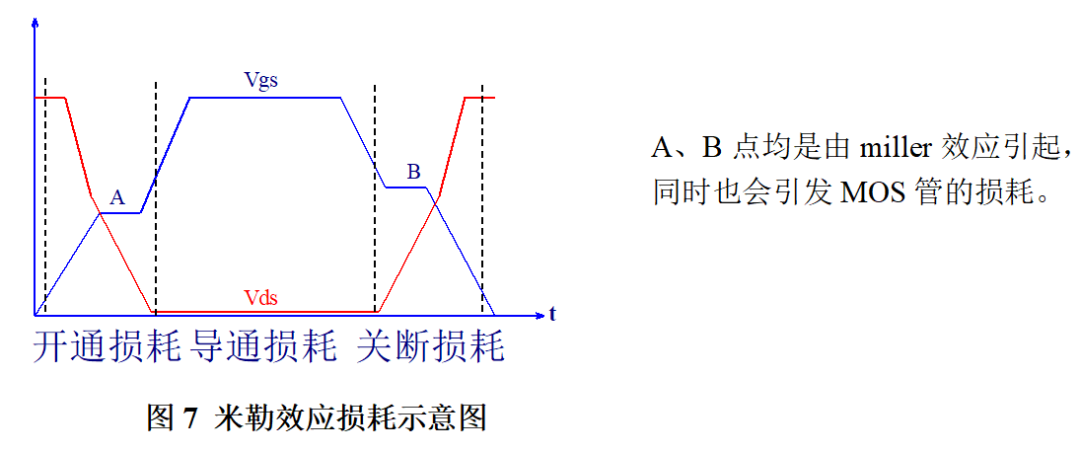

MOS/IGBT的米勒效应(miller)

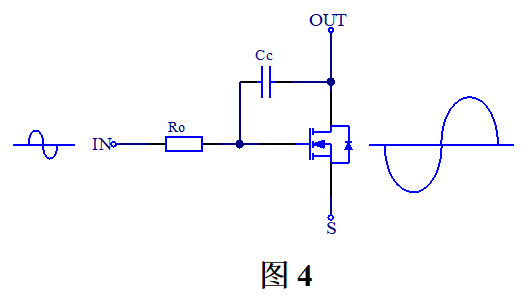

关于米勒效应,可以简单理解为由于线路拓扑结构所致,在放大环节中,输入到输出之间的电容容值会被放大。以CMOS运算放大器的设计为例,第二级均有一个频率补偿单元,以防止自激发生。如下图4所示:

这个Cc就是补偿电容。它是用金属—氧化层—半导体结构实现的。其容值:

其中ε为氧化层的介电常数,S为电容极板面积,d为氧化层厚度。即在工艺制造规程已定的情况下,ε和d是固定的,为获得一个一定值的Cc,理想情况下就需要把S设计大。但是在实际应用时是不可行的,因为不符合集成电路的设计理念(追求更小、更微)。

举例说,设计需要一个Cc=500pF的补偿电容,若不使用miller效应,则这个电容的面积有可能占到运算放大器面积的一半以上(视运算放大器的具体设计而异)。这显然是不能接受的。

而使用如上图所示的miller结构,它会对这个Cc放大。就是说,从out端看进去,Cc是本征值;而从输入端IN看进去,则是K倍的Cc值(当K=100时,则Cc=5pF)。这个K系数就是当地管子的电压放大倍数(对MOS管而言),或是电流放大倍数(对双极管而言)。这个Cc就能做小了。

故miller效应对运算放大器很有用。但对MOSFET驱动极为负面。这也正验证了亘古不变的道理“任何事物都具有两面性”。

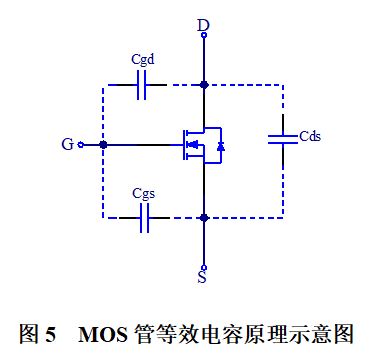

MOS管生产加工过程中,势必会引入Cgd、Cgs、Cds;Cgd会在MOS管的开启/关断过程中引入负反馈;即MOS管动态特性参数,

输入电容 Ciss=Cgs+Cgd

输出电容 Coss=Cds+Cgd

反向传输电容 Crss=Cgd(即米勒电容)

三

上/下预驱动器驱动电流(Iom+/Iom-)要求

在供电源能力有保障的前提下,并且假设在MOS管栅极上串联的电阻RG(为克服SW点过冲/振铃必须要加)为短路态,则下分析有参考价值:

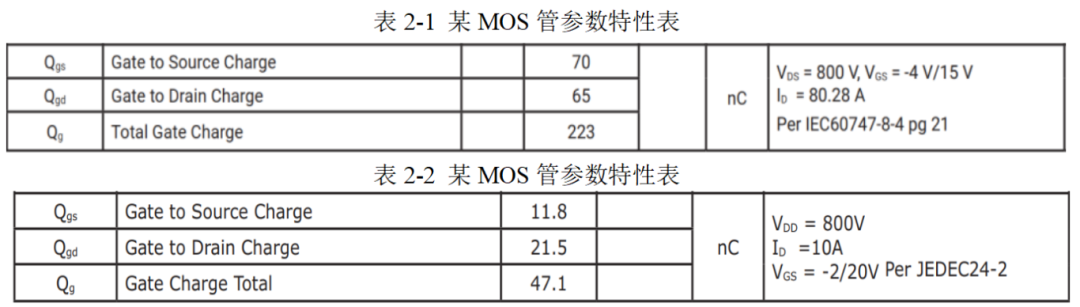

对一个MOS管充/放电,可依据公式Q=I·t。Q在选定MOS管的PDF中可查到。一般用Qg,Qgs,Qgd表示,单位为nC,如表2所示:

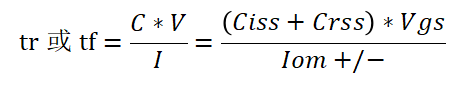

结合Q=C·V,不难得出下式:

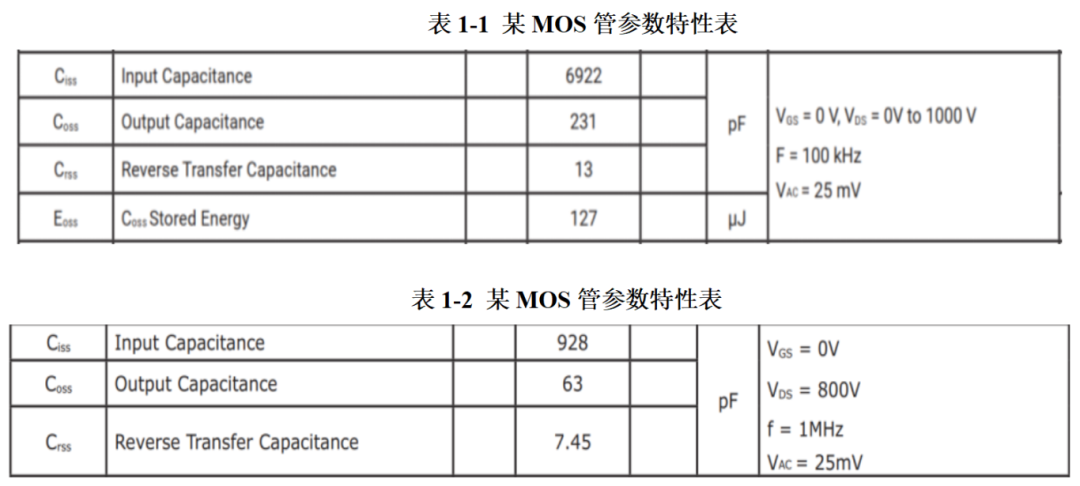

Ciss和Crss在选定MOS管PDF文件中都可查到,如表1所示。

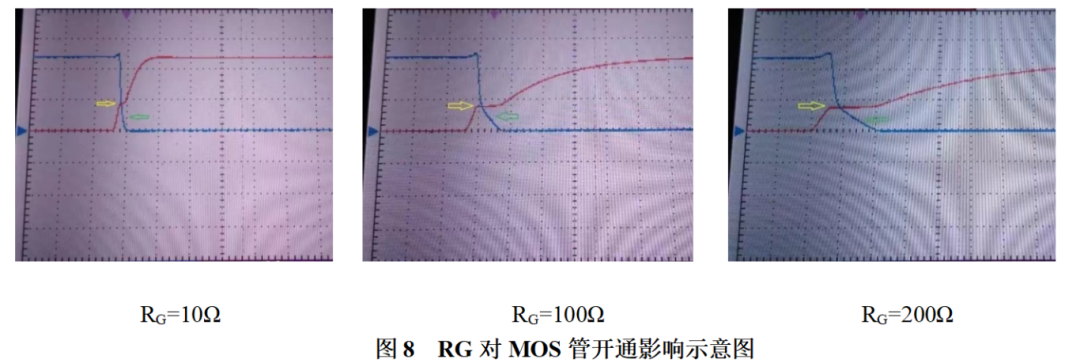

对选定型号MOS管,为减小tr/tf,即减小动态功耗,Iom+/﹣应该越大越好。但大多数三相自举驱动器受管芯面积限制,Iom+/-均较单驱动器来得小。如果不作计算分析,随意加一个不合适的RG,则MOS管的动态功耗就可能会较大。具体影响如下图8所示

四

为什么高压大功率应用不宜使用自举驱动

1、电荷关系式:Q=C·V,Q=I·t;

2、耐压越高、功率越大,则结面积越大,即Cgs、Cds、Cgd越大;

3、功率侧供电电压越高,则Cgd上储存的电荷量越大,因而需要前驱动器对其充电/放电的电荷量就越大;

4、由于自举驱动的能量来源仅限于Cb,因而很难在工程折中;

5、假若不能对Cgd充饱/泄放干净,不光是引发当地MOS管热功耗增大,还有可能引发上、下管有很大的穿通电流;

6、从这个意义上也能理解为什么同一个自举驱动在有些工况下应用正常,而在另一工况下就不正常的原因。

五

隔离驱动电路供电原理

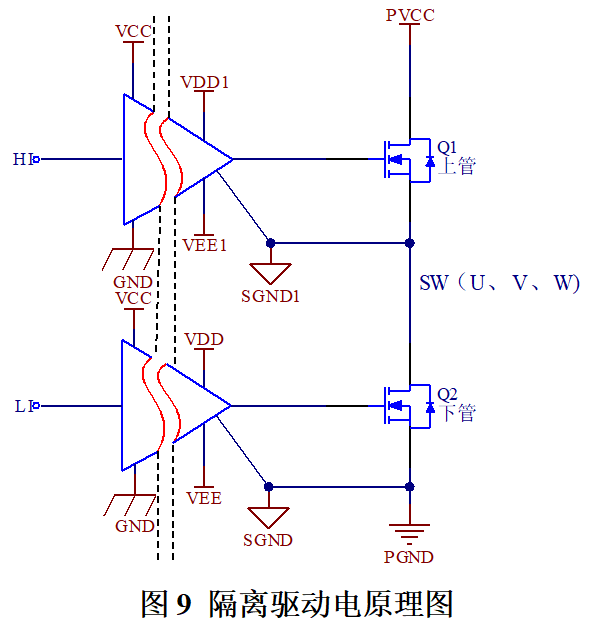

隔离驱动由集成隔离式栅极驱动及隔离电源组成,具体工作原理如图9所示

隔离对于栅极驱动器非常重要,不仅可以保护系统免受高压影响,更重要的是隔离输出接地点灵活,控制芯片与驱动可接不同的接地点,不易受雷击与浪涌影响,抗干扰能力强。

六

高端驱动隔离供电

从前面的讨论不难看出,由于实际应用时,PWM可能的频率变化,最小最大占空比限制,以及电机可能的堵转/换相,高端驱动采用隔离供电无疑是最优选项。

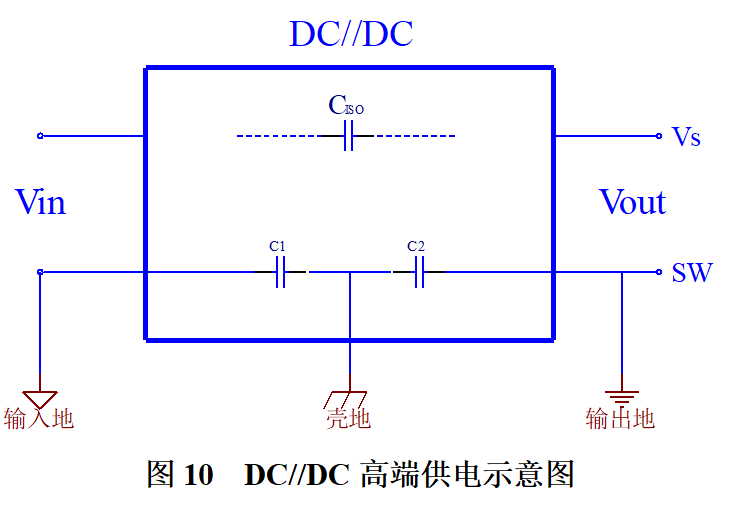

DC/DC的隔离电压一般都有保障。但其CMTI指标则千差万别。

所谓的CMTI(Common-Mode-Transient-Immunity)是指隔离抗共模瞬变的免疫能力。一般以KV/us为单位。它其实是衡量一个隔离器件抗扰度的指标。很重要,但实际选型时往往被忽略。

一个隔离DC/DC的CMTI指标好坏,受变压器绕制方法,内部元器件布局、输入输出引脚的爬电距离等因素影响。简单说,受输入输出等效的电容影响。

假如把一个DC/DC的输入输出引脚分别短路在一起,用电容表测得的电器≥150pF(@f=1MHz)时,该DC /DC的CMTI指标会很差,不适合三相桥的高端供电。这是因为高端驱动的参考点是SW点。它的电位是在PGND和Power上来回摆的,尤其是当功率侧供电电压比较高时,会通过DC//DC原次边的寄生电容反馈到输入侧的干扰非常大,DC//DC的正常工作会受到影响。

注意,有些DC//DC在设计时,为了压输出纹波和改善VIN端的电磁兼容性,会在输入地,输出地,壳地之间加C1、C2两个电容。这种结构的DC//DC绝对不能用于高端驱动使电用。

上图中的CISO是输入输出之间的寄生电容。

七

驱动SiC-MOSFET的特殊性

SiC-MOSFET属于第三代功率半导体器件。具有高功率密度、耐压高、耐高温及抗辐射电迁移等优点,特别适合恶劣环境。

然而其缺点也很明显。由于其禁带宽度比硅基的宽,其正向跨导Gfs就小,导致为减小静态损耗,加在栅极上的电压VGS就得大。另外,它的Crss比较大,miller效应就比较大,致使开启或关闭需要的电荷量Q就大。因此在使用时必须采用miller钳位,或者负压关断来解决。

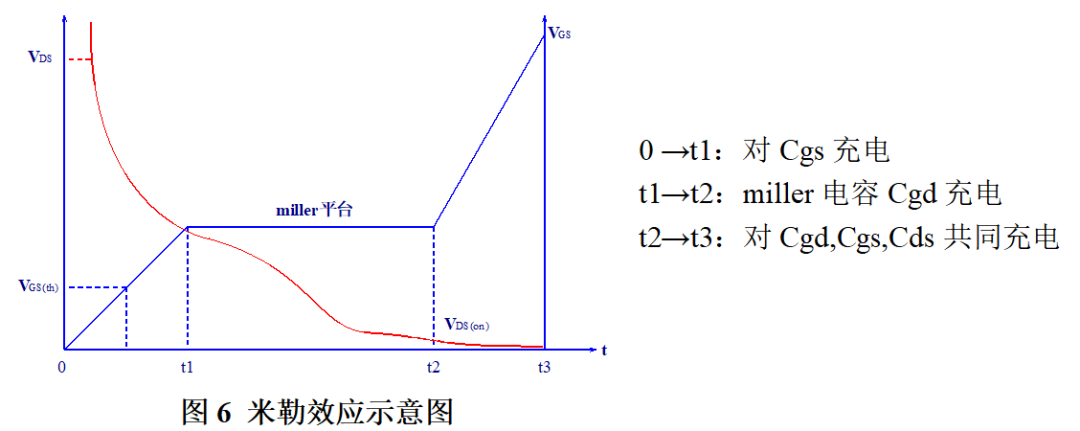

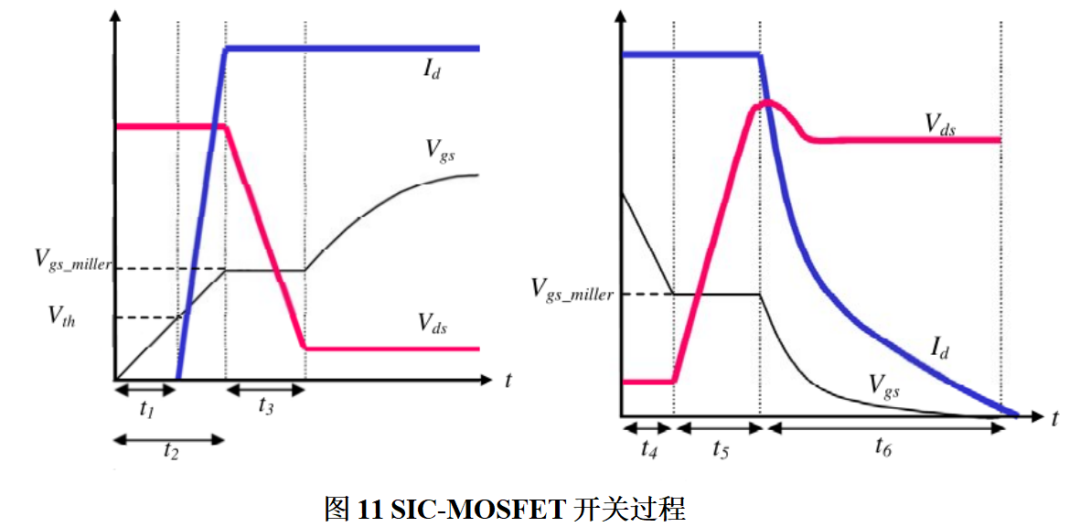

SiC-MOSFET仍属于压控型器件,所需要的静态驱动电流很小。由于寄生电容的存在,开通过程就是寄生电容充电过程;相反,关断过程就是寄生电容的放电过程。在感性负载下的开关过程如图11所示,以开通过程为例,该过程可以分为:延时阶段、电流上升阶段、米勒阶段和过驱动四个阶段。关断过程与开通过程基本相同,只是时间顺序相反。

通过对SiC-MOSFET器件特性和开关过程的分析可知,工作在高频的SiC-MOSFET驱

动电路必须具备以下特点:

(1)驱动电压波形的上升沿和下降沿要足够陡,从而增大开关速度,减小开关损耗;

(2)驱动电路要提供足够大的瞬时电流,缩短输入电容充电时间;

(3)驱动回路阻抗要适宜,回路阻抗太小容易造成驱动回路谐振,可能造成误导通或通

态电阻较大,回路阻抗太大会减缓输入电容充电时间,延长开关速度,增加开关损耗;

(4)栅极驱动电压要合理,栅极驱动电压越高,感应导电沟道越大,则通态电阻越小,

从而减小通态损耗;但栅极驱动电压太大时,较小的谐振引发的电压波动可能击穿栅极氧化层,造成器件永久失效;

(5)驱动电路还要能够提供负压关断,防止器件误导通,同时也加速了关断过程;

(6)驱动电路要紧靠被驱动器件,减小寄生参数对驱动电路性能的影响。

八

HJ393耐高温SIC-MOSFET/IGBT隔离式驱动器

航晶微电子团队在充分了解应用背景的情况下,在充分消化吸收以上原理的基础上,通过四次迭代,依托自身稳定的工艺平台,于十年前推出的HJ393系列产品,业已批量应用于高压大功率SiC-MOSFET/IGBT应用。

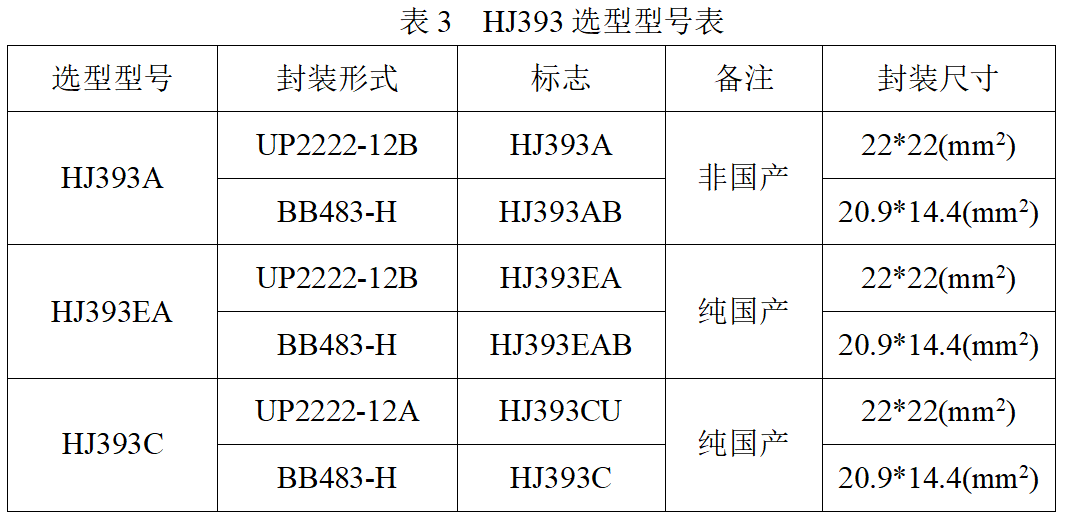

其原理为将供电、PWM输入信号与SiC-MOSFET的浮栅驱动进行隔离。隔离开通正电压≥+15V,有利于补偿SiC-MOSFET正向跨导小的缺陷,减小RON;隔离关断负电压≤-3.5V,有利于克服SiC-MOSFET较大的miller效应引入的误导通。区别于自举浮栅驱动,输入PWM的占空比可达0~100%,这个特性使得它可用于高压大功率SSPC设计。具体选型见下表3

-

自举电路自举电阻和自举电容的工作原理是什么?2024-01-11 2947

-

自举电路如何计算2023-01-30 7532

-

高压栅极驱动 IC 自举电路的设计与应用指南2022-12-12 4632

-

高压栅极驱动器自举电路设计2021-06-19 1901

-

BUCK自举驱动说明2021-05-09 1119

-

【专辑精选】自举电路系列教程与设计资料2019-04-22 2829

-

大功率LED高压驱动电路,LED driver2018-09-20 3678

-

利用MOSFET管自举升压驱动电路2016-12-16 1723

-

CPU-供电的MOSFET-自举驱动电路设计2016-06-21 3608

-

自举供电驱动电路设计-魏巍2016-05-11 865

-

高压大功率IGBT驱动型号介绍2012-09-03 1420

-

CPU供电的MOSFET自举驱动电路设计2011-09-14 1991

-

驱动半桥自举电路2010-01-04 11086

-

IGBT高压大功率驱动和保护电路的应用及原理2009-10-09 3067

全部0条评论

快来发表一下你的评论吧 !