HBM、HBM2、HBM3和HBM3e技术对比

存储技术

描述

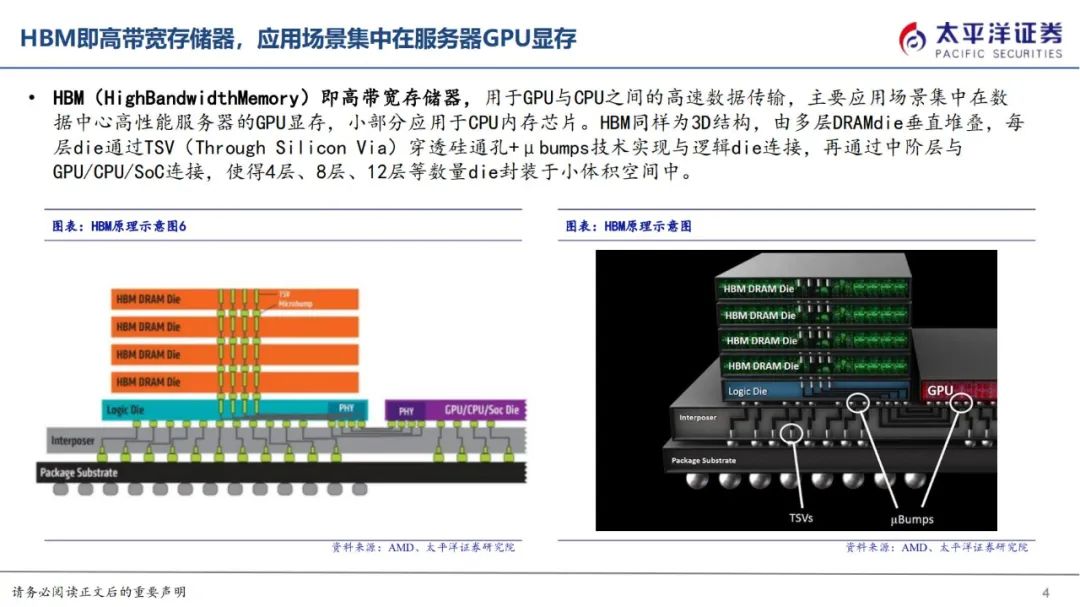

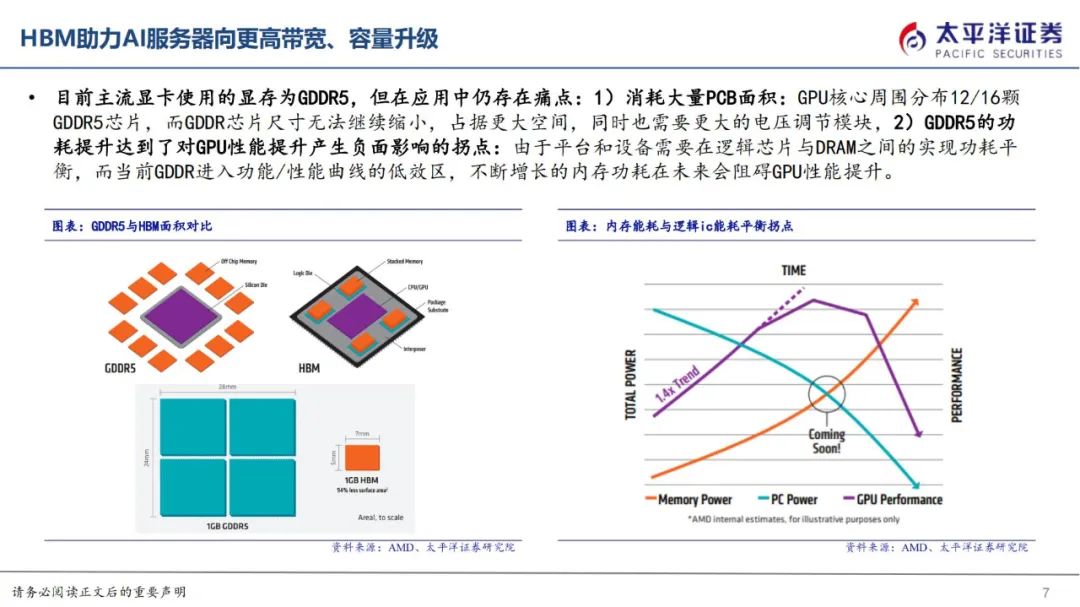

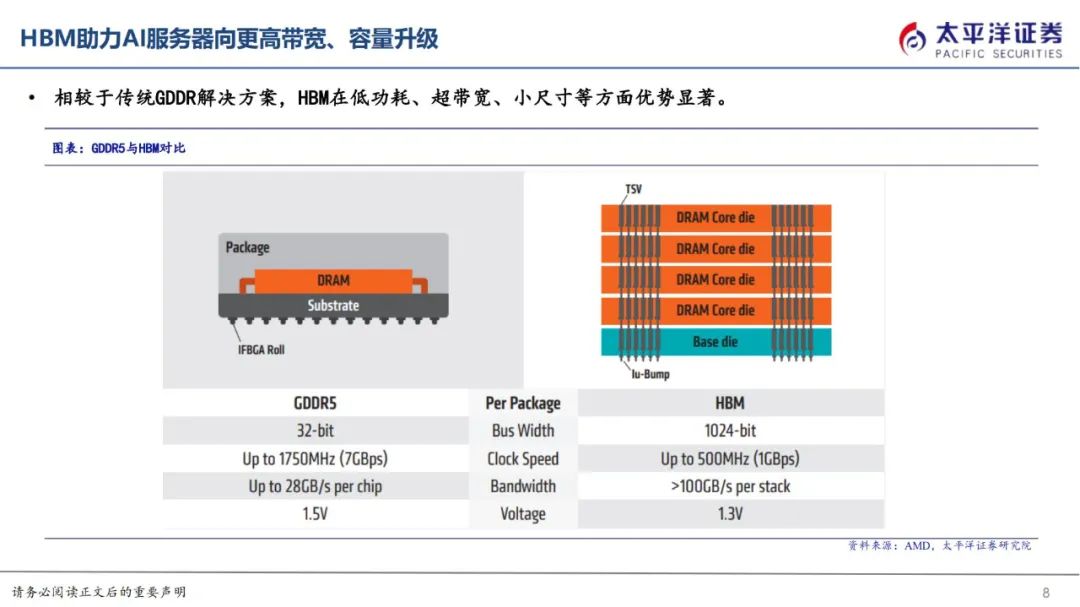

HBM即高带宽存储,由多层DRAM Die垂直堆叠,每层Die通过TSV穿透硅通孔技术实现与逻辑Die连接,使得8层、12层Die封装于小体积空间中,从而实现小尺寸于高带宽、高传输速度的兼容,成为高性能AI服务器GPU显存的主流解决方案。

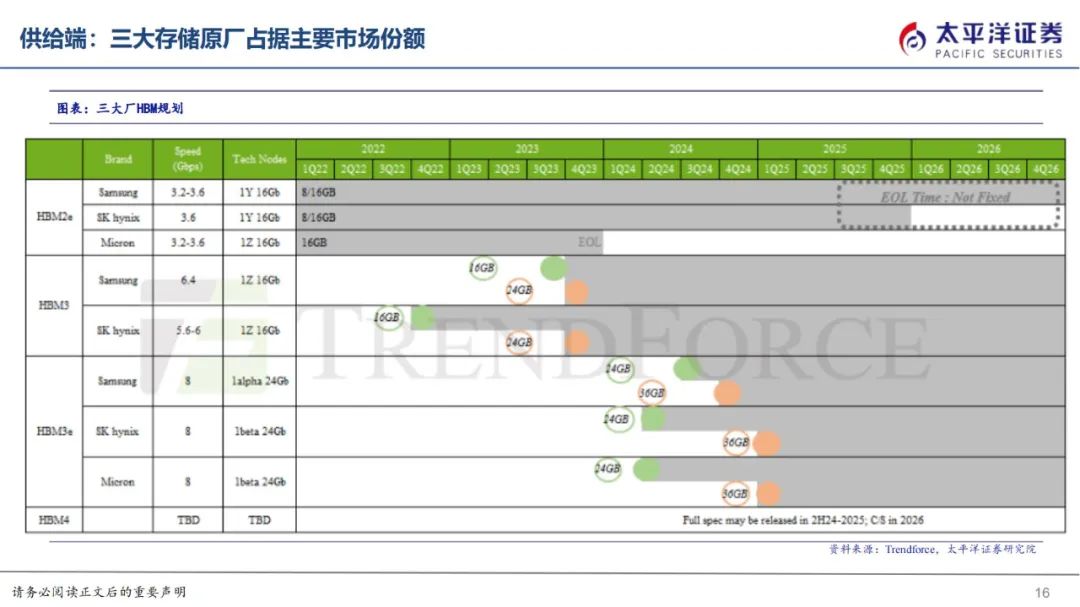

目前迭代至HBM3的扩展版本HBM3E,提供高达8Gbps的传输速度和16GB内存,由SK海力士率先发布,将于2024年量。

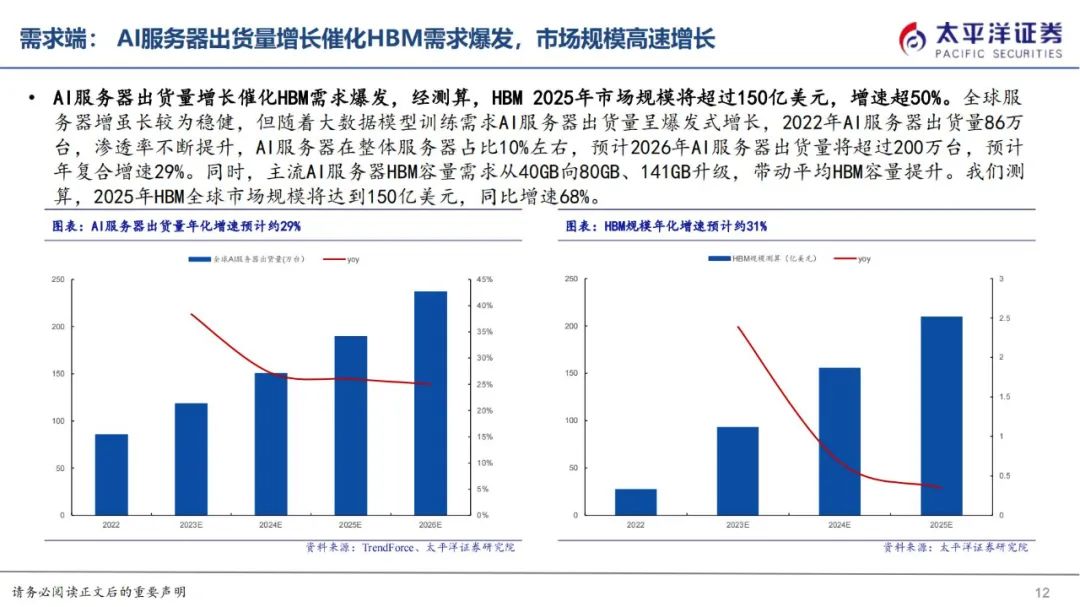

HBM主要应用场景为AI服务器,最新一代HBM3e搭载于英伟达2023年发布的H200。根据Trendforce数据,2022年AI服务器出货量86万台,预计2026年AI服务器出货量将超过200万台,年复合增速29%。

AI服务器出货量增长催化HBM需求爆发,且伴随服务器平均HBM容量增加,经测算,预期25年市场规模约150亿美元,增速超过50%。

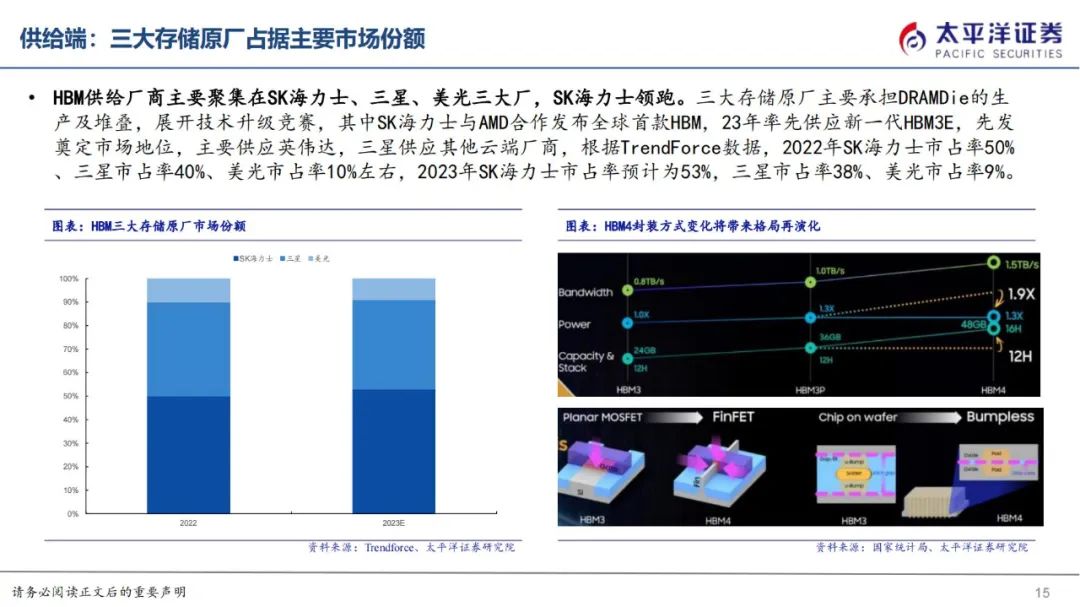

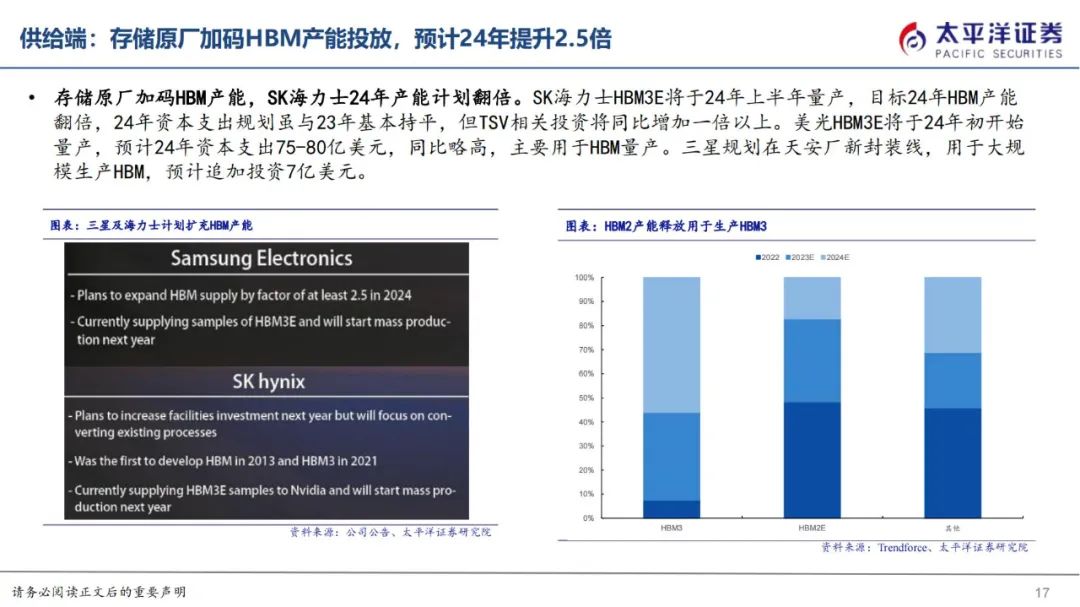

HBM供给厂商主要聚集在SK海力士、三星、美光三大存储原厂,根据Trendforce数据,2023年SK海力士市占率预计为53%,三星市占率38%、美光市占率9%。HBM在工艺上的变化主要在CoWoS和TSV。

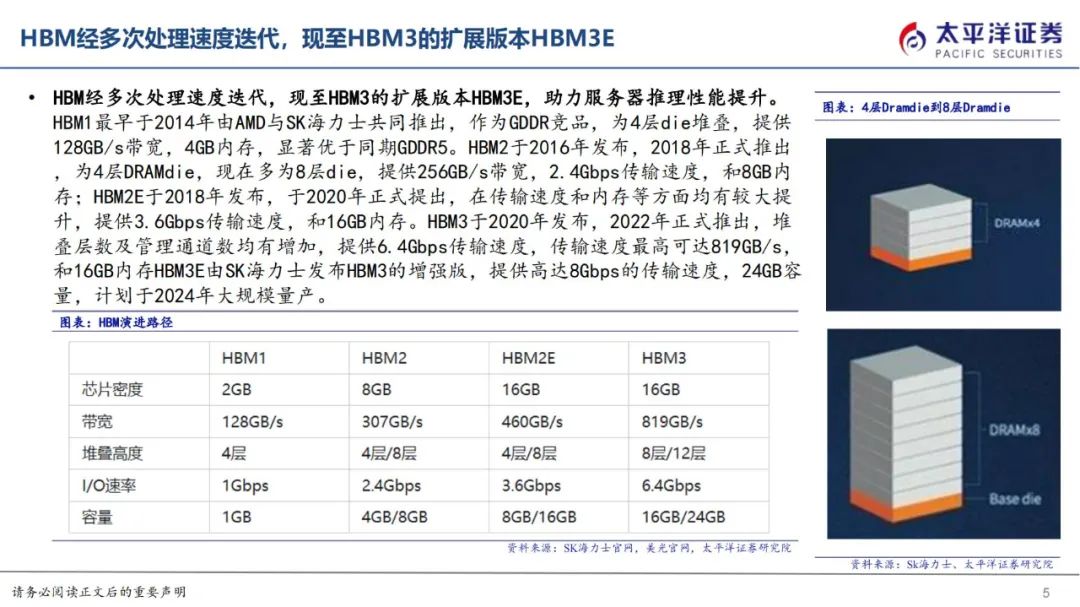

HBM1最早于2014年由AMD与SK海力士共同推出,作为GDDR竞品,为4层die堆叠,提供128GB/s带宽,4GB内存,显著优于同期GDDR5。

HBM2于2016年发布,2018年正式推出,为4层DRAMdie,现在多为8层die,提供256GB/s带宽,2.4Gbps传输速度,和8GB内存;HBM2E于2018年发布,于2020年正式提出,在传输速度和内存等方面均有较大提升,提供3.6Gbps传输速度,和16GB内存。HBM3于2020年发布,2022年正式推出,堆叠层数及管理通道数均有增加,提供6.4Gbps传输速度,传输速度最高可达819GB/s,和16GB内存HBM3E由SK海力士发布HBM3的增强版,提供高达8Gbps的传输速度,24GB容量,计划于2024年大规模量产。

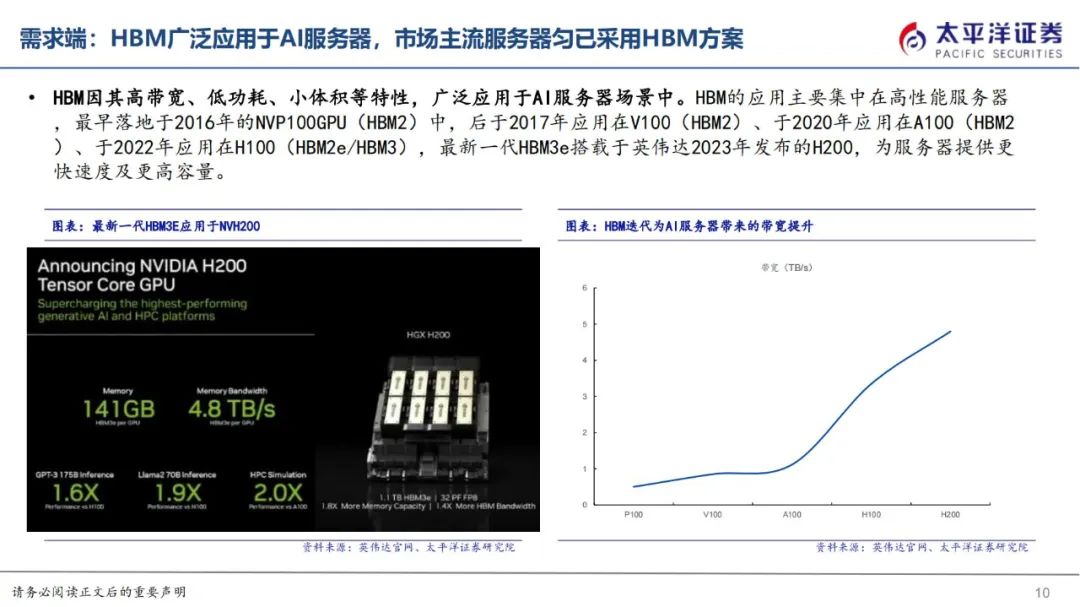

HBM因其高带宽、低功耗、小体积等特性,广泛应用于AI服务器场景中。HBM的应用主要集中在高性能服务器,最早落地于2016年的NVP100GPU(HBM2)中,后于2017年应用在V100(HBM2)、于2020年应用在A100(HBM2)、于2022年应用在H100(HBM2e/HBM3),最新一代HBM3e搭载于英伟达2023年发布的H200,为服务器提供更快速度及更高容量。

HBM供给厂商主要聚集在SK海力士、三星、美光三大厂,SK海力士领跑。三大存储原厂主要承担DRAMDie的生产及堆叠,展开技术升级竞赛,其中SK海力士与AMD合作发布全球首款HBM,23年率先供应新一代HBM3E,先发奠定市场地位,主要供应英伟达,三星供应其他云端厂商,根据TrendForce数据,2022年SK海力士市占率50%、三星市占率40%、美光市占率10%左右,2023年SK海力士市占率预计为53%,三星市占率38%、美光市占率9%。

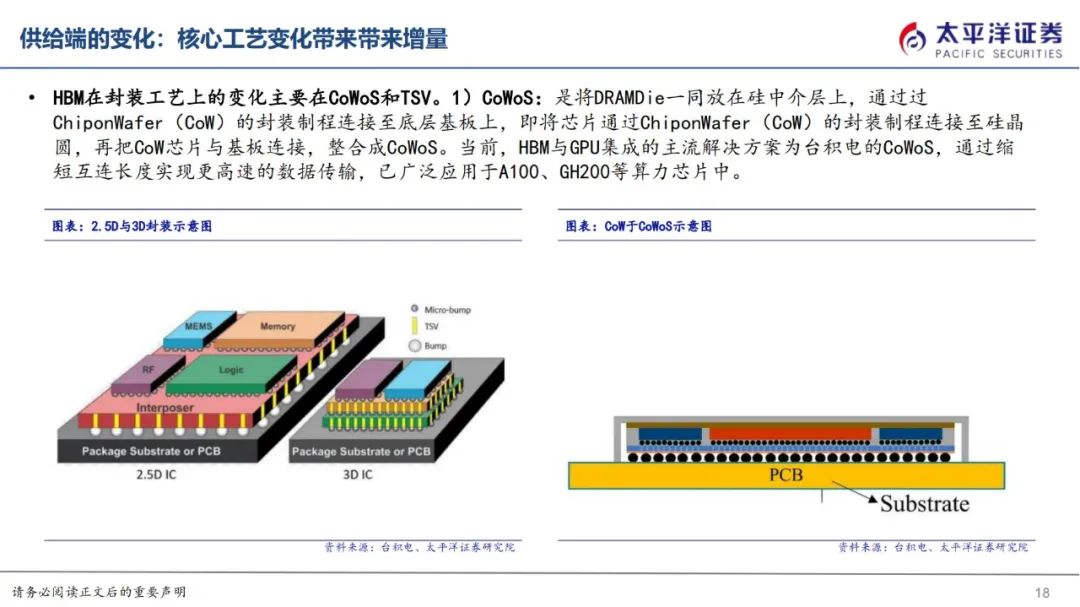

HBM在封装工艺上的变化主要在CoWoS和TSV。

1)CoWoS:是将DRAMDie一同放在硅中介层上,通过过ChiponWafer(CoW)的封装制程连接至底层基板上,即将芯片通过ChiponWafer(CoW)的封装制程连接至硅晶圆,再把CoW芯片与基板连接,整合成CoWoS。当前,HBM与GPU集成的主流解决方案为台积电的CoWoS,通过缩短互连长度实现更高速的数据传输,已广泛应用于A100、GH200等算力芯片中。

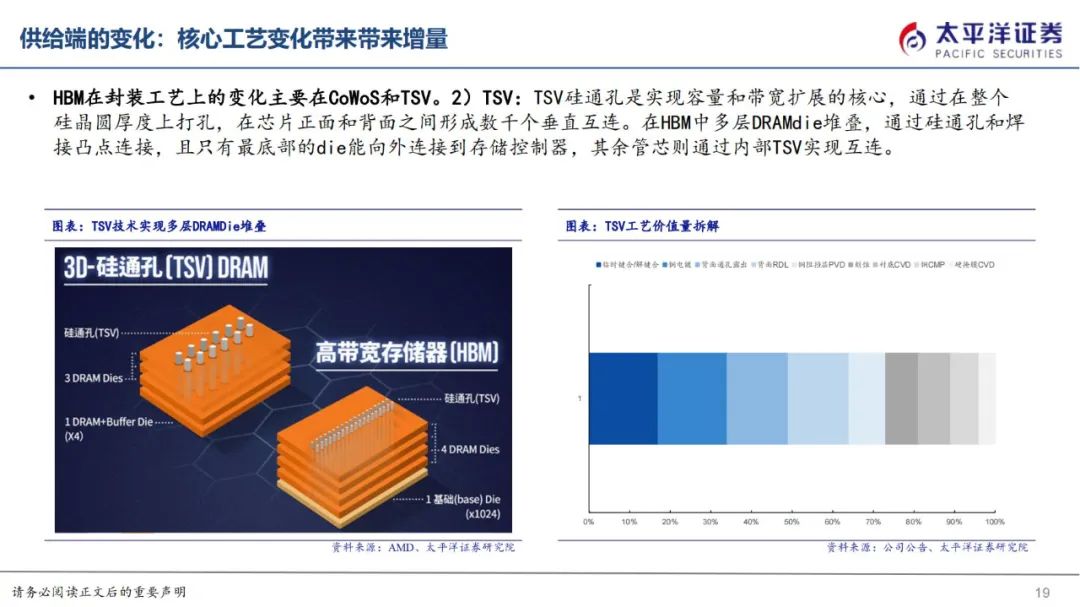

2)TSV:TSV硅通孔是实现容量和带宽扩展的核心,通过在整个硅晶圆厚度上打孔,在芯片正面和背面之间形成数千个垂直互连。在HBM中多层DRAMdie堆叠,通过硅通孔和焊接凸点连接,且只有最底部的die能向外连接到存储控制器,其余管芯则通过内部TSV实现互连。

审核编辑:黄飞

-

三星电子将供应改良版HBM3E芯片2025-02-06 1314

-

三星电子HBM存储技术进展:12层HBM3E芯片,2TB/s带宽HBM4即将上市2024-03-27 2644

-

什么是HBM3E内存?Rambus HBM3E/3内存控制器内核2024-03-20 5180

-

三星电子成功发布其首款12层堆叠HBM3E DRAM—HBM3E 12H2024-02-27 1920

-

AMD发布HBM3e AI加速器升级版,2025年推新款Instinct MI2024-02-25 1653

-

英伟达将于Q1完成HBM3e验证 2026年HBM4将推出2023-11-29 1826

-

预计英伟达将于Q1完成HBM3e验证 2026年HBM4将推出2023-11-27 1922

-

追赶SK海力士,三星、美光抢进HBM3E2023-10-25 4813

-

HBM3E明年商业出货,兼具高速和低成本优点2023-10-10 1882

-

SK海力士开发出全球最高规格HBM3E,向英伟达提供样品2023-08-22 1910

-

SK海力士开发出全球最高规格HBM3E2023-08-21 2058

-

英伟达、微软、亚马逊等排队求购SK海力士HBM芯片,这些国产设备厂迎机遇2023-07-06 3980

-

还没用上HBM2E?HBM3要来了2021-08-23 2574

全部0条评论

快来发表一下你的评论吧 !