IC设计:ram的折叠设计操作步骤

电子说

描述

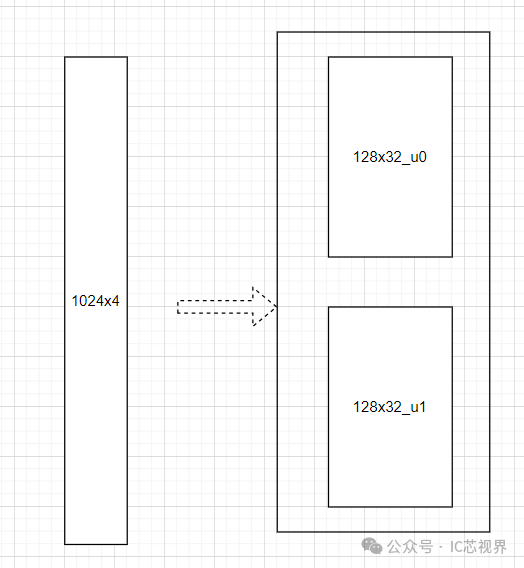

在IC设计中,我们有时会使用深度很大,位宽很小的ram。例如深度为1024,位宽为4bit的ram。此类的ram有个明显的缺点:形状狭长,不利于布局布线、导致读写接口走线过长,不利于时序收敛。

此时为了方便布局布线和时序收敛,我们通常会进行折叠设计。

如下图所示,深度为1024,位宽为4bit的双端口1r1w的ram,有一个读接口,一个写接口,支持同时读写操作,出于以上考虑,我们会进行折叠设计,采用2个128x32的1r1w的ram实现。

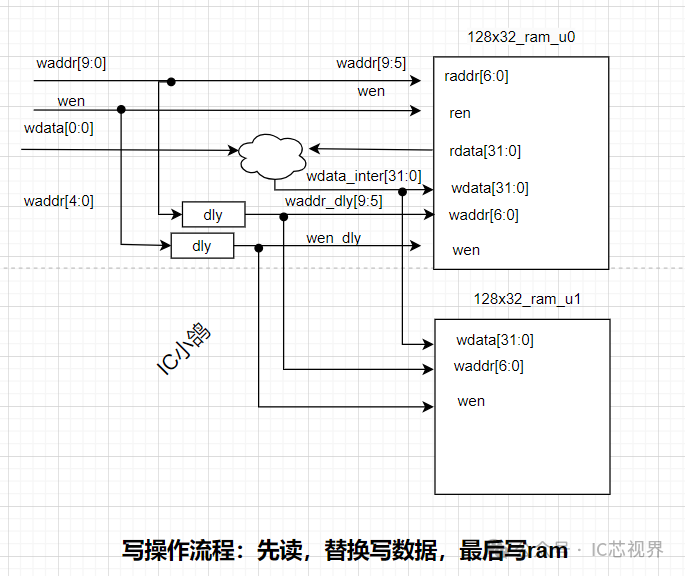

如图所示:两个2个128x32存储的内容完全一致。

无论是否进行折叠设计,ram接口信号位宽均一致。读写地址位宽为10bit,读写数据位宽为4bit。部分ram读写接口信号如下

| 信号 | 位宽 | 描述 |

| waddr | 10 | 写地址 |

| wen | 1 | 写使能信号,1表示写有效 |

| wdata | 4 | 写数据 |

| raddr | 10 | 读地址 |

| ren | 1 | 读使能信号,1表示读有效 |

| rdata | 4 | 读数据 |

进行写操作时:

使用waddr[9:5] 作为读地址,读128x32_ram_u0,获得rdata[31:0] 使用waddr[4:0] 选择rdata[31:0]中一个bit,使用wdata[0:0]进行替换,得到写入数据wdata_inter[31:0] 使用waddr_dly[9:5] 作为写地址,将wdata_inter[31:0]作为写数据同时写入128x32_ram_u0和128x32_ram_u1。

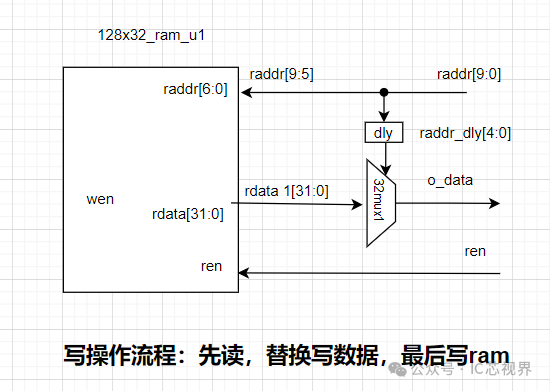

进行读操作时: 使用raddr[9:5] 作为读地址,读128x32_ram_u1,获得rdata1[31:0] 使用raddr[4:0] 选择rdata1[31:0]中一个bit,赋值给o_rdata。

为什么需要用两个128x32的ram?

因为1024x1_1r1w_ram_wrapper需要同时支持读写操作,而在折叠设计中,写操作需要先读ram,读操作也需要读ram,如果仅仅使用1个128x32的ram,就会出现有两个读请求同时产生,因此为了避免出现此冲突,需要2个128x32的ram才能实现。

审核编辑:刘清

-

IC设计:常见的ram访问冲突2023-11-13 3642

-

用Jlink和J-Flash RAM读取单片机程序和烧录单片机程序操作步骤2022-01-26 8428

-

不止于大,如何打造优秀的折叠屏应用体验2022-12-23 1677

-

LS23机芯升级操作步骤2013-09-05 487

-

DXP入门基本操作步骤2016-07-20 1748

-

回流焊操作步骤2018-12-12 23780

-

折叠屏有什么意义2019-03-10 13603

-

RAM的项目设计需求与操作步骤2019-11-20 2052

-

IC的焊接步骤与用注意哪些基本事项2019-11-06 12689

-

带电作业的操作步骤2020-06-13 9587

-

如何使用FPGA内部的RAM以及程序对该RAM的数据读写操作2022-02-08 16153

-

TANDY WP 2 RAM IC卡开源分享2022-07-15 608

-

IC设计中关于ram的应用2023-11-17 1181

-

华为pockets折叠屏手机怎么贴膜2024-03-05 6607

-

网关基本配置操作步骤-ModbusRTU2025-03-27 390

全部0条评论

快来发表一下你的评论吧 !