MCU制程工艺迈进28nm时代,汽车行业的创新之路

控制/MCU

描述

1.车规MCU制程工艺朝28nm进发

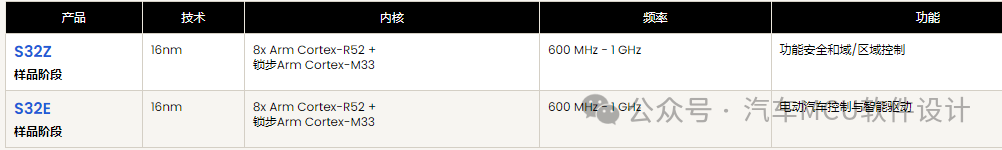

随着英飞凌发布了关于AURIX TC4xx系列即将量产的新闻,国际MCU大厂关于下一代跨域融合架构的车规MCU基本凑齐了。 而跨域融合对车规MCU算力要求的提升,MCU的制造工艺开始向更先进的制程迈进。 NXP采用TSMC 16nm FinFet技术推出了S32Z和S32E样品,分别用于区域控制和电动汽车(xEV)控制和智能驱动。

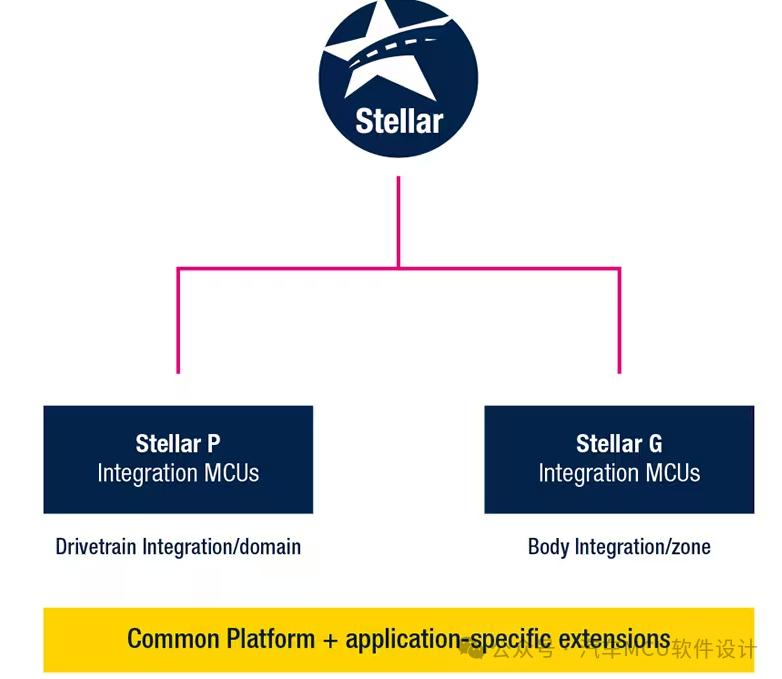

ST采用自家28nm FD-SOI技术推出了Stellar G和P系列,分别用于网关、控制等;

瑞萨早在18年就推出了基于28nm的集成eFlash技术的MCU,并在20年前后推出了涵盖车身、网关到动力控制的高性能MCU U2AU2B。

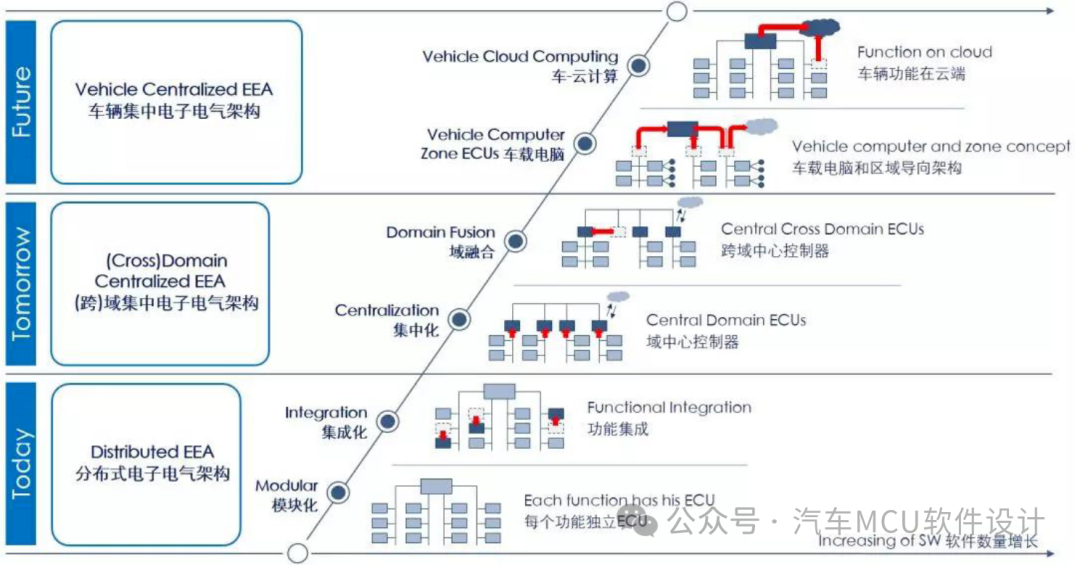

可以看到,随着电子电气架构架构的演进,对车规MCU的算力、资源、性能的要求都提升了一个档次。

从目前掌握到的情况下,针对跨域融合产品,这几家MCU大厂均瞄准了如下几个方面:

针对加速车内报文的路由处理能力的硬件化设计;

针对跨域融合的MCU硬件虚拟化功能;

满足ISOSAE 21434的信息安全解决方案;

针对MCU无感SOTA的优化设计

针对跨域融合的大容量存储器

针对新电子电气架构的高性能大算力的CPU

很明显,上述技术是需要更先进的制程工艺来满足的。理论上,制程工艺越小,单位面积能容纳的晶体管就越多,功耗相对就越小,因此选用28nm、22nm乃至16nm无可厚非。 不过,众所周知MCU迟迟在40nm徘徊,最主要的因素还是受限MCU内部的eFlash本身制程,即使台积电能够做到28nm的eFlash,产能也不见得能够释放给每家MCU大厂。 那么对于MCU的存储器,这几家国际大厂是如何考量的呢?

2.MCU存储器概述

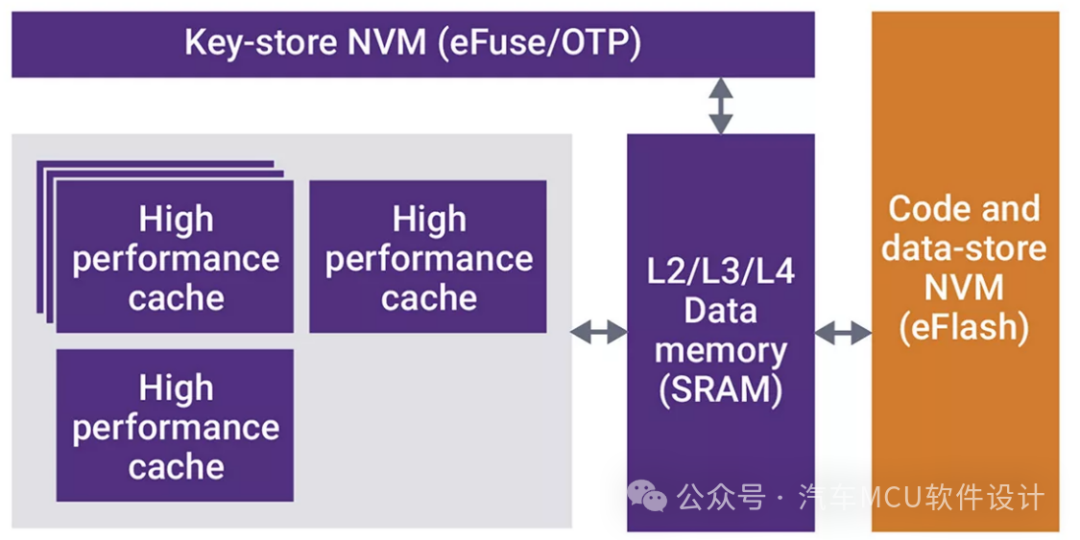

在一款MCU中,有4类常见的存储器:

缓存:靠近核内的小型存储器,可以提升MCU取指或者读数据的性能;

SRAM:提高整体系统效率,属于高密度存储器,掉电数据丢失,价格不菲。

程序、数据存储:大容量NVM(Non-Volatile Memory)用于存储代码和数据,掉电不丢失。eFlash 是实现这一目的的首要选择。

密钥存储存储器:用于存储芯片ID、安全代码、SRAM 修复签名或模拟电路调试信息的小型 NVM。常见的如ROM、OTP存储器或 eFuses。

其层级结构和关联关系如下图:

在业界,一直有着买Flash送MCU的说法,可见eFlash对于MCU的重要程度,相较于片外Flash,eFlash运行效率更高,但是该技术在制造时所需工艺与数字、模拟电路所需的CMOS工艺还是有比较大区别。以常见的浮栅技术为例,eFlash需要额外的光罩层次,用于编程、擦除的电压通常大于5V,这些技术在28nm甚至更小的硅几何结构下不容易实现微缩化,因此给MCU往先进制程工艺的推进带来了阻碍。 因此业内开始考虑是否有替代或者优化eFlash的解决方案。 根据台积电和新思的官网介绍,目前关于NVM市场除了eFlash工艺,eNVM工艺也异军突起,它在CMOS工艺基础上生产出带NVM的芯片,主要有以下几种技术:

PCM(Phase-Change Memory):相变存储器

STT-MRAM(Spin-Transfer Torque ):嵌入式自旋转移矩磁阻RAM

RRAM(Resistive RAM):电阻随机存储器

3.MCU大厂的选择

瑞萨日前宣布,公司已基于STT-MRAM的电路技术开发出具有快速读写能力的测试芯片。该MCU 测试芯片采用 22 纳米工艺制造,包括一个 10.8Mbit嵌入式 MRAM 存储单元阵列。它实现了超过 200 MHz 的随机读取访问频率和10.4MB/s的写入吞吐量。

3.1 瑞萨自研STT-MRAM

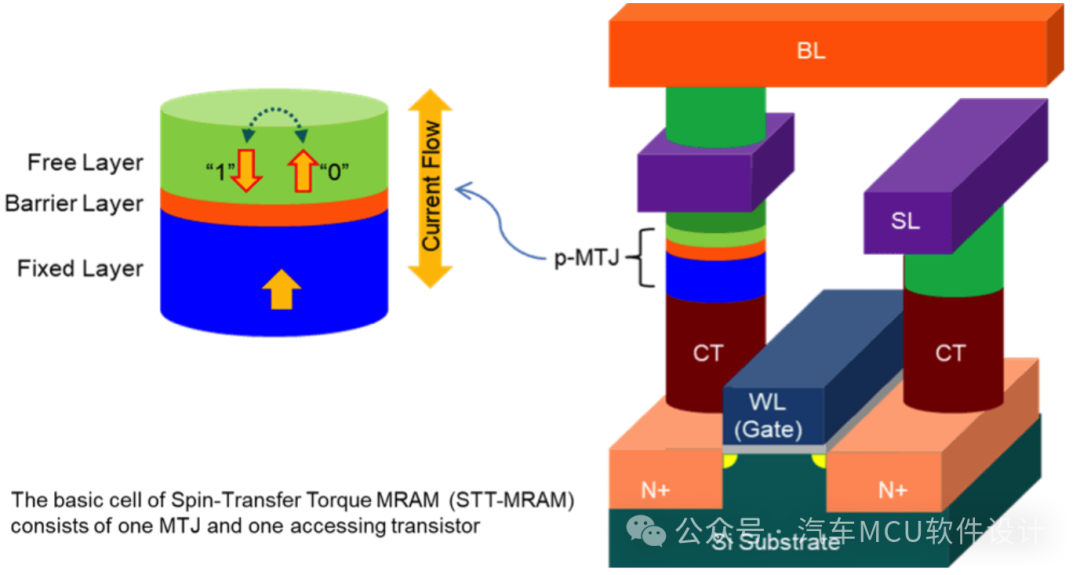

STT-MRAM的基本架构如下:

它使用MTJ(Magnetic Tunnel Junction --磁隧道结)存储信息,而不是传统的电荷存储方式。 每个MTJ包含两个铁磁层和一个隧道势垒层。其中一个铁磁层(Fixed Layer--蓝色)具有固定的磁性方向,而另一个铁磁层(Free Layer--绿色)可以通过外部电磁场或自旋传递转矩改变其磁性方向。如果两个铁磁层具有不同的方向,则MTJ电阻高,表明“逻辑1”状态。如果两层具有相同的方向,则MTJ电阻为低,表示“逻辑0”状态。 STT-MRAM通过将自旋极化电流直接穿过MTJ结构来改变自由层的磁方向,意味着使状态反转的阈值电流将随着MTJ的尺寸变小而减小。

3.2 ST专注PCM

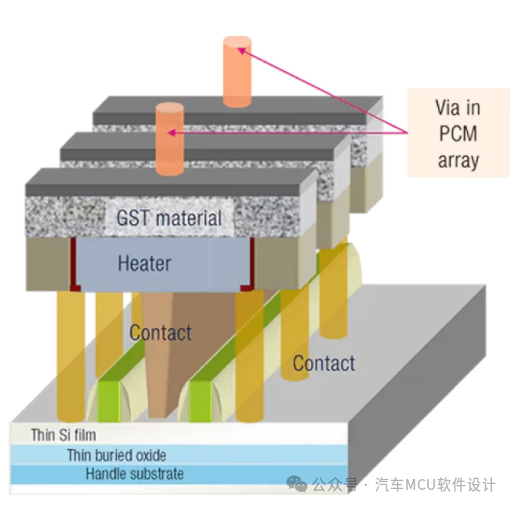

意法半导体的Stellar PG系列使用PCM技术作为eNVM解决方案,应用到了28nm FD-SOI技术平台。所谓PCM,就是相变材料在焦耳热作用下在结晶体态和非晶态下转换,从而呈现不同阻态。 ST的PCM技术采用锗锑碲 (GST) 合金制造而成,且在制造过程中利用了材料可在非晶态和结晶态之间进行快速热控制变化的物理特性,分别对应逻辑"0"和逻辑"1"相对应。具体来讲可通过非晶态(逻辑0)的高电阻和结晶态(逻辑1)的低电阻进行电气区分。PCM支持在低电压下进行读写操作,并且具备单比特位可变更性,因此相较于eFlash更有优势。

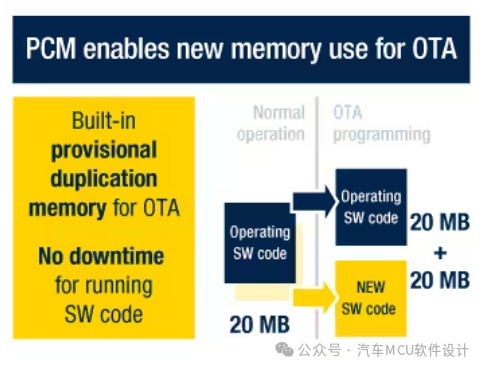

意法半导体在存储单元和GST合金上的专利布局,让其在汽车越来越多的OTA场景中抢占了先机,如下图:

3.3 英飞凌和台积电联手RRAM

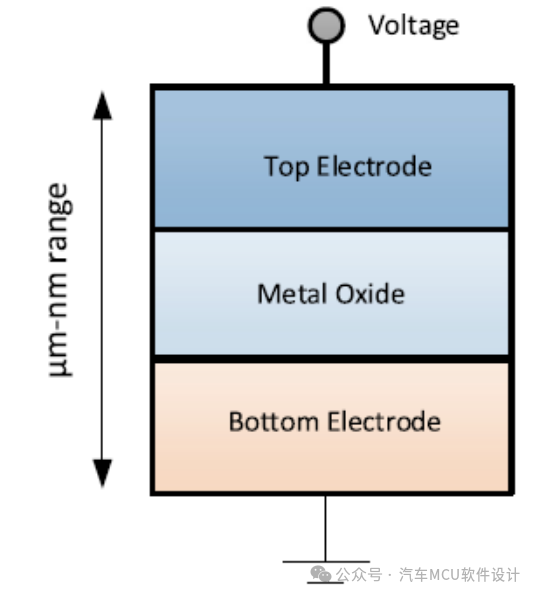

据英飞凌官网发布,TC4xx的NVM采用其与台积电联合研发的28nm RRAM技术。 RRAM(也称ReRAM),作为结构最简单的存储技术其结构看上去像一个三明治,绝缘介质层(阻变层)被夹在两层金属之间,形成由上、下电极和阻变层构成金属-介质层-金属(metal-insulator-metal,简称MIM)三层结构。

阻变原理是基于器件阻变层中导电通路(一般称之为conductive filament, 导电细丝)实现的,即通过在上、下电极施加不同的脉冲电压激励,使介质层发生阻变,产生物理性变化。 导电细丝会在阻变层中呈现导通或断开两种状态:非易失性的低阻态(Low Resistance State,LRS)或高阻态(High Resistance State,HRS),从而实现了“0”,“1”状态的区分和存储。

3.4 NXP如何计划eNVM

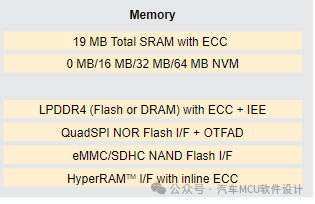

S32Z和S32E处理器采用TSMC 16nm FinFET技术实现。如下图:

目前还没有掌握到它这64MB的NvM采用什么技术。

4.小结

可以看到,eFlash制程工艺对MCU的架构和产品迭代影响是巨大的。而国内MCU厂商要想实现弯道超车,设计是一方面,生产、工艺则是重中之重。 就好像我想在空中修一栋房子,想法是好的,前提是生产建造技术要能够支撑我的想法。 兵马未动,粮草先行。而针对MCU的国产替代,我理解是设计未动,工艺先行。

审核编辑:黄飞

-

中国28nm制程会被美国卡脖子吗?2021-06-21 8403

-

汽车行业PCB测试程序2013-04-30 3698

-

汽车行业空调行业检漏用快速连接器2015-06-11 5919

-

如何利用28nm高端FPGA实现功耗和性能的平衡?2019-09-17 2922

-

请问C2000系列产品的制程是45nm还是28nm?2020-06-17 2167

-

为什么NOR FLASH仍是汽车行业的优选看了就知道2021-01-05 1630

-

28nm器件三大创新,Altera期待超越摩尔定律2010-02-05 1229

-

Chipworks拆解基于台积电28nm HPL工艺的赛灵思Kintex2017-02-11 3918

-

了解Altera公司28nm的DSP创新技术2018-06-22 5285

-

数据驱动变革——Tableau 赋能汽车行业2019-05-23 5441

-

汽车行业点胶加工中应用的工艺是怎么样的2020-07-13 1975

-

半导体制程发展:28nm向3nm的“大跃进”2020-10-15 7005

-

Omdia 研究报告,28nm 将在未来 5 年成为半导体应用的长节点制程工艺2020-12-03 3622

-

台积电和联华电子28nm工艺将满负荷运行2021-01-19 3318

-

基于28nm工艺制程的7系列FPGA2023-03-03 3514

全部0条评论

快来发表一下你的评论吧 !