开关电源噪声探源与静噪策略:外置MOS与集成MOS的比较研究

EMC/EMI设计

描述

在探讨如何消除开关电源的噪声之前,我们从源头开始了解一下开关电源的噪声是如何产生的,后续针对开关噪声以及DC-DC是外置MOS还是集成MOS两种类型确定静噪策略。

01

DC-DC的电流路径

首先,使用同步整流型降压DC/DC转换器的等效电路来了解一下开关电源电流的路径:

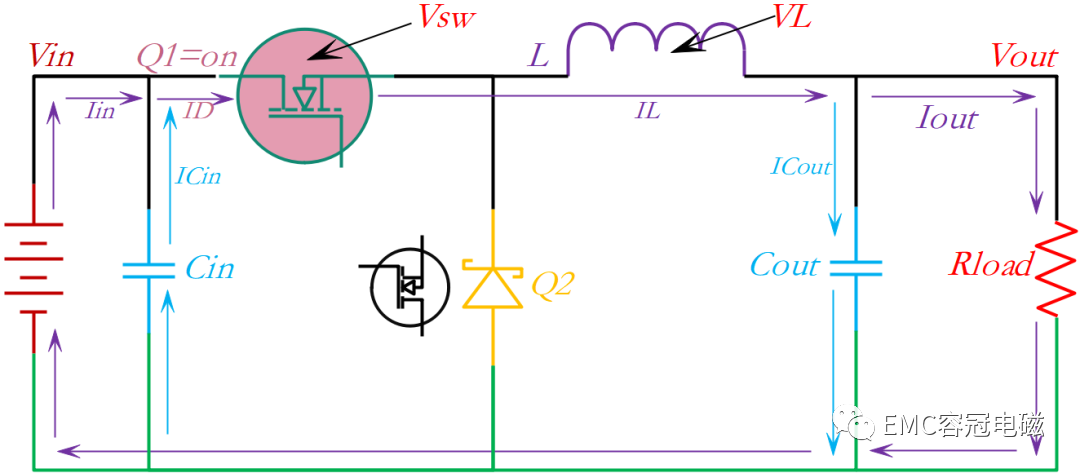

图1 Q1(高边开关)ON 时的电流路径

如图1所示,Q1为高边开关,Q2为低边开关。Q1导通时,此时Q2为关断状态,电流Iin路径是从输入电容器Cin(上阶段Cin已经充满电)到Q1、再经由电感L到输出电容器Cout和负载Rload。

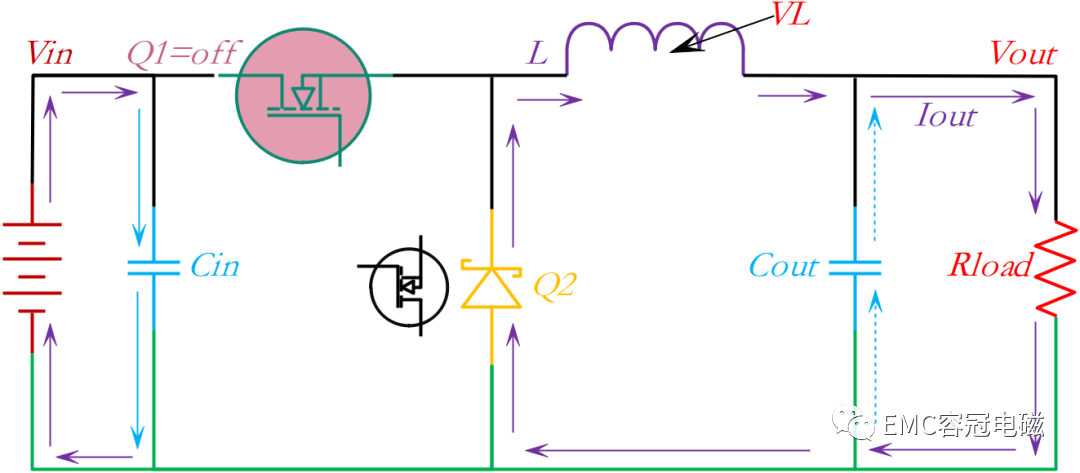

图2 Q2(低边开关)ON 时的电流路径

图2在Q2导通时,此时Q1为关断状态,Q1导通阶段Cout已经储满电量,Q1刚进入关断时,电感L其反向电动势维持输出电流Iout,而后电感能量减弱,Cout就会开始参与放电维持Iout,注意看电容蓝色电流虚线,电流路径是L经由负载Rload到Q2。

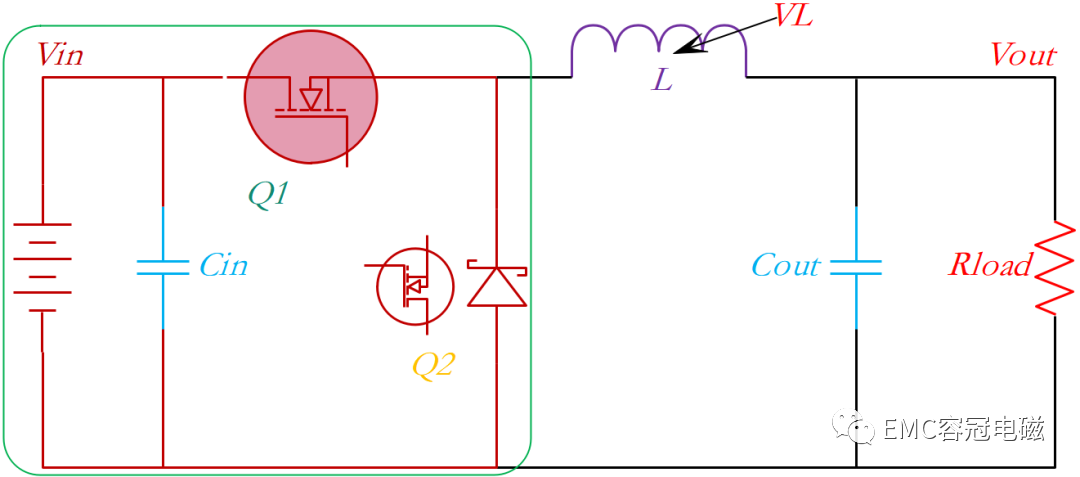

图3 图1和图2的电流路径差异

图3绿框表示图1和图2这些电流路径之间的差异,每当开关ON/OFF时,红色线路的电流都会急剧变化。该环路的电流变化非常剧烈,所以会因PCB布线的电感分量而在环路内产生高频振铃,产生的电压可通过下列公式来计算:

如果在电感分量为10nH的布线中1A电流在10ns内变化,则将产生1V电压。

02

DC-DC的寄生分量

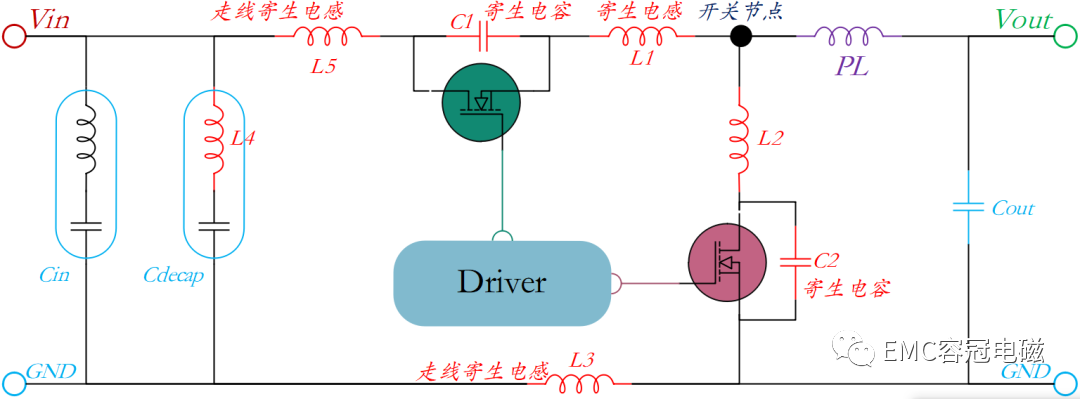

图4 电源电路的实装电路板的寄生分量

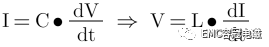

红色部分标出的是图4所表示的电流在急剧变化的环路中的寄生分量,布线中存在布线电感,通常每1mm有1nH左右的电感。另外,电容器中存在等效串联电感ESL,MOSFET的各引脚间存在寄生电容,而开关MOS的上升/下降时间是几ns。因此,如图5波形图所示,开关节点将产生100MHz~300MHz的振铃。所产生的电流和电压,可通过如下给出的两个公式求得。

图5 寄生分量和振铃之间的关系

红色波形是开关噪声分量,青色波形是基波分量,在上升/下降时出现100MHz至300MHz的强烈振铃。

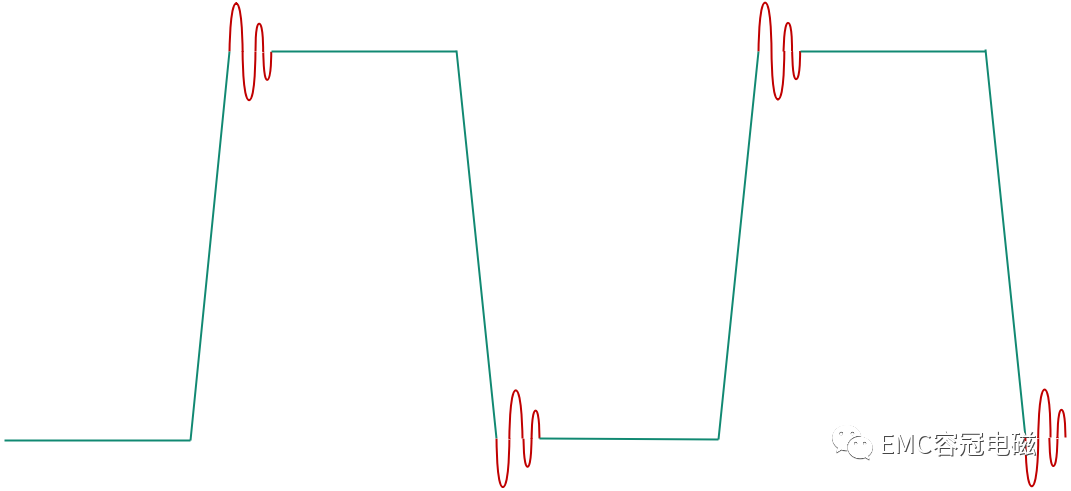

图6 开关电源电路产生的噪声

这种振铃会作为高频开关噪声带来各种影响,如图6,即使优化环路,残留的开关噪声成分也会作为共模噪声传导到电源端,必须采取措施,通过在传输线中插入电感器等高阻抗元件来限制噪声,还必须注意串扰。虽然有采取相应的措施,但由于无法从电源IC处去除安装电路板的寄生分量,因此只能通过PCB板布局设计及采用去藕电容来解决。

03

小结

① 在开关时会产生急剧电流ON/OFF的环路中,会因寄生分量产生高频振铃(=开关噪声)。

② 可通过优化PCB布线等做法来降低这种开关噪声,但即使这样,残留的噪声也会作为共模噪声传导至输入电源,因此需要采取措施防止噪声泄露。

审核编辑:黄飞

-

开关电源MOS管驱动电路的设计2022-09-15 5848

-

开关电源设计之MOS管驱动电路2023-05-04 3958

-

开关电源的噪声是如何产生的2023-08-30 2694

-

开关电源的mos管选择2017-04-09 3796

-

开关电源上的MOS管怎么选择2019-03-19 1653

-

MOS管开关电源损耗2021-10-29 2100

-

MOS管的驱动设计开关电源考虑的因素2022-01-03 2717

-

开关电源mos基础与功耗设计2021-09-24 1072

-

开关电源的MOS管的驱动2021-09-28 2538

-

开关电源MOS管如何选择,参数是核心2021-10-21 1777

-

开关电源IC耗散功率计算-KIA MOS管2023-02-06 3515

-

MOS管的工作原理 采用MOS管开关电源的电路设计2023-03-27 8972

-

开关电源常用mos管型号大全2023-08-18 27855

-

开关电源MOS管的主要损耗2024-08-07 5771

-

MOS管在开关电源中的应用及作用2024-11-05 3766

全部0条评论

快来发表一下你的评论吧 !