PCB工作地与金属外壳连接对ESD干扰影响的实例分析

PCB设计

描述

本文主要举例分析PCB工作地与金属外壳是否连接对ESD干扰的影响。

Part 1

现象描述

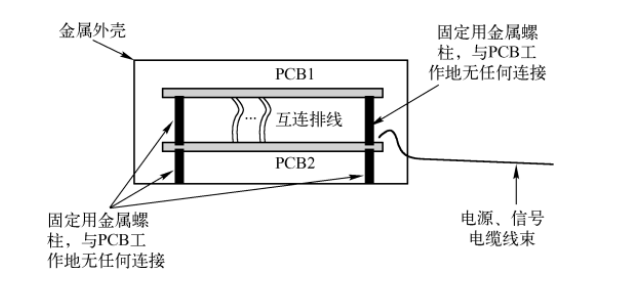

一个电子设备,其基本产品架构如下图所示。

图一 产品架构示意图

从上图可以看出:

该产品采用金属外壳。

内部有两块PCB, 这两块 PCB 通过螺柱固定在金属外壳上。

螺柱与PCB中的电路或工作地之间无任何连接。

PCB 之间采用排线进行信号交互。

PCB2 上还有一个 I/O 连接器, 与其互连的电缆中有电源信号、 输入/ 输出信号和其他控制信号。

该产品按照 ISO10605 标准规定的测试配置进行接触放电测试时, 发现测试电压只要高于±2 kV, 就会出现系统错误现象。

遇到ESD问题,大家不要慌张,ESD问题,基本上可以通过设备正确的接地来解决。

那这次我们的设备为什么会出现测试不过的现象呢?下面我们来详细的分析。

Part 2

原因分析

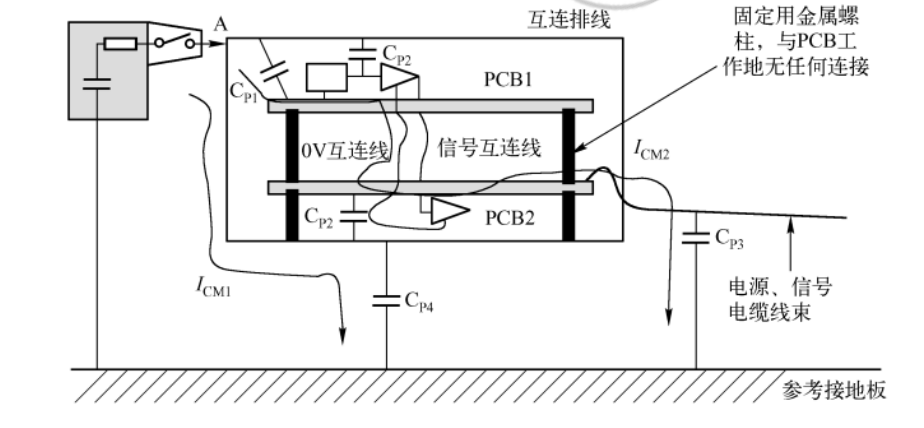

通过上面的产品架构,我们可以描绘出该产品在静电放电选在金属外壳上的ESD共模干扰路径,如下图所示:

图二 ESD 共模干扰路径分析图

图中有两条ESD共模干扰路径,即图中左边ICM1所在路径和右边ICM2路径。

很明显,第二条干扰路径才是ESD测试不通过的主要原因。

图中ICM2所在干扰路径,途径PCB1、PCB1与PCB2之间的互联排线、PCB2以及PCB2上的互联线缆。

这条干扰路径是一条“非期望”的路径,该路径中的干扰电流越大,意味着PCB受到的干扰就越大,出现问题的概率也越大。

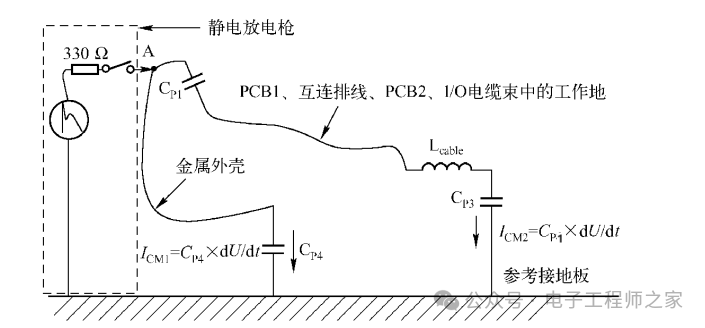

为了方便理解,我们可以简化其干扰路径,如下图所示:

图三 简化的等效电路图

CP1是产品金属外壳与 PCB1 地平面之间的寄生电容。

注:产品金属外壳与 PCB1 中的元器件、 印制线、 地平面、 电源平面都会产生寄生电容, 其中产品金属外壳与地平面、 电源平面的寄生电容最大,如10pF。

CP3是产品电缆线束与参考接地板之间的寄生电容。

在测试中,电缆线束一般放置在参考接地平面上, 并且离参考接地平面25mm, 此电容可以估算为60pF/m (ISO10605 标准规定电缆放置要求)。

本案例中电缆线束为2m, 故CP3可以估算为120pF。

CP4为产品金属外壳与参考接地板之间的寄生电容。

测试中该产品放置在参考接地平面上, 之间用相对介电常数小于1.4 的绝缘物隔离, 绝缘物的高度为 25mm, 此电容约为 30pF。

CP2是PCB2地平面与金属外壳之间的寄生电容。

在图中,CP2与CP4串联然后与CP3是并联, 而且 CP2<

因此可以看出 ESD 放电点 “A” 点相对于参考接地平面的电压不等于零 (当金属外壳良好接参考接地板时, “A” 点相对于参考接地平面的电压接近于零)。

在4kV接触放电测试时,A 点瞬态电压可达 1kV, 于是就造成了共模电流ICM2 ,共模电流的公式如下:

ICM2 =CP1 ×dU/dt = 10pF×1kV/1ns = 10 A

注: 在 ESD 干扰电流的频率下, 电缆 Lcable和 CP4造成的等效特性阻抗约为 150Ω 要远小于CP1的容抗。

对于 ESD 共模干扰电流 ICM2,我们可以做如下理解:

当发生静电放电时, 由于金属外壳上的放电点与参考接地板之间不可能做到等电位 (这需要金属外壳和参考接地板之间的阻抗为零,显然这是不可能的,接地产品会好一些)。

这就使得 A 点的电位不为零, 最终导致在 PCB1 、 PCB1 与 PCB2 之间的互连线、 PCB2 及电缆注入了一个 ESD 干扰共模电流 ICM2 。

ICM2主要流经 PCB1 中的 0V 工作地, PCB1 与 PCB2 之间的互连线上的 0V 工作地 、 PCB2 中的 0V 工作地, 以及电缆束上的 0V 工作地 (因为 0V 工作地所在的路径阻抗最小)。

ICM2 , 是由一个相对于参考接地板的共模 ESD 电压造成的, 它还不是直接影响电路工作的电流, 因为它是共模电流。

而产品内部电路之间传递的是电压信号, 而且这种传递的电压信号为芯片或电路端口与 0V 工作地之间的电压, 即差模的电压信号。

要使这种共模电流或共模电压影响产品中以差模电压传递的电路信号正常工作, 就必须发生转化。

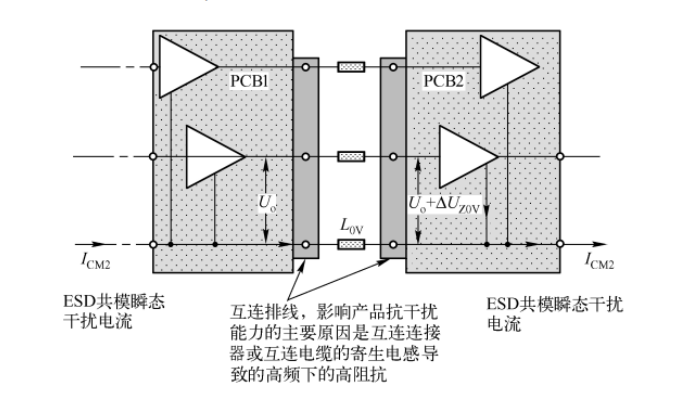

下图就是 ESD 共模瞬态电流流过互连连接器时的公共阻抗耦合原理。

图四 公共阻抗耦合原理

图中给出了这种转化的原理, 其中 UO 是 PCB1 与 PCB2 之间传递的正常工作电压信号。

当没有 ESD 共模干扰电流流过互连排线时,UO 正常地从 PCB1 传递到 PCB2。

但是, 当 ESD 共模电流流过其中的 0V 地时, 由于 PCB1 与 PCB2 之间的互连线实际存在寄生电感 L ( 约 10nH /cm), ESD 共模电流就会在其两端感应出电压,这个电压计算公式如下:

ΔUZ0V = | L0V ×dICM2 / dt |

假设PCB1 与 PCB2 之间的排线长约10 cm, 寄生电感估算为 100 nH。对于的感应电压为:

ΔUZ0V = | LdICM2/dt | = 100nH×4A/1ns = 400V

这个电压已经远远超过了电路本身的电压噪声容限。 因此,就出现了前面提到的出现系统错误的现象。

对该问题的剩余分析、处理措施以及得到的启示,详见后面文章《EMC测试案例分析——PCB工作地与金属外壳是否连接对ESD干扰的影响《二》》

审核编辑:黄飞

-

压接式N头使用金属外壳的主要原因2024-10-29 991

-

开关电源金属外壳触摸手麻原因分析2024-08-14 2599

-

电气设备的金属外壳接地是什么接地2024-06-06 14220

-

金属外壳的工业连接器在性能上有哪些独特之处?2023-08-19 2437

-

PCB板子的地和产品金属外壳的如何连接?2023-06-29 4746

-

PCB板的两种接地方式2022-04-09 9264

-

金属外壳与电路板的接地问题2021-01-12 21853

-

分析塑料外壳连接器和金属外壳连接器对ESD测试的影响2020-07-30 3212

-

塑料外壳与金属外壳连接器对ESD的影响分析2020-01-28 5627

-

关于PCB上DB9公头的金属外壳如何处理之疑问2017-01-22 7389

-

解惑高级PCB-EMC问题2016-08-23 5233

-

接近开关的金属外壳对自身造成干扰,怎么办?2016-04-25 18569

-

金属外壳对蓝牙模块有影响吗?2014-05-14 11227

-

金属外壳的电源如何接地2011-03-10 7087

全部0条评论

快来发表一下你的评论吧 !