高速背板的电磁兼容性设计要点

EMC/EMI设计

描述

1 高速背板的分层

高速背板为实现较好的电磁兼容性设计,使得印制板在正常工作时能满足电磁兼容和敏感度标准。正确的堆叠有助于屏蔽和抑制EMI。

多层印制板的电磁兼容分析可以基于克希霍夫定律和法拉第电磁感应定律。

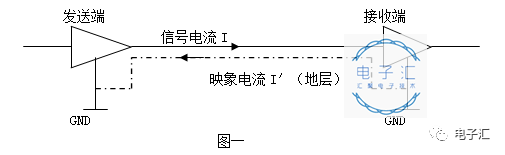

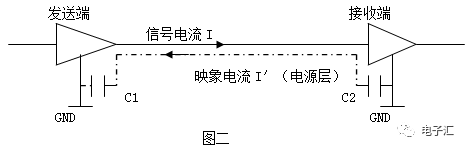

根据克希霍夫定律,任何时域信号由源到负载的传输都必须有一个最低阻抗的路径。见图一。图中I=I′,大小相等,方向相反。图中I我们称为信号电流,I′称为映象电流,而I′所在的层我们称为映象平面层。如果信号电流下方是电源层(POWER),此时的映象电流回路是通过电容耦合所达到的。见图二。

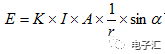

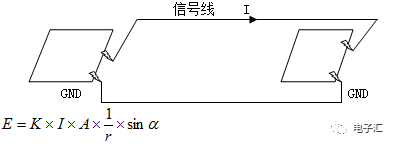

根据法拉第电磁感应定律。

可以得出当A越大时,E值越大。见图三

根据以上两个定律,我们得出在多层印制板分层及堆叠中应遵徇以下基本原则;

① 电源平面应尽量靠近接地平面,并应在接地平面之下。

② 布线层应安排与映象平面层相邻。

③ 电源与地层阻抗最低。其中电源阻抗Z0=其中D为电源平面同地平面之间的间距。W为平面之间的面积。

④ 在中间层形成带状线,表面形成微带线。两者特性不同。

重要信号线应紧临地层。

① 六层板

表二

| 第一层 | 第二层 | 第三层 | 第四层 | 第五层 | 第六层 | |

| A | S1 | GND | S2 | S3 | POWER | S4 |

| B | S1 | S2 | GND | POWER | S3 | S4 |

| C | S1 | GND | S2 | POWER | GND | S3 |

| D | GND | S1 | POWER | GND | S2 | GND |

在背板设计中推荐D种情况,在六层板中,它的EMI性能最优。

② 八层板

表三

| 第一层 | 第二层 | 第三层 | 第四层 | 第五层 | 第六层 | 第七层 | 第八层 | |

| A | S1 | S2 | S3 | GND | POWER | S4 | S5 | S6 |

| B | S1 | GND | S2 | S3 | S4 | S5 | POWER | S6 |

| C | S1 | GND | S2 | S3 | GND | POWER | S4 | S5 |

| D | S1 | GND | S2 | GND | S3 | POWER | S4 | S5 |

| E | S1 | GND | S2 | GND | POWER | S3 | GND | S4 |

八层板,如果是5个信号层,以D种情况为最好。在这种情况中,S1,S2,S3都是比较好的布线层。同时电源平面阻抗也比较低。如果是4个信号层,以表三中E种情况为最好。每个信号层都是良好布线层。在这几种情况中,相邻信号层应布线。

③ 十层板

表四

| 第一层 | 第二层 | 第三层 | 第四层 | 第五层 | 第六层 | 第七层 | 第八层 | 第九层 | 第十层 | |

| A | S1 | GND | S2 | S3 | GND | POWER | S4 | S5 | GND | S6 |

| B | S1 | GND | S2 | GND | S3 | GND | POWER | S4 | GND | S5 |

| C | S1 | GND | S2 | S3 | GND | POWER | S4 | GND | S5 | GND |

| D | GND | S1 | S2 | GND | S3 | S4 | GND | POWER | S5 | GND |

十层板中C、D一般用于背板。其中D种情况对EMC的屏蔽作用要好于C。不足之处是在于两信号层相接,在布线上要注意。

总之,PCB的分层及叠层是一个比较复杂的事情。有多方面的因素要考虑。

2 高速背板的布线

高速信号的布线主要是考虑信号的完整性,即延迟、反射、串扰、同步切换噪声(SSN)和电磁兼容性(EMI)。

2.1 时钟信号线

时钟信号线既要考虑信号完整性问题,又要考虑EMI问题。它的处理对高速背板性能的优劣。

时钟信号线在背板中一般走在内层,最好夹在两个平面层之间进行走线,走线的阻抗须进行控制,在不同层切换时保证阻抗的一致性,以防信号反射对时钟的影响。

信号线之间,信号线与其它线的线距最少满足3W原则,可以有效预防由时钟线引起的串扰,信号线之间若有同步时序要求,布线设计时应等长,防止走线的延迟对同步时序的影响。

2.2 高速数据信号线

高速信号线主要考虑信号完整性问题,即阻抗控制、反射、串扰等因素。

高速信号线在背板中一般走在内层,并与地平面层相临之间进行走线,走线的阻抗须进行控制,在不同层切换时保证阻抗的一致性,以防阻抗失配引起信号反射,对数据线形成过冲及振铃,影响数据的可靠性。

高速信号线与其它线的线距最少满足2W原则,布线条件较宽裕的应满足3W原则,这样可以有效预防由数据线相互的串扰,保证数据的可靠性。并行数据信号线之间要满足同步时序要求,布线设计时应完全等长,防止走线的延迟对数据线同步时序的影响。

2.3 LVDS布线

边沿速率(Edge Rate):对于Multi-Point方式的背板总线结构通常使用NESA(North East SystemsAssociates,Inc)公司的TDR(Time Domain Reflectometry)分析法来描述信号的边沿速率(EdgeRate)的影响。信号的跃变时间(上升和下降时间)对于传输线的计算是一个很重要的指标,需要注意的是当信号的边沿速率(EdgeRate)小于300ps时,Multi-Point和Multi-Drop方式的总线结构是不能使用的。

Stub长度:Stub长度对背板总线的影响一般也是用NESA公司提出的TDR和TDT(Time Domain Transmission)”Passive Signal Integrity”方法来衡量。一般的结论是Stub长度越长,线路上的阻抗不连续性越严重,线路上的阻抗不连续性越严重,在信号的上升沿和下降沿的阻尼振荡的幅度越大。因此单板上的Stub长度越短,对背板总线的影响就越小。

接口器件的放置:为了减少Stub长度对背板上的传输线的影响,应当尽量缩短Stub长度。因此在单板的布局时,应当首先决定接口器件的位置,以保证有最短的Stub长度。要把总线收发器(Multi-Point方式)或接收器(Multi-Drop方式)放置在连接器的附近,而且越近越好,最好采用双面放置,以减少Stub长度。

差分阻抗:BLVDS要求在一对差分线之间要有100欧姆的差分阻抗。两对差分线间如果能保证有20mil的间距,彼此之间的共模和差模干扰就可以忽略不计。一对差分线之间的距离越近,其对外的辐射干扰就越少,外部对这对差分线的干扰反映在接收端的差模分量就越少,共模分量就越大,这对于接收器显然是有好处的。如果用W表示走线的宽度,d表示层间电解质的厚度,l表示一对差分线之间的距离,L表示差分线对之间的距离。那么,线宽W越宽,PCB板的特性阻抗越容易加工的准确,背板上的线宽一般选择12mil;层间电解质的厚度d一般不能选的太小,d值越小,特性阻抗就越低,背板上信号层之间或信号层与地线层之间的电解质厚度不能小于13mil:一对差分线信号内相互之间的间距l的选择至少要大于d,一般当d选择13mil时,l至少要大于18mil;差分线对之间的间距L的选择一般要大于两倍的l值。

总线的终止:对于Multi-Point方式的总线,其两端都要有一个匹配电阻。对于Multi-Drop方式的总线,要根据驱动器的位置不同用一个或两个匹配电阻。电阻的阻值应当与线路加载后的有效阻抗相一致。一般的原则是匹配电阻要选的比实际的有效电阻大一些,而不要小于实际的有效电阻,这样做的原因是选的大一些只能带来反射方面的不利因素,选的小了还会造成信号的幅度变小的弊病。

Stub的终止:在靠近连接器管脚处的LVDS差分信号线对的每根信号线上串联一个15到30欧姆的电阻,如图 1所示,对边沿速率(Edge Rate)能起到滤波的作用,这能有效地抑制Stub和边沿速率(Edge Rate)造成的阻尼振荡,也可以在差分接收器的两个输入端跨接一个小的电容来实现,但是电容的大小很难掌握,一般多用电阻来实现,而且这种做法只适用于Multi-Drop方式的连线。如果你处理的是边沿速率很快的并且Stub长度较长的Multi-Drop方式的连线,这种串接电阻的方法很有效。

连接器及其管脚分配:连接器的选择是根据不同的应用而定的,一般考虑的因素有信号管脚的的数目、机械尺寸要求、电气性能要求、管脚排列要求等。一般来讲,连接器每排的管脚数越少越好。并且对于多数连接器,一对差分信号应当尽量放置在一排内,以保证具有相同的走线长度。其它的TTL/CMOS信号应当与LVDS信号隔开,以避免相互的辐射干扰。对于电源与地线应当采用特殊针长的引脚,以保证上电顺序。通常上电的顺序是地线、电源线、I/O线。下电顺序正好相反,是I/O线、电源线、地线。

线对的平衡:当差分线对之间不平衡时,就会引入共模噪声。控制共模噪声的最好方法是使差分线对的两根线尽量在长度上相等、再走线方式上一致、两根线之间的间距尽量保持一致,从而使两根线之间处于平衡状态。另外,一对差分线中的两根信号线之间的长度不同时,除了会造成skew外,还会在接收端造成抖动,这两点都是要时时注意的。还有一点要注意的是,一个信号线的总长度要尽量避免等于信号波长四分之一的整数倍的情况。

2.4 基于信号完整性分析的PCB设计方法

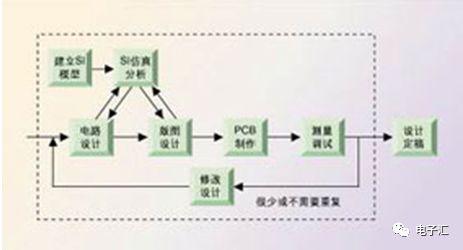

高速背板布线推荐采用基于信号完整性分析的PCB设计方法,它的设计流程如下:

在PCB板设计之前,首先建立高速数字信号传输的信号完整性模型。

根据SI模型对信号完整性问题进行一系列的预分析,根据仿真计算的结果选择合适的元器件类型、参数和电路拓扑结构,作为电路设计的依据。

在电路的设计过程中,将设计方案送交SI模型进行信号完整性分析,并综合元器件和PCB板参数的公差范围、PCB版图设计中可能的拓扑结构和参数变化等因素,计算分析设计方案的解空间。

在电路设计完成后,各高速数字信号应该都具有一个连续的、可实现的解空间。即当PCB及元器件参数在一定的范围内变化、元器件在PCB板上的布局以及信号线在PCB板上的布线方式具有一定的灵活性的情况下,仍然能够保证对信号完整性的要求。

PCB版图设计开始之前,将获得的各信号解空间的边界值作为版图设计的约束条件,以此作为PCB版图布局、布线的设计依据。

在PCB版图设计过程中,将部分完成或全部完成的设计送回SI模型进行设计后的信号完整性分析,以确认实际的版图设计是否符合预计的信号完整性要求。若仿真结果不能满足要求,则需修改版图设计甚至电路设计,这样可以降低因设计不当而导致产品失败的风险。

在PCB设计完成后,就可以进行PCB板制作。PCB板制造参数的公差范围应在信号完整性分析的解空间的范围之内。

当PCB板制造好后,再用仪器进行测量调试,以验证SI模型及SI分析的正确性,并以此作为修正模型的依据。

在SI模型以及分析方法正确的基础上,通常PCB板不需要或只需要很少的重复修改设计及制作就能够最终定稿,从而可以缩短产品开发周期,降低开发成本。

2.5高速背板布局及材料

高速背板布局时应遵循“模拟、数字区域分开”,“高速、中速、低速区域分开”的布局原则,防止模数干扰及信号之间的串扰。接插件的竖排针上应多定义地,即可给信号最短路径回流,又可防止信号的串扰。背板上对模拟地、数字地的处理一般遵循“分区不分割”的原则,模拟信号、数字信号分别在相应区域布线,无联系的信号线不跨区布线。

高速背板根据信号实际的带宽,须采用符合要求的高速连接件,如MOLEX公司的VHDM系列接插件,可满足3.125G以上要求。接插件须考虑降额设计。

审核编辑:黄飞

-

高速PCB的信号完整性、电源完整性和电磁兼容性研究2024-09-19 1186

-

PCB板层设计与电磁兼容性有什么关系?2022-02-09 919

-

开关电源的PCB电磁兼容设计要点分析2021-07-26 1819

-

如何确保满足电磁兼容性的要求?2021-05-13 2075

-

怎样去设计高速电路的电磁兼容性?2021-04-26 2183

-

电磁兼容与电磁兼容性有什么区别2020-07-28 3714

-

PCB布线对电磁兼容性的影响2020-04-13 2219

-

怎么提高电磁兼容性2019-05-31 1934

-

一文看懂电磁兼容性原理与方法及设计2018-04-03 36589

-

手机PCB的电磁兼容性设计2016-11-24 1823

-

电磁兼容性分析的方法2016-08-25 5542

-

高速混合PCB板的电磁兼容性设计2010-08-12 672

-

通信开关电源的电磁兼容性2009-07-16 895

全部0条评论

快来发表一下你的评论吧 !