【ALINX 技术分享】AMD Versal AI Edge 自适应计算加速平台之 Versal 介绍(2)

电子说

描述

Versal 介绍

Versal 包含了 Cortex-A72 处理器和 Cortex-R5 处理器,PL 端可编程逻辑部分,PMC 平台管理控制器,AI Engine 等模块,与以往的 ZYNQ 7000 和 MPSoC 不同,Versal 内部是通过 NoC 片上网络进行互联。

Versal 芯片的总体框图

Versal 芯片的总体框图

PS: 处理系统 (Processing System) , 就是与 FPGA 无关的 ARM 的 SoC 的部分。

PL: 可编程逻辑 (Progarmmable Logic), 就是 FPGA 部分。

NoC 架构

Versal 可编程片上网络(NoC) 是一种 AXI 互连网络,用于在可编程逻辑 PL,处理器系统 PS 等之间共享数据,而之前的 Versal 系列采用的 AXI 交叉互联模块,这是 Versal 的不同之处。

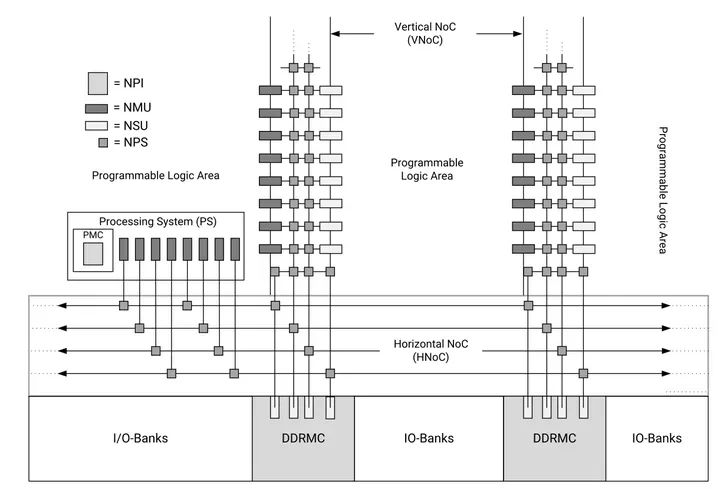

NoC 是为可扩展性而设计的。它由一系列相互连接的水平(HNoC)和垂直(VNoC)路径,由一组可定制的硬件实现组件支持,这些组件可以以不同的方式进行配置,以满足设计时序、速度和逻辑利用率要求。以下是 NoC 的结构图

NoC 的结构图

从 NoC 的结构图,可以看到,其主要由 NMU(NoC master units),NSU(NoC slave units),NPI(NoC programming interface),NPS(NoC packet switch)组成。PS 端可以连接到 NMU,再通过 NPS 连接访问到 DDRMC,同样 PL 端也可以通过 NMU,NPS 访问到 DDRMC。通过 NPS 路由的方式,灵活地访问各模块。

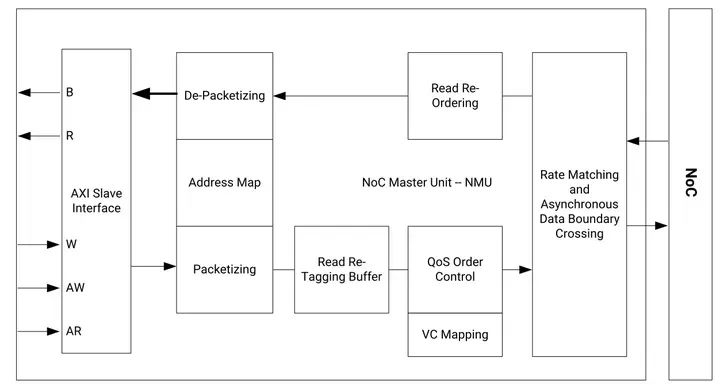

NMU 结构

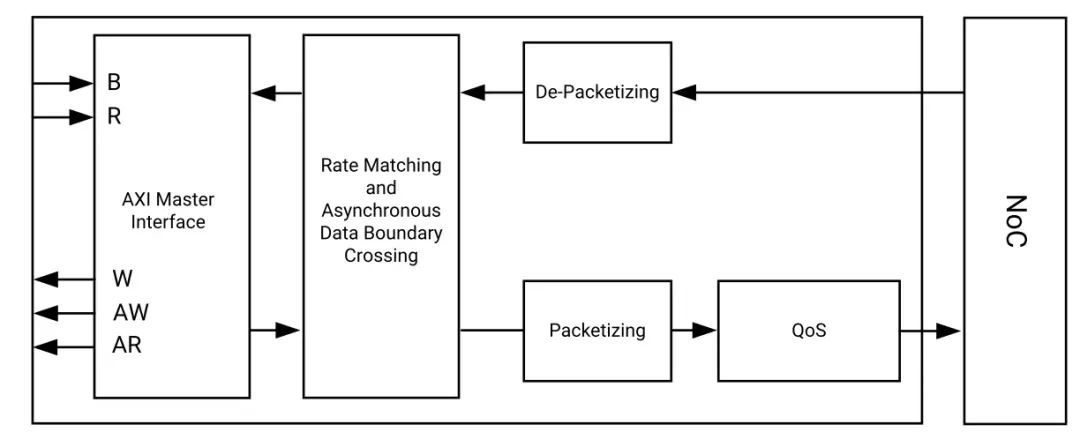

NSU 结构

从以上的 NMU, NSU 结构可以看到,对用户的接口仍然是 AXI 总线,在其内部,将 AXI 数据进行组包或解包,连接到 NoC 网络。

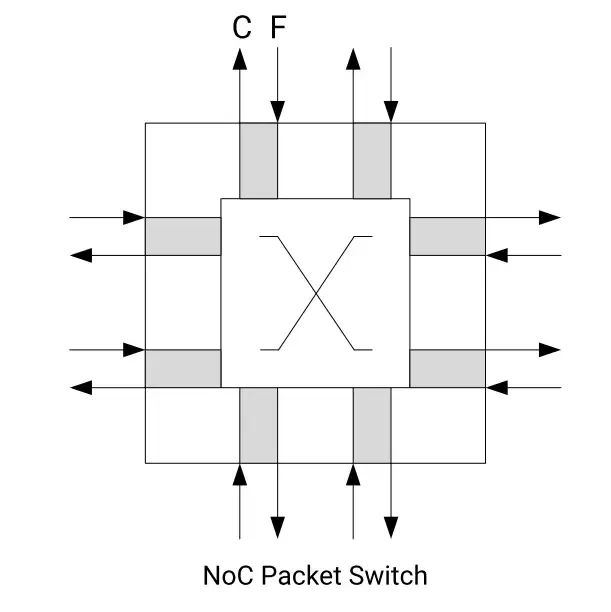

NPS 结构

而 NMU 和 NSU 都是连接到 NPS 上的,它相当于一个路由器,将数据转发给目的设备。它是一个全双工的 4x4 switch,每个端口在每个方向支持 8 个虚拟通道,采用基于信用的流控,类似于 TCP 的滑动窗口。

NoC 是 Versal 开发中非常重要的部件,PS 端访问 DDR,PL 端访问 DDR 都是通过 NoC,与 Versal 不同的是,versal 在 PS 端没有 DDR 控制器,都是通过 NoC 访问,因此了解 NoC 结构是很有必要的,更多的内容可以参考官方的 pg313 文档。

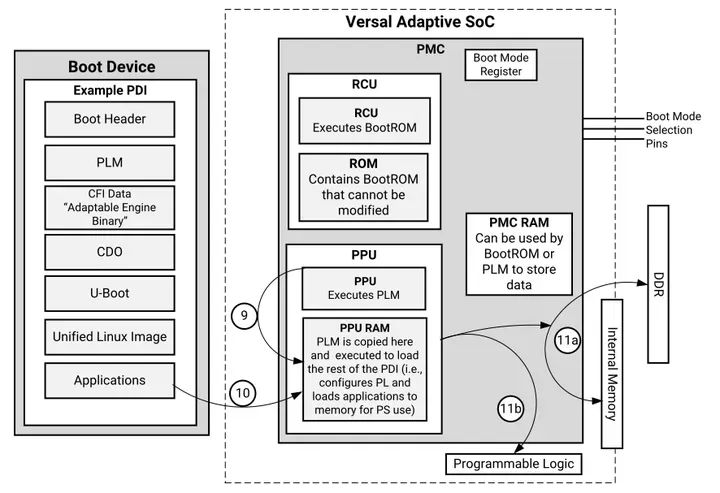

PMC 架构

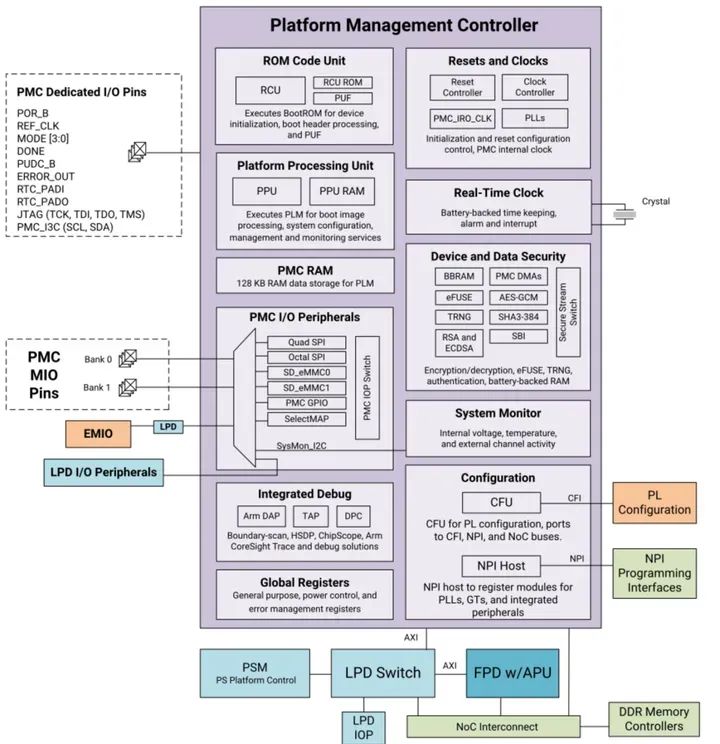

PMC(平台管理控制器)在启动,配置,运行时做平台的管理。从下图的结构图中可以看出,PMC 由 ROM Code Unit,Platform Processing Unit,PMC I/O Peripherals 等单元组成,功能丰富。在这里主要介绍一下 PMC 是如何引导程序启动的。

PMC 结构图

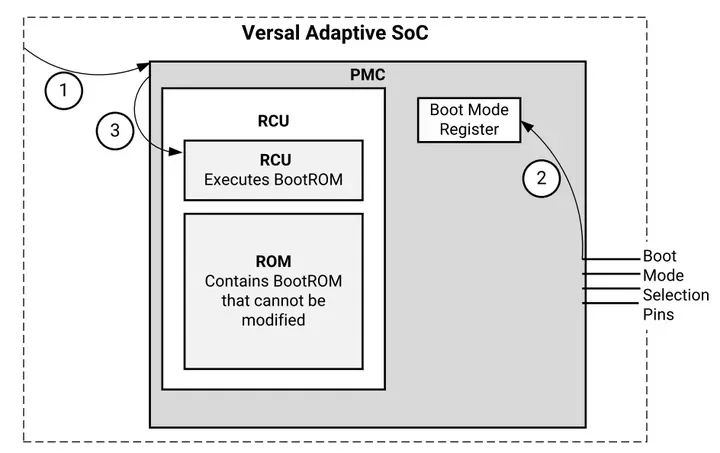

第一阶段:Pre-Boot

PMC 检测 PMC 电源和 POR_B 释放

2. PMC 读取启动模式引脚并存入 boot mode 寄存器

3. PMC 发送复位给 RCU(ROM code unit)

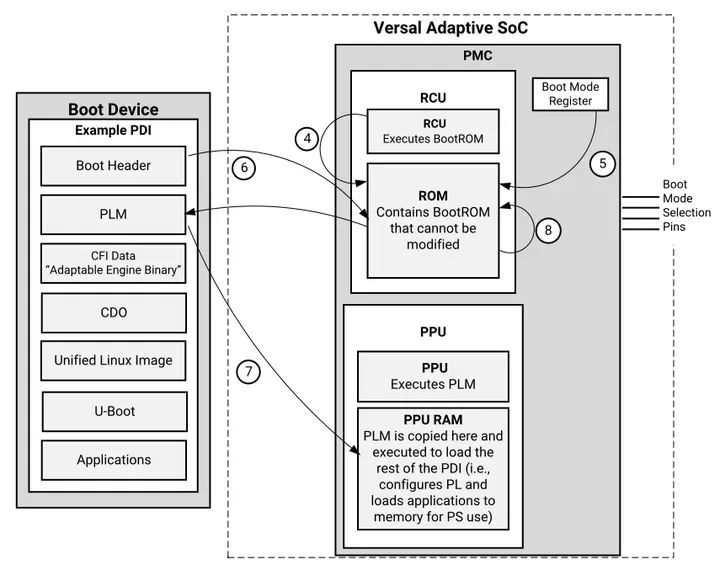

第二阶段:Boot Setup

4. RCU 从 RCU ROM 中执行 BootROM

5. BootROM 读出 boot mode 寄存器,选择启动设备

6. BootROM 从启动设备读取 PDI(programmable device image) 并校验

7. BootROM 释放 PPU 的复位,将 PLM 加载到 PPU RAM 并校验。校验后,PPU 唤醒,PLM 软件开始执行。

8. BootROM 进入睡眠状态

第三阶段:Load Platform

9. PPU 开始从 PPU RAM 中执行 PLM

10. PLM 开始读取并运行 PDI 模块

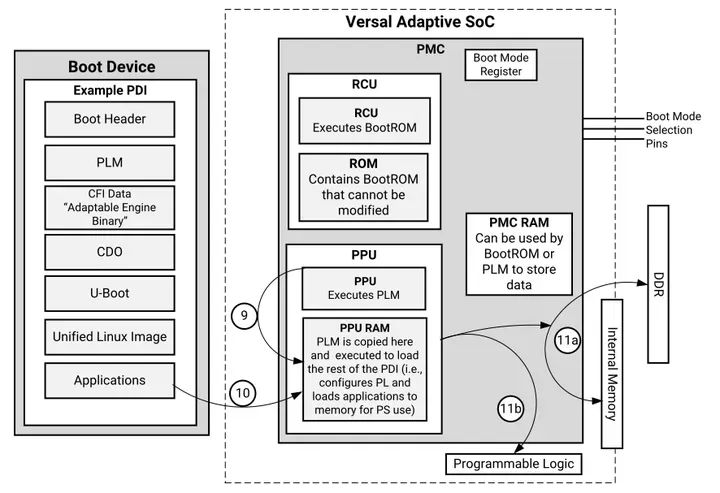

11. PLM 利用 PDI 内容配置 Versal 其他部分

11a: PLM 为以下模块配置数据:PMC, PS clocks

(MIO ,clocks, resets 等)(CDO 文件)

NoC 初始化和 NPI 模块(DDR 控制器,NoC,

GT,XPIPE,I/Os,clocking 和其他 NPI 模块

PLM 加载 APU 和 RPU 的应用程序 ELF 到存储空间,

如 DDR,OCM,TCM 等

11b: PL 端逻辑配置

PL 端数据(CFI 文件)

AI Engine 配置(AI Engine CDO)

第四阶段:Post-Boot

12. PLM 继续运行,直到下一次 POR 或系统复位。并负责 DFX 重配置,电源管理,子系统重启,错误管理,安全服务。

Versal 芯片开发流程的简介

由于 Versal 将 CPU 与 FPGA 集成在了一起,开发人员既需要设计 ARM 的操作系统应用程序和设备的驱动程序,又需要设计 FPGA 部分的硬件逻辑设计。开发中既要了解 Linux 操作系统,系统的构架,也需要搭建一个 FPGA 和 ARM 系统之间的硬件设计平台。所以 Versal 的开发是需要软件人员和硬件硬件人员协同设计并开发的。这既是 Versal 开发中所谓的 " 软硬件协同设计”。

Versal 系统的硬件系统和软件系统的设计和开发需要用到一下的开发环境和调试工具:Xilinx Vivado。Vivado 设计套件实现 FPGA 部分的设计和开发,管脚和时序的约束,编译和仿真,实现 RTL 到比特流的设计流程。

Xilinx Vitis 是 Xilinx 软件开发套件 (SDK), 在 Vivado 硬件系统的基础上,系统会自动配置一些重要参数,其中包括工具和库路径、编译器选项、JTAG 和闪存设置,调试器连接已经裸机板支持包 (BSP)。SDK 也为所有支持的 Xilinx IP 硬核提供了驱动程序。Vitis 支持 IP 硬核(FPGA 上)和处理器软件协同调试,我们可以使用高级 C 或 C++ 语言来开发和调试 ARM 和 FPGA 系统,测试硬件系统是否工作正常。Vitis 软件也是 Vivado 软件自带的,无需单独安装。

Versal 的开发也是先硬件后软件的方法。具体流程如下:

在 Vivado 上新建工程,增加一个嵌入式的源文件。

在 Vivado 里添加和配置 PS 和 PL 部分基本的外设,或需要添加自定义的外设。

在 Vivado 里生成顶层 HDL 文件,并添加约束文件。再编译生成比特流文件(*.pdi)。

导出硬件信息到 Vitis 软件开发环境,在 Vitis 环境里可以编写一些调试软件验证硬件和软件,结合比特流文件单独调试 Versal 系统。

在 VMware 虚拟机里生成 u-boot.elf、 bootloader 镜像。

在 Vitis 里将比特流文件和 u-boot.elf 文件生成一个 BOOT.pdi 文件。

在 VMware 里生成 Ubuntu 的内核镜像文件 Zimage 和 Ubuntu 的根文件系统。另外还需要要对 FPGA 自定义的 IP 编写驱动。

把 BOOT、内核、设备树、根文件系统文件放入到 SD 卡中,启动开发板电源,Linux 操作系统会从 SD 卡里启动。

学习 Versal 要具备哪些技能

学习 Versal 比学习 FPGA、MCU、ARM 等传统工具开发要求更高,想学好 Versal 也不是一蹴而就的事情。

软件开发人员

计算机组成原理

C、C++ 语言

计算机操作系统

tcl 脚本

良好的英语阅读基础

逻辑开发人员

计算机组成原理

C 语言

数字电路基础

访问ALINX官网了解 Versal AI Edge 自适应计算加速平台更多详情。

如需购买 Versal AI Edge 自适应计算加速平台 SOM 及配套开发板,请登录天猫或京东:ALINX旗舰店。

ALINX | AUMO 智能车载

芯驿电子科技(上海)有限公司

芯驿电子科技(上海)有限公司,成立于 2012 年,总部位于上海松江临港科技城,高新技术企业、上海市专精特新企业,是一家车载智能产品和 FPGA 技术方案公司,拥有 “AUMO” 和 “ALINX” 两大品牌,先后获得国家级科技型中小企业认定、上海市创新型中小企业认证、ISO9001 质量体系认证等。

AUMO 品牌专注车载智能产品,提供一站式自动驾驶硬件在环仿真 HIL、电子后视镜 CMS 产品及方案,与多家车载自动驾驶客户已开展深度合作;ALINX 品牌专注于 FPGA 产品和方案定制,是全球 FPGA 芯片龙头企业 AMD/XILINX 官方合作伙伴,国内 FPGA 芯片龙头企业紫光同创官方合作伙伴,同时作为百度 AI 合作伙伴,为百度定制了国产 AI 飞桨系统的 Edgeboard 系列边缘设备。经历十余年发展,公司产品已经远销海外 30 多个国家,服务数千家企业客户。

业务范围

主要聚焦于 FPGA 行业解决方案,自动驾驶 HIL、FPGA 国产化,FPGA SOM 开发套件。

应用领域

公司涉及的行业解决方案涉及人工智能、自动驾驶、医疗成像、智能制造、数据中心、交通电力、5G 通信、机器视觉、工业互联、仪器仪表、IC 测试等行业。

审核编辑 黄宇

-

AMD Versal AI Edge自适应计算加速平台之Versal介绍(2)2024-03-06 2969

-

【ALINX 技术分享】AMD Versal AI Edge 自适应计算加速平台之准备工作(1)2024-03-07 1985

-

AMD Versal AI Edge自适应计算加速平台PL LED实验(3)2024-03-13 1995

-

AMD Versal AI Edge自适应计算加速平台之PL LED实验(3)2024-03-22 14731

-

在Vivado中构建AMD Versal可扩展嵌入式平台示例设计流程2024-04-09 3260

-

AMD Versal自适应SoC内置自校准的工作原理2025-10-21 4356

-

Xilinx推出Versal:业界首款自适应计算加速平台,支持快速创新2018-10-18 2226

-

赛灵思发布自适应计算加速平台芯片系列Versal2018-10-22 6595

-

赛灵思Versal自适应计算加速平台助于高效实现设计目标2021-05-27 2763

-

赛灵思Versal自适应计算加速平台指南2021-10-11 5399

-

Versal启动文件简述2023-07-07 2260

-

Versal:首款自适应计算加速平台(ACAP)2023-09-18 686

-

AMD发布第二代Versal自适应SoC,AI嵌入式领域再提速2024-04-11 1794

-

ALINX VERSAL SOM产品介绍2024-08-05 1966

-

面向AI与机器学习应用的开发平台 AMD/Xilinx Versal™ AI Edge VEK2802025-04-11 2790

全部0条评论

快来发表一下你的评论吧 !