化学镀镍钯金电路板金丝键合可靠性分析

描述

共读好书

张路非,闫军政,刘理想,王芝兵,吴美丽,李毅

(贵州振华群英电器有限公司)

摘要:

在微组装工艺应用领域,为保证印制电路板上裸芯片键合后的产品可靠性,采用化学镀镍钯金工艺(ENEPIG),可在焊接时避免“金脆”问题、金丝键合时避免“黑焊盘”问题。针对化学镀镍钯金电路板的金丝键合(球焊)可靠性进行了研究,从破坏性键合拉力测试、第一键合点剪切力测试以及通过加热条件下的加速材料扩散试验、键合点切片分析、键合点内部元素扫描等多方面分析,与常规应用的镀镍金基板键合强度进行了相关参数对比,最终确认了长期可靠性满足产品生产要求。此外,对镍钯金电路板金丝键合应用过程中需要注意的相关事项进行了总结与说明。

0 引言

随着微组装工艺的发展,印制电路板上除常规元器件焊接外,也渐渐出现裸芯片的粘接、焊接和键合工艺,以满足对产品的高集成度、小型化的要求。因此,印制电路板的焊盘表面处理工艺也从最基础的“喷锡”演变到“镀金”、“沉金”,但同时,也带来了新的问题。常规采用含锡焊料的焊接工艺中,当焊点中金含量为3%~19%时,会形成AuSn 4合金,导致焊点变脆,存在质量隐患,这种现象称为“金脆”现象。为了避免该问题,在有高可靠性要求的焊接工艺中,或者不采用金焊盘,或者将金焊盘的镀金层厚度进行严格控制。

标准DOD-STD-2000-1B中规定,镀金连接器和元件引线的焊接部位的镀层在1.27~2.54 μm范围内时,应进行搪锡,以避免“金脆”问题 [1] 。电路板焊接应用中,由于大部分元器件均采用贴装形式,焊接部位锡量较少,一般情况下,应将焊盘中的镀金层控制在0.3 μm以下,才可以有效避免“金脆”现象。

印制电路板常规的金焊盘镀覆工艺为化学镀镍金工艺,即在电路板铜焊盘基材上先镀镍再镀金,而该工艺经过高温或长时间储存后,镀层中的镍会向金层渗透、扩散,形成“黑焊盘” [2] 。常规的印制电路板进行微组装工艺时,都是对元器件先焊接,再键合,焊接过程中的高温可造成“黑焊盘”问题,影响后续的键合工艺。为避免“黑焊盘”的问题出现,一般会提高键合区域的焊盘镀金层厚度,印制板厂家一般建议将该区域的镀金层厚度做到1 μm以上。

1 化学镀镍金电路板解决方案

1.1 选择性镀金工艺

为了使印制电路板可以兼容焊接和键合工艺,电路板厂家开始应用选择性镀金工艺。

印制 电路 板焊 盘仍 采用 化学 沉镍 金工 艺(ENIG),为防止“黑焊盘”对键合工艺的影响,且避免“金脆”现象出现,将电路板中的焊接区域、键合区域进行选择性镀金,即镀金厚度不同,焊接区域镀金厚度控制在0.3 μm以下,键合区域镀金厚度控制在1 μm以上。

但是,选择性镀金工艺,需要至少两次镀金,且要对部分焊盘进行“保护”,工艺流程大大增加,导致电路板生产成本提高,某些焊盘较多的电路板在采用选择性镀金工艺后,价格可能是采用普通镀金工艺的几倍甚至十几倍。

1.2 增加“过渡片”工艺

当某一型号的印制电路板需求量很低时,考虑生产成本,也不会对电路板焊盘进行选择性镀金,而是仍采用镀金焊盘,但是镀金层厚度控制在0.3 μm以下,印制电路板上需要进行键合的焊盘处,再焊接或者使用导电胶粘接一种上表面为纯金或者镀厚金的“过渡片”,形成高可靠性的键合区域,再完成芯片对“过渡片”间的键合,从而完成印制电路板上的电气互联。

但是,“过渡片”如果采用金-铜镶嵌材料,即焊接部位为铜、键合部位为金,成本也会很高。若采用铜表面镀金材料,则仍存在“金脆”隐患,而只能采用导电胶粘接工艺,这样,不仅会增加生产工序,导电胶粘接应用在航空、航天产品中可靠性也较差。

为解决以上问题,印制电路板制造行业,开始研发并应用化学镀镍钯金工艺(ENEPIG),该工艺在镍层和金层之间加入薄的一层钯(Pd),阻止镍层向金层扩散,避免了“黑焊盘”问题。这种工艺制备的焊盘,金层很薄,一般厚度在0.3 μm以下,避免了焊接过程中,出现“金脆”现象。同时,由于金层厚度较薄,且镀金工艺简单,生产成本也大大降低。

近年来,化学镀镍钯金工艺在国内具有高可靠要求的产品中应用增多,为验证其键合应用的长期可靠性,进行了相关研究。

2 化学镀镍钯金焊盘的键合强度

2.1 材料及工艺方案

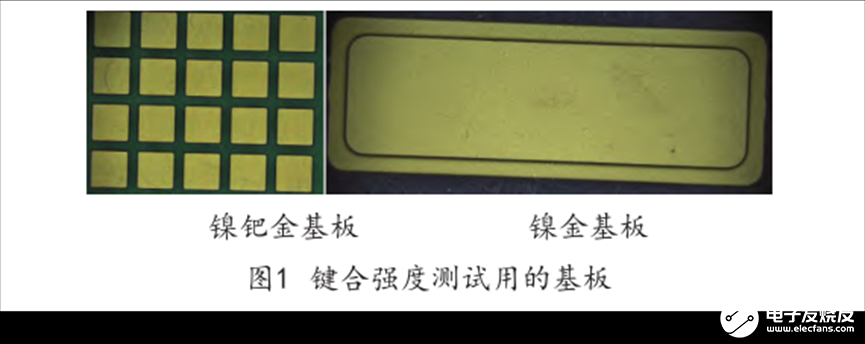

在对化学镀镍钯金焊盘的键合强度测试中,以常见的表面镀镍金基板作为对比,如图1所示。

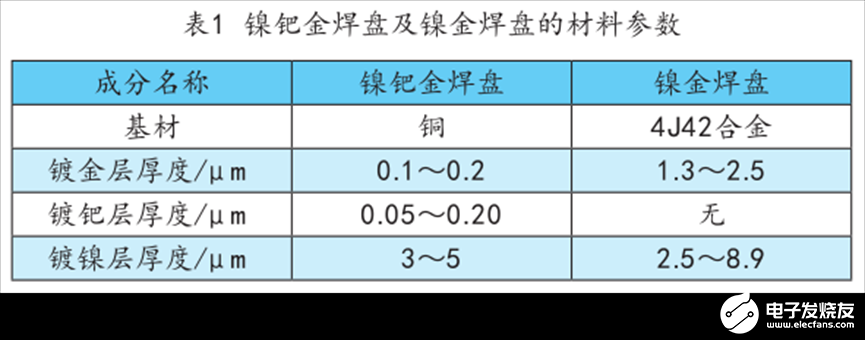

两种材料的详细情况见表1。

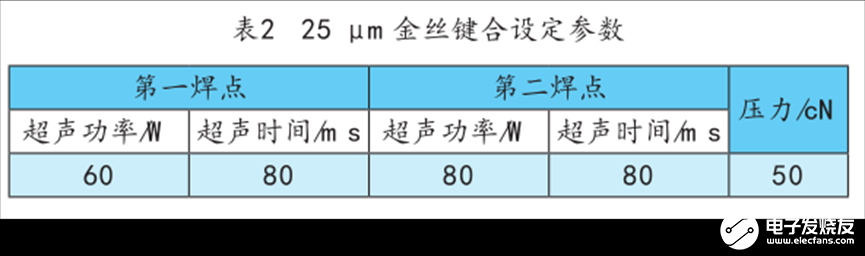

两种基材均使用某型号设备进行全自动键合,在基板表面,采用相同的键合程序,分别键合50根直径为25 μm的金丝,以确保键合丝长度、弧度、键合参数相同,详细键合参数见表2。

2.2 破坏性键合拉力测试

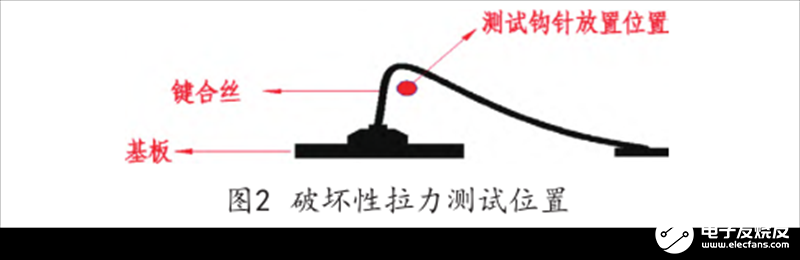

键合完成后,对所有键合丝进行破坏性拉力测试,拉力测试位置均为弧高最高点,如图2所示。

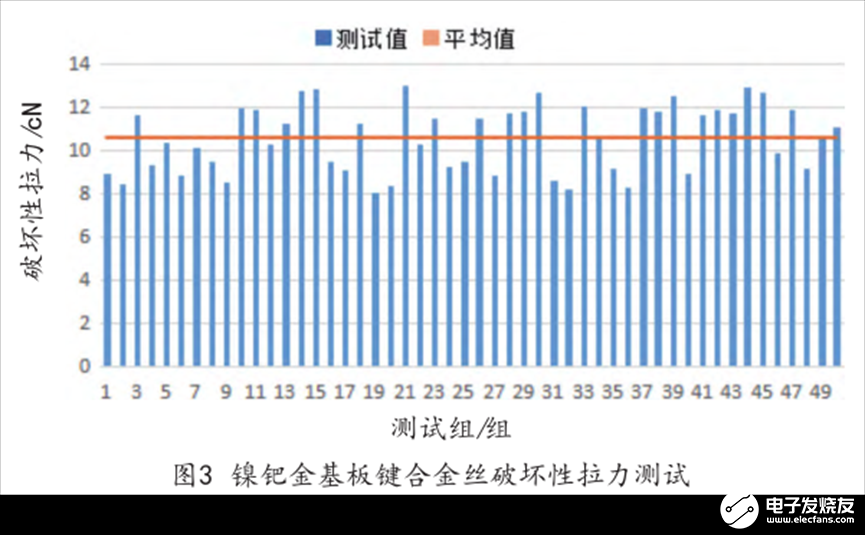

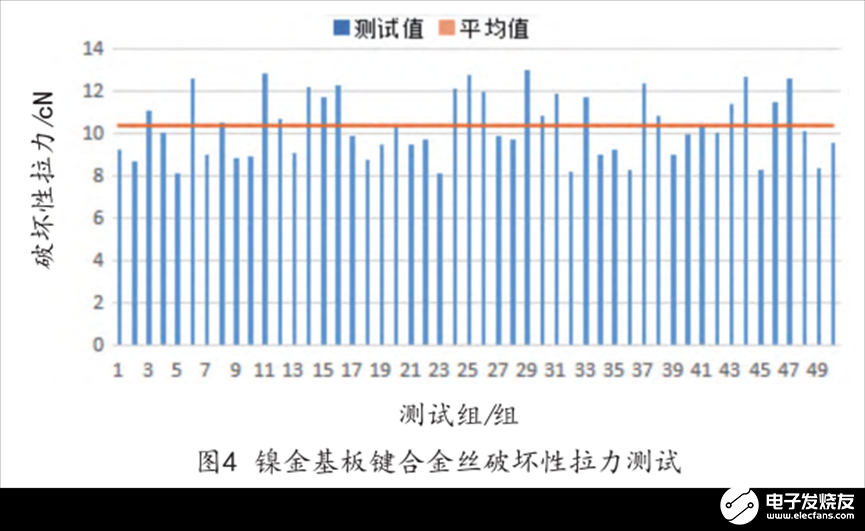

镍钯金基板键合金丝测试后,破坏性拉力均值为10.6 cN,数据分布如图3所示。镍金基板键合金丝测试后,破坏性拉力均值为10.3 cN,数据分布如图4所示。测试过程中均无键合点脱落情况。通过破坏性拉力测试数据对比,两种基板无明显差别。

2.3 键合点剪切力测试

键合点剪切力测试,是将金丝键合的第一键合点进行破坏性剪切力测试,以更加直观地检测其第一键合点的键合强度。

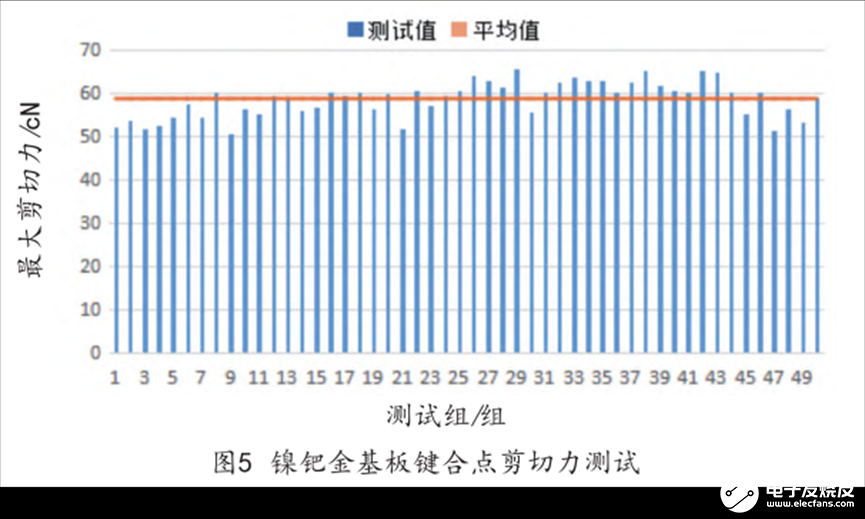

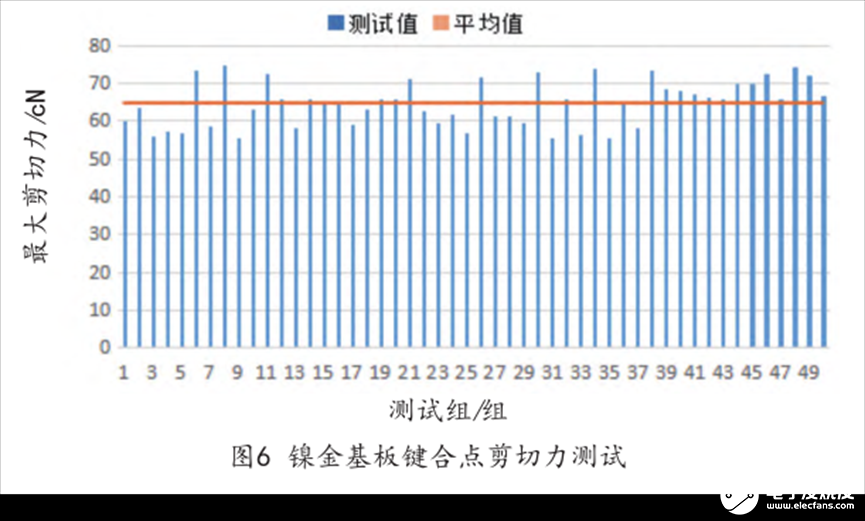

经过测试,镍钯金基板的第一键合点剪切力测试均值为58.8 cN,数据分布如图5所示。而镍金基板的第一键合点剪切力测试均值为64.6 cN,数据分布如图6所示。通过破坏性键合点剪切力测试数据可以看出,在相同键合参数下,镍金基板的第一键合点强度要高于镍钯金基板的。

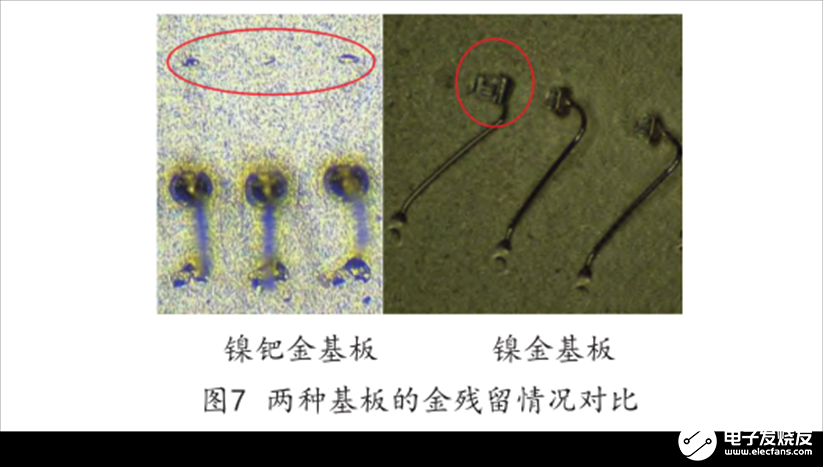

2.4 键合点剪切力测试后金残留情况

进行破坏性键合点剪切力测试后,键合点的金残留情况也可作为键合强度是否可靠的判断依据。镍钯金基板进行键合点剪切力测试后,键合点金残留情况明显少于镍金基板的,如图7所示。

3 化学镀镍钯金焊盘的键合可靠性

通过拉力、键合点剪切力测试分析,产品基本可以满足使用要求,但是键合点剪切力测试后的金残留情况与常规镍金基板不同,因此,继续进行了相关可靠性研究。

3.1 试验条件(烘焙温度300 ℃、烘焙时间1 h)

在金丝键合工艺应用过程中,为验证键合材料与基板金属间的扩散效应,经常采用在温度300 ℃下烘焙1 h的试验方式,来加快材料间的扩散,进而验证长期应用可靠性。

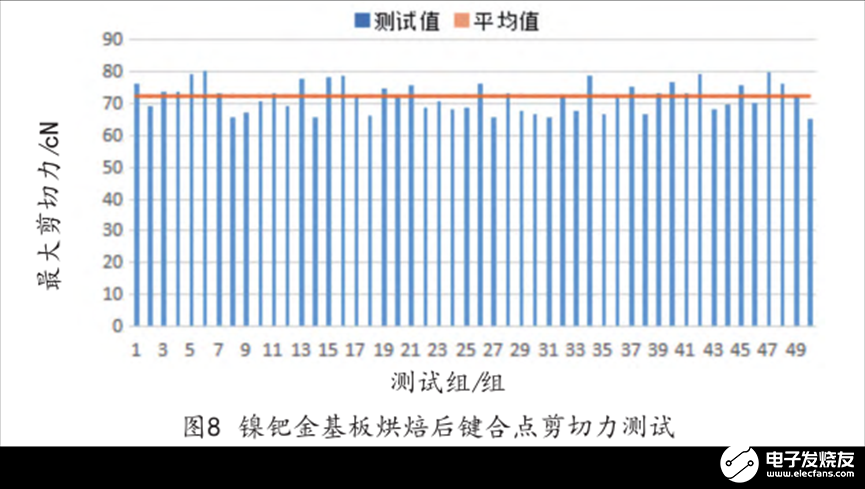

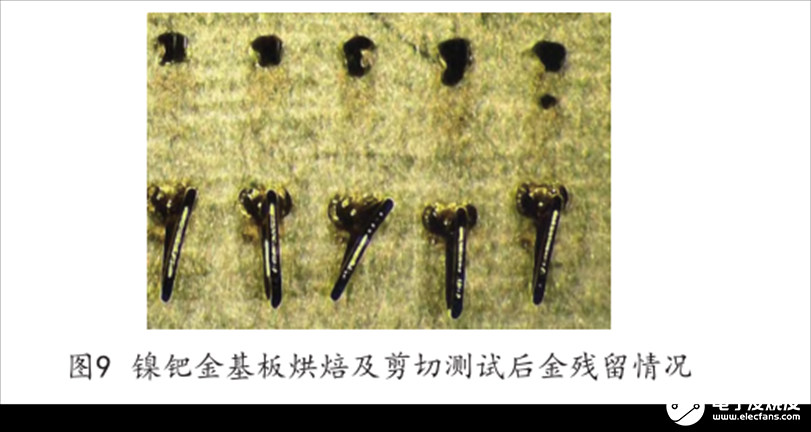

本次将键合后的镍钯金电路板进行了300 ℃下1 h的烘焙,烘焙后,对第一键合点进行了破坏性剪切力测试。其键合点并未出现脱落情况。其剪切力测试均值为72.1 cN,对比烘焙前,有明显提升,数据分布如图8所示。此外,其第一键合点进行剪切力测试后,金残留也逐渐变多,如图9所示。

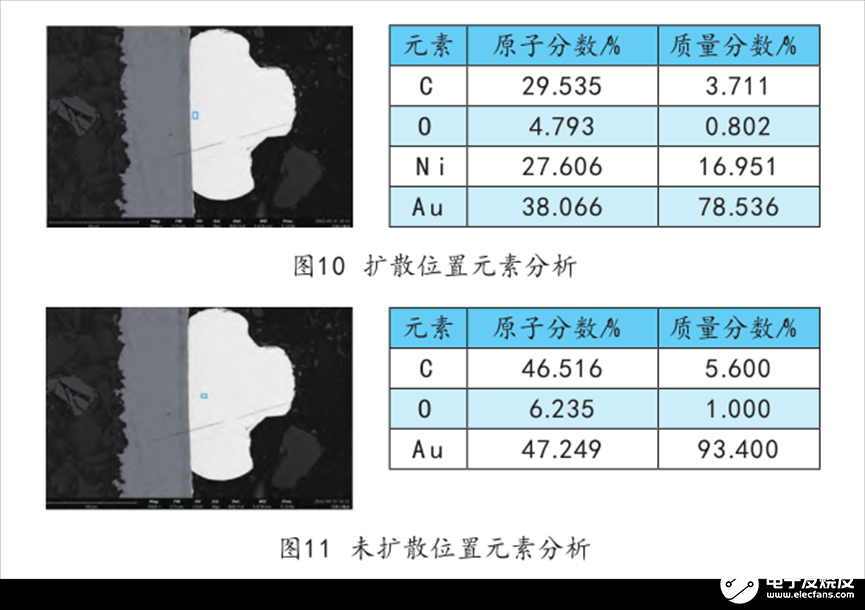

验证其键合强度增强是否为键合点与材料间的扩散导致,对键合点进行了切片分析,证实了其焊盘镀层中的镍元素(Ni)确实扩散到了键合点内部,如图10和图11所示。

3.2 试验条件(烘焙温度300 ℃、烘焙时间8 h)

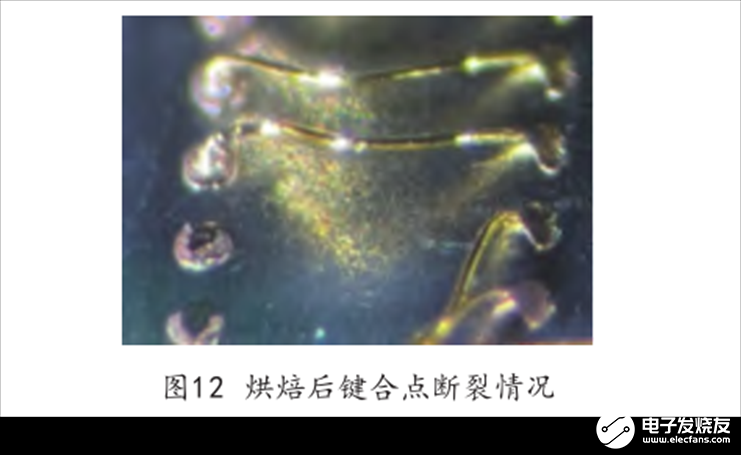

为验证该扩散是否持续进行,再次试制样品,并进行了温度300 ℃下8 h的烘焙。烘焙后,其电路基板部分已经变形,但是铜镀镍钯金焊盘部分得以保留,对其第一键合点再次进行剪切力测试,其键合点大部分已无法去除,键合点仅从颈缩处断裂,因此,第一键合点的剪切力测试数据已无意义,如图12所示。

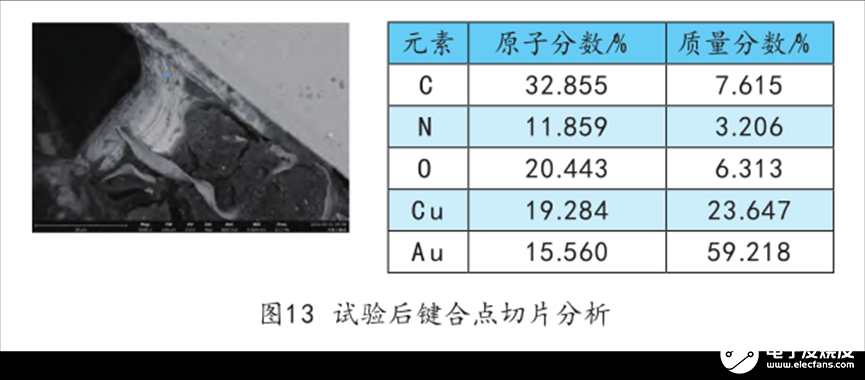

对该键合点再次进行切片分析,Ni元素扩散位置更加深入,且焊盘底层的Cu元素也开始扩散,如图13所示。

3.3 小结

通过以上验证,可知镍钯金基板长期应用过程中,Ni元素仍然存在扩散问题,只是生产过程中,镀层中的Pd成分可以有效阻止Ni元素短时间内扩散,以保证焊接后,键合工艺的稳定进行。

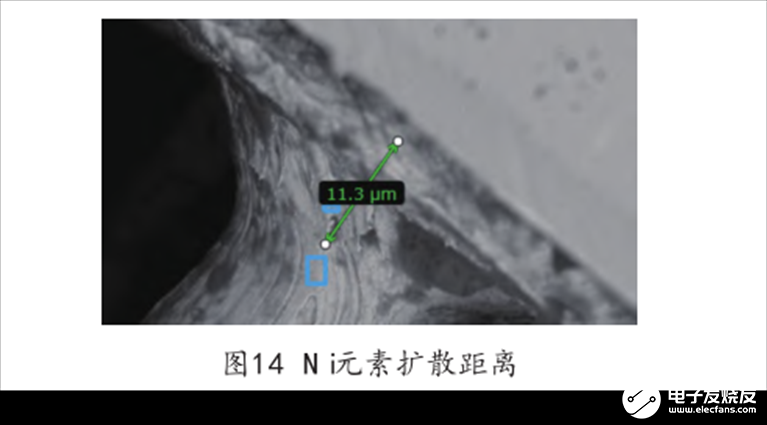

测量烘焙300 ℃/8 h后的Ni元素的扩散距离已大于10 μm(如图14所示)。因此,通过该试验也可以确定,常规的镍金基板的镀金层厚度大于1 μm仍然无法阻止长时间的Ni元素扩散。

常规镍金基板在微组装领域已应用多年,无可靠性隐患,因此,可以推断,镍钯金基板的镍层扩散问题不会影响长期应用可靠性。且其经过扩散后键合强度增加,无多层金属分离问题,证明其长期应用可靠性能够满足高可靠性产品要求。

4 产品应用注意事项

4.1 避免表面划伤

镍钯金焊盘在使用过程中,由于其表面金层、钯层厚度均较薄,应注意避免表面划伤,否则很容易破坏金、钯镀层,导致键合强度异常。

4.2 避免沾污

键合用的基板在少量沾污情况下,采用等离子清洗工艺,即可去除表面污染,该方式同样适用于镍钯金基板。但是,若出现较为严重的污染时,常规的镍金基板表面,可以采用打磨方式去除顽固污物,而镍钯金焊盘的打磨方式不易控制,无法确保镀层不被破坏。

4.3 确保表面粗糙度

该问题主要对于印制电路板的制造商而言,因其镀金层较薄,实际键合过程中,表面金层的形变量很小,因此,相对于镀厚金的镍金基板,镍钯金基板对表面粗糙度要求更高,有文献表明,表面粗糙度至少要在 R a 0.6以下 [3] 。

5 结论

通过以上验证,可知采用化学镀镍钯金工艺的印制电路板焊盘可以满足金丝键合的可靠性要求,但是,在实际生产中相对镍金基板,应用镍钯金基板需要对其他生产工艺进行更加良好的控制,避免对镀金、钯层的破坏。

审核编辑 黄宇

-

基于推拉力测试机的化学镀镍钯金电路板金丝键合可靠性验证2025-04-29 1412

-

探秘化学镀镍金:提升电子元件可靠性的秘诀2025-03-05 1276

-

pcb表面处理 什么是化学镀镍2024-01-17 3085

-

金丝键合第二焊点补球工艺的可靠性分析2023-10-26 4592

-

微波组件细间距金丝键合工艺的可靠性分析2023-05-16 3239

-

《炬丰科技-半导体工艺》用于半导体封装基板的化学镀 Ni-P/Pd/Au2021-07-09 4039

-

正面金属化工艺高CP值选择-化学镀2021-06-26 2423

-

不合格的PCB化学镀镍层怎样处置2019-08-22 1224

-

挠性电路板化学镍钯金工艺技术研究2017-01-22 1061

-

探讨印制电路板用化学镀镍金工艺2016-06-15 1088

-

印制电路板用化学镀镍金工艺探讨-悌末源2015-04-10 3140

-

Pcb化学镀镍/金工艺介绍2009-10-17 1419

-

[分享]电路板可靠性分析2009-05-18 9332

-

印制电路板用化学镀镍金工艺探讨(一)2006-04-16 1268

全部0条评论

快来发表一下你的评论吧 !